基于FPGA的多路安全连接抗重放攻击设计实现.pptx

快乐****蜜蜂

亲,该文档总共27页,到这已经超出免费预览范围,如果喜欢就直接下载吧~

相关资料

基于FPGA的多路安全连接抗重放攻击设计实现.pptx

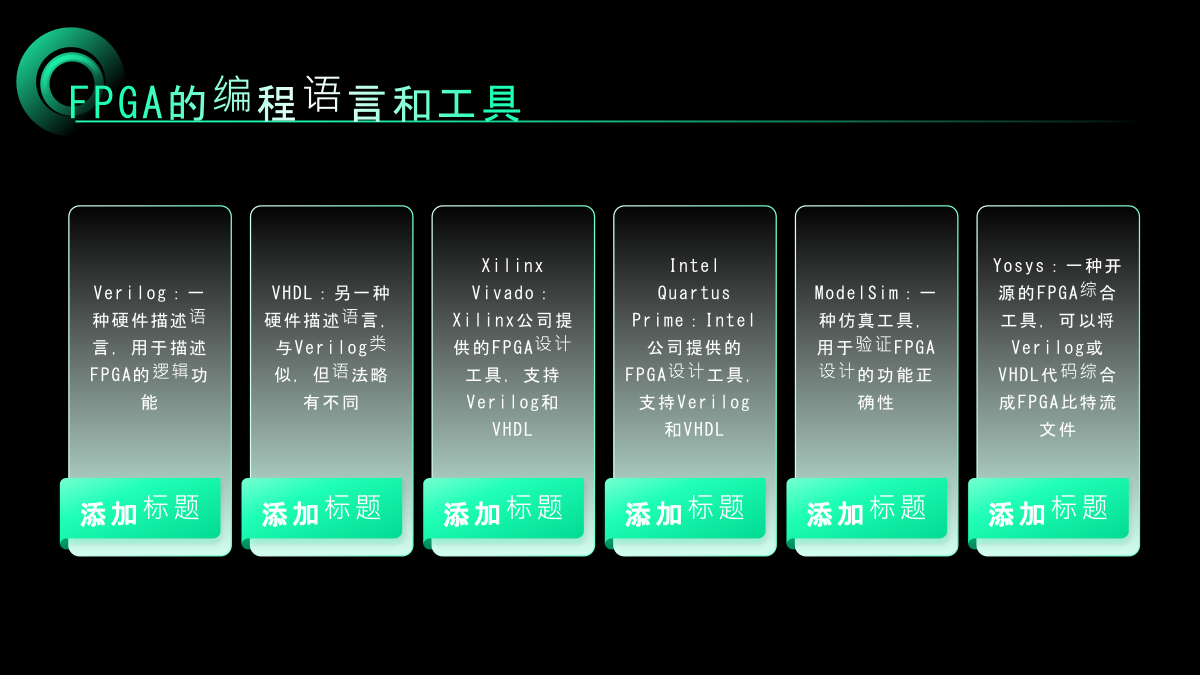

汇报人:CONTENTSPARTONEPARTTWOFPGA的特性FPGA在安全连接中的作用FPGA的编程语言和工具PARTTHREE多路安全连接的概念和重要性基于FPGA的多路安全连接架构多路安全连接的关键技术PARTFOUR重放攻击的原理和危害抗重放攻击的常用方法基于FPGA的抗重放攻击实现PARTFIVE设计思路和流程FPGA编程和仿真验证测试和性能评估PARTSIX安全性评估标准基于FPGA的多路安全连接抗重放攻击的安全性分析与其他方案的比较和优势分析PARTSEVEN基于FPGA的多路安全连接抗

基于FPGA实现的多路PWM设计.docx

基于FPGA实现的多路PWM设计多路PWM设计的概述PWM(脉宽调制)是在控制器和执行器之间的传输信号,在工业控制系统中普遍使用。PWM信号通过改变每个周期中高电平和低电平持续时间的比例来调节输出电压或电流。FPGA(现场可编程门阵列)是一种数字电路。由于其高速处理和可重构性,FPGA成为了很多系统中的首选,而且能够减少集成电路的复杂度。多路PWM设计结合了这两种技术,使用FPGA处理多路PWM信号,并且具有卓越的自适应性和灵活性。FPGA的优势FPGA最显著的优势之一是其可重构性。FPGA的设计可以随着

基于双重验证的抗重放攻击方案.docx

基于双重验证的抗重放攻击方案引言随着互联网的快速发展,网络攻击者也变得越来越有技巧性和破坏性。网络攻击方式越来越多样,其中比较常见的攻击方式包括重放攻击、中间人攻击、跨站点脚本攻击等。在这些攻击方式中,重放攻击是一种比较常见的攻击方式。重放攻击可以对系统造成严重的威胁,例如篡改用户信息、非法获取用户数据等。因此,如何有效地防范重放攻击成为了构建安全系统的一个重要问题。本文旨在探讨基于双重验证的抗重放攻击方案。双重验证可以有效地防范重放攻击并确保用户数据的安全性。首先,本文将对重放攻击进行详细介绍,并阐述重

基于FPGA的多路高速串口设计与实现.docx

基于FPGA的多路高速串口设计与实现基于FPGA的多路高速串口设计与实现摘要:本文针对现实生活中常见的多路串口同步传输问题,在FPGA平台上设计了一种多路高速串口方案。该方案基于FPGA平台,结合串口协议标准,采用FIFO缓存技术、串口发送接收缓存控制、时序控制等方式进行系统设计。关键词:FPGA、多路串口、FIFO缓存技术、串口发送接收缓存控制、时序控制引言:随着技术的不断发展和应用领域的不断拓宽,现今市场上常见的嵌入式应用,往往需要采用多路高速串口传输数据。例如,一些多功能测试仪器、PLC控制器和通信

抗重放攻击认证协议的设计原则和方法研究.docx

抗重放攻击认证协议的设计原则和方法研究随着网络技术的发展,网络安全问题也变得愈发突出,其中重放攻击是网络安全中常见的攻击方式之一。为了解决重放攻击问题,抗重放攻击认证协议的设计也逐渐成为研究热点。本文将从抗重放攻击认证协议设计的原则和方法两方面进行分析和探讨。一、抗重放攻击认证协议设计的原则1.防止重放攻击重放攻击是指攻击者能够通过录制认证信息并再次发送来获得未授权的访问或造成混乱。因此,防止重放攻击成为抗重放攻击认证协议设计的首要原则。2.保证数据完整性数据完整性是指数据在传输过程中没有被篡改。为保证数