数字电路 电工与电子技术教学.pptx

骑着****猪猪

亲,该文档总共109页,到这已经超出免费预览范围,如果喜欢就直接下载吧~

相关资料

数字电路 电工与电子技术教学.pptx

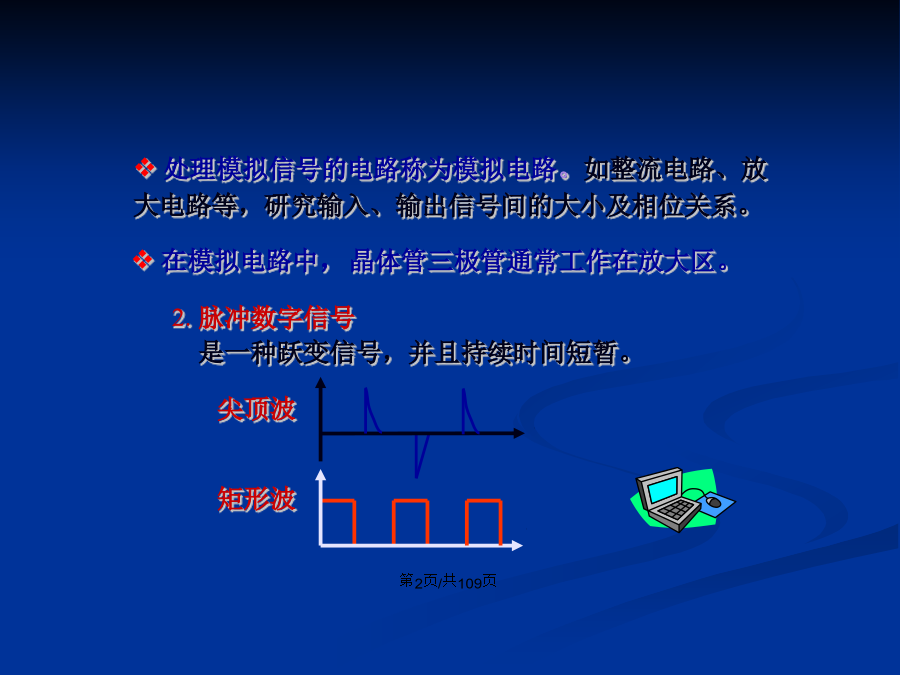

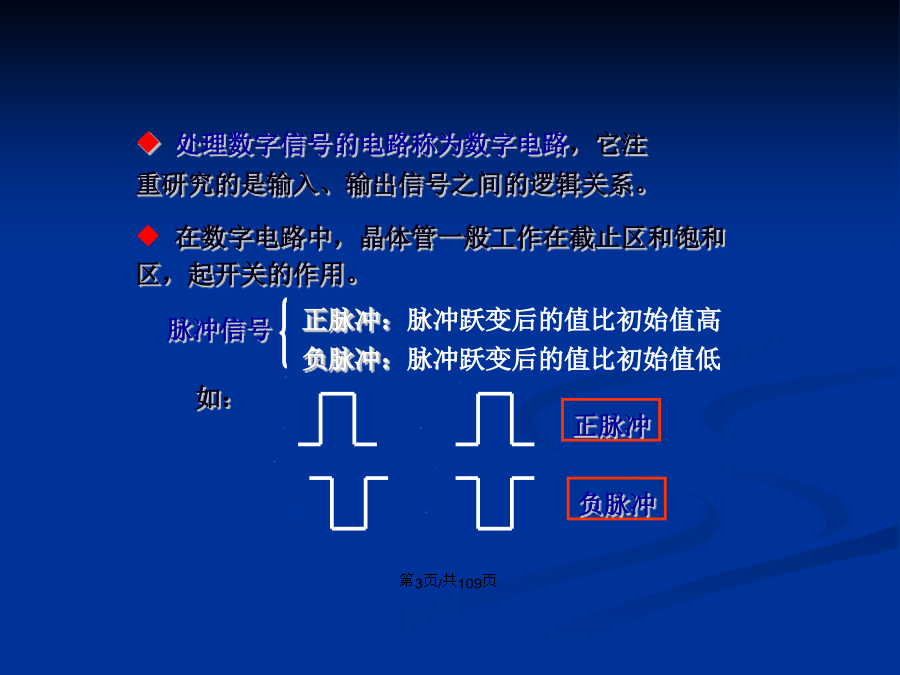

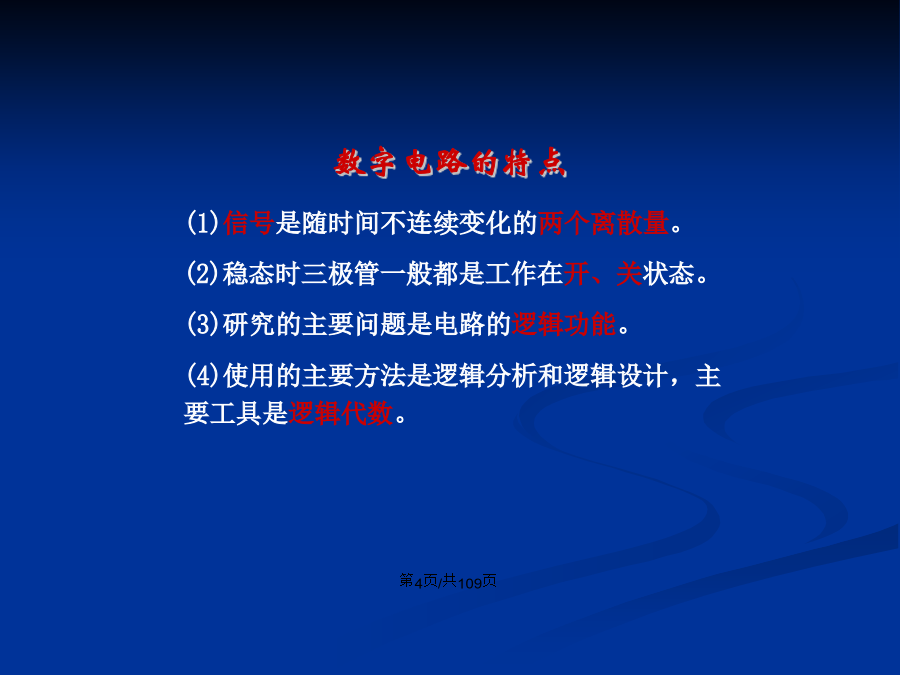

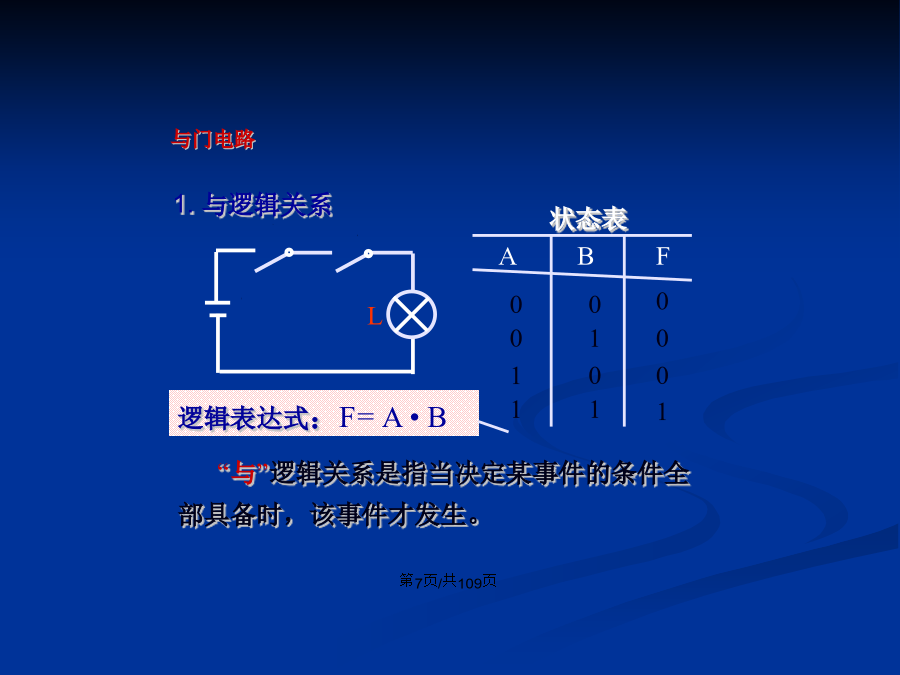

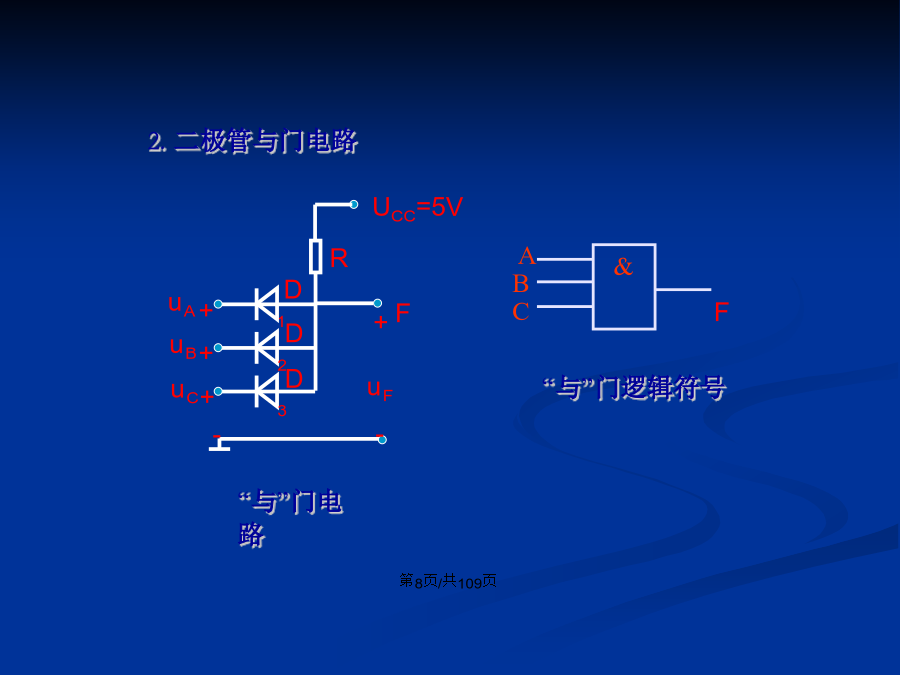

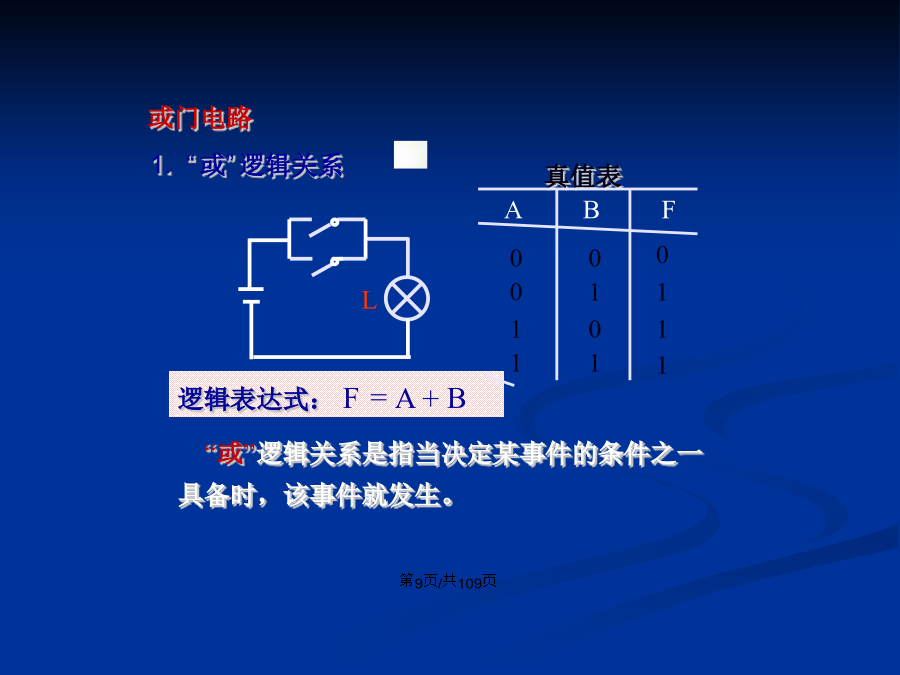

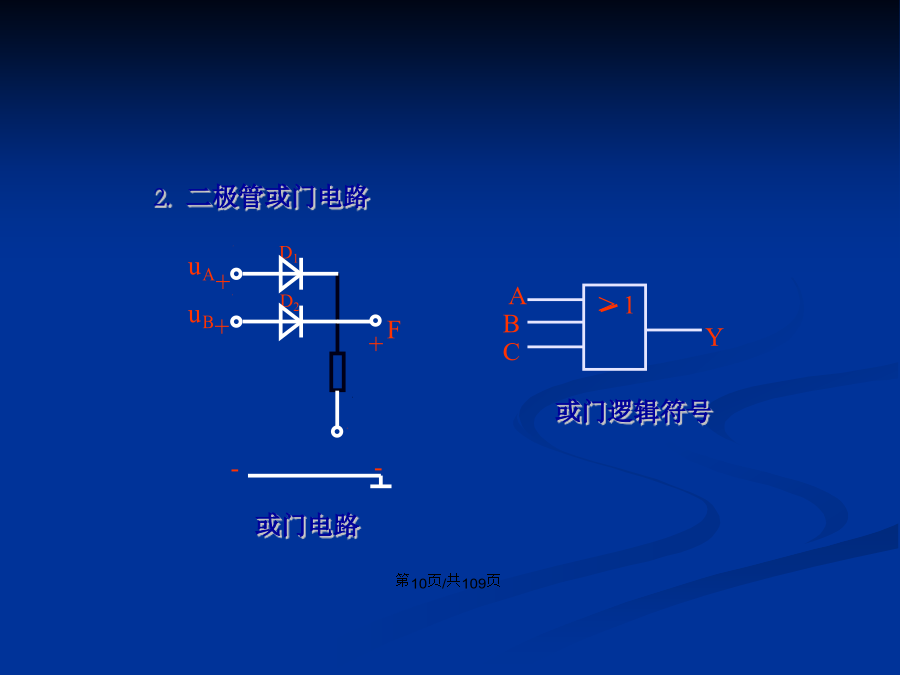

会计学处理模拟信号的电路称为模拟电路。如整流电路、放大电路等,研究输入、输出信号间的大小及相位关系。处理数字信号的电路称为数字电路,它注重研究的是输入、输出信号之间的逻辑关系。数字电路的特点电平的高低一般用“1”和“0”两种状态区别,若规定高电平为“1”,低电平为“0”则称为正逻辑。反之则称为负逻辑。若无特殊说明,均采用正逻辑。5.2分立元件门电路逻辑表达式:F=A•B2.二极管与门电路B非门电路2.非门电路逻辑代数(1)基本律(3)结合律(5)吸收律(6)德摩根定理(反演律)对偶关系:将某逻辑表达式中的

电工电子技术基础之数字电路.docx

第一节数字电路概述一、数字信号与数字电路模拟信号:在时间上和数值上连续的信号。数字信号:在时间上和数值上不连续的(即离散的)信号。uu模拟信号波形数字信号波形tt对模拟信号进行传输、处理的电子线路称为模拟电路。对数字信号进行传输、处理的电子线路称为数字电路。二、数字电路的特点(1)工作信号是二进制的数字信号在时间上和数值上是离散的(不连续)反映在电路上就是低电平和高电平两种状态(即0和1两个逻辑值)。(2)在数字电路中研究的主要问题是电路的逻辑功能即输入信号的状态和输出信号的状态之间的逻辑关系

电工电子技术基础之数字电路.docx

第页第一节数字电路概述一、数字信号与数字电路模拟信号:在时间上和数值上连续的信号。数字信号:在时间上和数值上不连续的(即离散的)信号。uu模拟信号波形数字信号波形tt对模拟信号进行传输、处理的电子线路称为模拟电路。对数字信号进行传输、处理的电子线路称为数字电路。二、数字电路的特点(1)工作信号是二进制的数字信号,在时间上和数值上是离散的(不连续),反映在电路上就是低电平和高电平两种状态(即0和1两个逻辑值)。(2)在数字电路中,研究的主要问题是电路的逻辑功能,即输入信号的状态和输出信号的

电工电子技术基础之数字电路.docx

第页第一节数字电路概述一、数字信号与数字电路模拟信号:在时间上和数值上连续的信号。数字信号:在时间上和数值上不连续的(即离散的)信号。uu模拟信号波形数字信号波形tt对模拟信号进行传输、处理的电子线路称为模拟电路。对数字信号进行传输、处理的电子线路称为数字电路。二、数字电路的特点(1)工作信号是二进制的数字信号,在时间上和数值上是离散的(不连续),反映在电路上就是低电平和高电平两种状态(即0和1两个逻辑值)。(2)在数字电路中,研究的主要问题是电路的逻辑功能,即输入信号的状态和输出信号的状

中职-电工电子技术第十章-数字电路.ppt

10.1概述10.1概述10.1概述10.1概述10.1概述10.1概述10.1概述10.1概述10.1概述10.1概述10.1概述10.1概述10.1概述10.2逻辑门电路10.2逻辑门电路10.2逻辑门电路10.2逻辑门电路10.2逻辑门电路10.2逻辑门电路10.2逻辑门电路10.2逻辑门电路10.2逻辑门电路10.2逻辑门电路10.2逻辑门电路10.2逻辑门电路10.2逻辑门电路10.2逻辑门电路10.2逻辑门电路10.2逻辑门电路10.2逻辑门电路10.2逻辑门电路10.3触发器10.3触发器1