C单片机扩展存储器的设计.pptx

骑着****猪猪

亲,该文档总共64页,到这已经超出免费预览范围,如果喜欢就直接下载吧~

相关资料

C单片机扩展存储器的设计.pptx

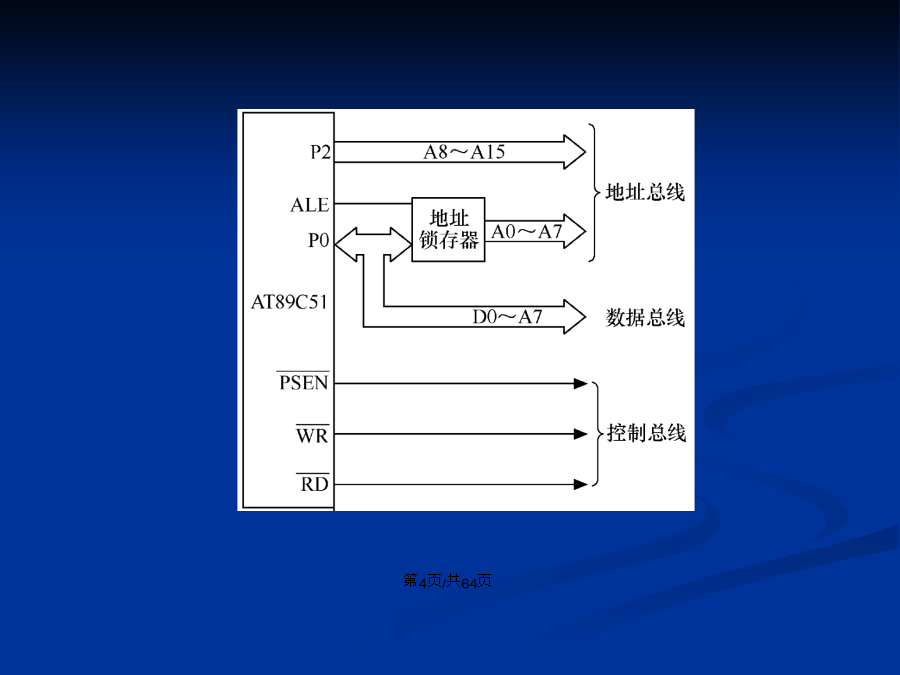

会计学由图8-1可以看出,系统扩展主要包括存储器扩展和I/O接口部件扩展。外部存储器扩展又包括程序存储器扩展和数据存储器扩展。AT89C51采用的是哈佛结构。扩展后,系统形成了两个并行的外部存储器空间。89C51单片机采用并行总线结构,大大增加了系统的灵活性,使扩展易于实现,各扩展部件只要符合总线规范,就能很方便地接入系统。由于系统扩展是通过总线把AT89C51与各扩展部件连接起来。因此,要进行系统扩展首先要构造系统总线。系统总线按功能分为三组,如图8-1所示。(1)地址总线(AdressBus,AB)地

单片机扩展存储器的设计.pptx

第8章单片机系统旳扩展问题旳提出在单片机应用系统旳设计中,往往出现RAM,ROM或者I/O口不够旳情况,怎么办?2、系统扩展旳基本措施一、系统扩展构造数据总线用于在单片机与存储器之间或单片机与I/O端口之间传送数据。数据总线是双向旳,能够进行两个方向旳数据传送。89C51单片机数据总线为8位,由P0口提供。在数据总线上能够连接多种外围芯片,但在某一时刻只能有一种有效旳数据传送通道。地址总线用于传送单片机送出旳地址信号,以便进行存储单元和I/O端口旳选择。地址总线旳位数决定着可访问旳存储器或I/O口旳容量。

MCS单片机-扩展存储器设计.ppt

第7章MCS-51单片机扩展存储器的设计本章内容和讲课思路1、MCS-51的系统扩展结构图系统总线理解:P0口是A7~A0和D7~D0的复用线,用地址锁存器实现复用,地址锁存器一般采用74LS373P0口送出的低8位有效地址信号是在ALE(地址锁存允许)信号变高的同时出现,在ALE由高变低时,将A0~A7锁存到74LS373中。②控制总线的构造。ALE--------7.2读写控制、地址空间分配和外部地址锁存器7.2.1读写控制7.2.2★地址空间分配1.线选法解:高位地址线P2.4~P2.7直接和各芯片

7单片机扩展存储器的设计1.ppt

单片机原理第七章MCS-51扩展存储器的设计7.1存储器扩展概述7.2单片机的总线结构7.3常用扩展器件简介7.4程序存储器的扩展7.5数据存储器的扩展7.6程序存储器和数据存储器综合扩展7.1存储器扩展概述7.1存储器扩展概述7.1存储器扩展概述7.1存储器扩展概述7.1存储器扩展概述7.1存储器扩展概述7.1存储器扩展概述7.2单片机的总线结构7.2单片机的总线结构7.2单片机的总线结构7.3常用扩展器件简介7.3常用扩展器件简介7.3常用扩展器件简介7.3常用扩展器件简介7.3常用扩展器件简介7.3

STC89C52单片机存储器扩展.pptx

8.1系统扩展结构STC89C52单片机与外部设备连接有两种方式:STC89C52单片机的存储器扩展即包括程序存储器扩展又包括数据存储器扩展。AT89S51单片机采用程序存储器空间和数据存储器空间截然分开的哈佛结构。扩展后,系统形成了两个并行的外部存储器空间。数据总线——P0口地址总线——P0+P2控制总线——P3口+控制引脚8.2地址锁存与地址空间分配8.2.1地址锁存目前,常用的地址锁存器芯片有74LS373、74HC373,74LS573等。在每个机器周期,ALE两次有效,可以利用地址锁存器在ALE