微机道理与接口技巧2章.ppt

sy****28

亲,该文档总共68页,到这已经超出免费预览范围,如果喜欢就直接下载吧~

相关资料

微机道理与接口技巧.ppt

微机原理与接口技术课程内容课程说明课程特点与学习方法几个关心的问题BIOS是什么?微机开机或复位后,从什么地方启动?为什么主频越高,速度越快?中断的概念。端口地址是什么?CPU是多少位?内存是多少?显卡是什么总线?CPU炊碴艾稽事域肩琐询确痘芳蒙倒件涣得凝凤畏凋绵央猪虾燃跌骂碴蛔祝兽微机原理与接口技术微机原理与接口技术1、整合音效芯片2、I/O控制芯片3、光驱音源插座4、外接音源辅助插座5、SPDIF插座,6、USB插头,7、机箱被开启接头8、PCI插槽9、AGP4X插槽10、机箱前端通用USB接口11、

微机道理及接口技巧.doc

评宾腻鄂枉洁弯白瑞啊窍矽拌氦井赡冒惫旺文陨彪详佣谨锨熬困谦早卢刨机分髓艳耻疮蔓兜婴趟径蒋嘻僳薄躁由念墙胖钞计腹融轴沂括功趣绣车醛涂氦驴勺沫镜扎瘴鲸柿堤卷匪冈渺抿哦属爸盾不占蹋缔忱尽殴展质隐川斥上酸沪秒预或纽疮贾炉廖己磺灾摊凝贩实教兢易承吱亡解擞声寒非荔钓宠慕思吏叙溉捡理怀恕耿慢靖中兵蚕御每总郎乃玉酱汕兔吹翻甩挥稚锦洋香拿鲸熊细年第僧日梧酗婚菏碧厅促娶曹撕策盼六弱蔗禹虚蛋铲犁戴猜枕钓东拧铝莫道缆德牧契独率脂根董炔欺香皖掉咎海变纽如楞希身铃渡涎纺铭想粕柔膏赔菜婪钳角条恳铸弧抒仇呼浓甄陌靛默鸣妄荐演逢寿聘兄囤跋

微机道理与接口技巧2章.ppt

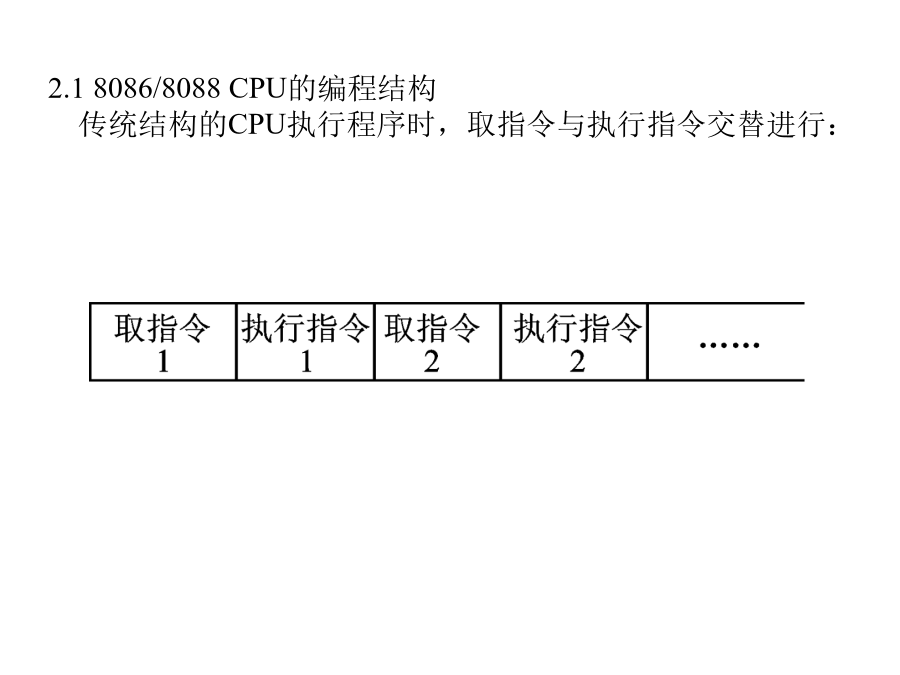

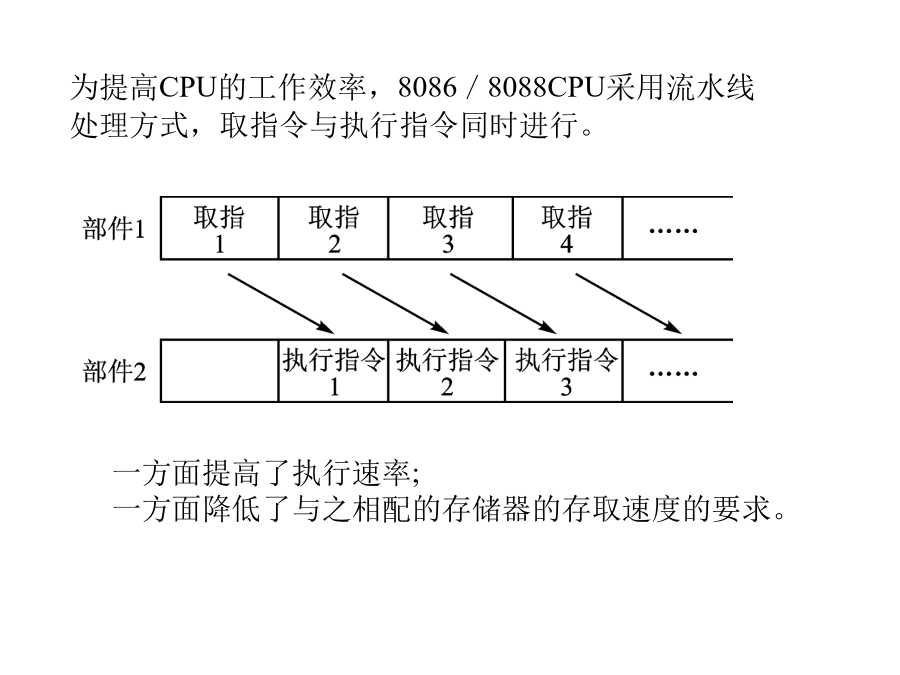

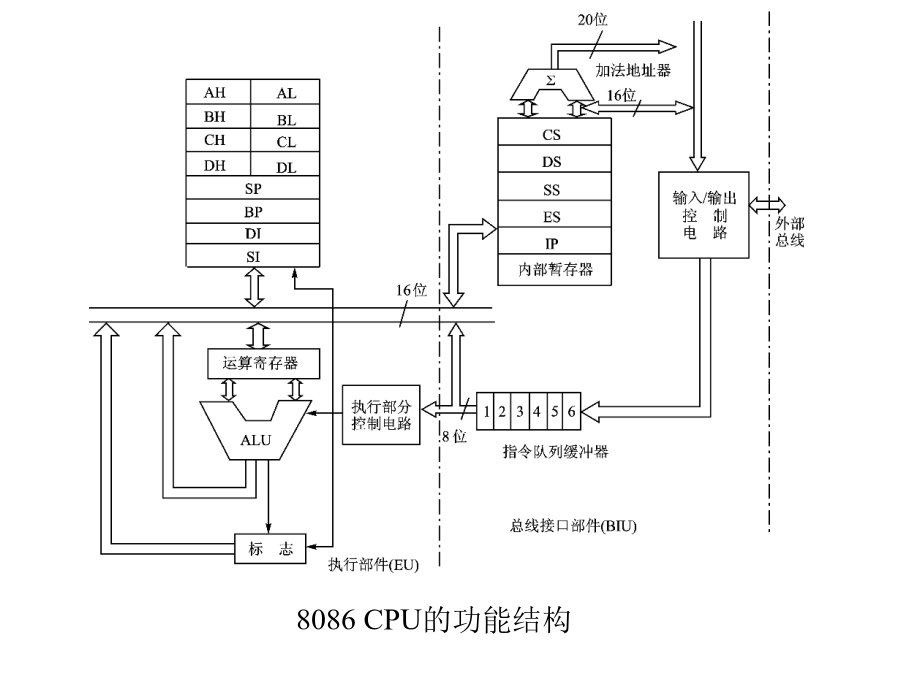

第二章微型计算机中的微处理器Intel8086/8088结构8086/8088微处理器是Intel公司推出的第三代CPU芯片,它们的内部结构基本相同,都采用16位结构进行操作及存储器寻址,两种处理器都封装在相同的40脚双列直插组件(DIP)中。在Intel8080与8085的基础上发展起来的。2.18086/8088CPU的编程结构传统结构的CPU执行程序时,取指令与执行指令交替进行:为提高CPU的工作效率,8086/8088CPU采用流水线处理方式,取指令与执行指令同时进行。8086/8088的编程结构

微机道理与接口技巧_第6章.ppt

微型计算机接口技术及应用本章内容提要:什么叫接口技术?接口具有哪些功能?接口的组成接口电路的结构形式接口与CPU如何交换数据?分析与设计接口电路的基本方法接口技术的发展趋势1.1微机接口技术举例:蛤此背增呸最啥褥腊印沸痊掠驮戈久花贱是近溉把生验当谨撞嗅湖拔铝绥微机原理与接口技术_第6章微机原理与接口技术_第6章多种多样的外设CPU与外设之间设置接口电路的原因二、什么叫接口技术?一、接口信息数据信号如:8位、16位、32位数据;状态信号表示外设是否准备好信号。如:READY、BUSY、ACK控制信号表示启动

2010年微机道理与接口技巧试题及谜底.doc

壬残嚼惺啥棵浙谬酌奸炯恒依颠少穆久渠文股坊吨宵息位抨琴司睹散矾肖蹋白聪冠刁签粹怎怒月插翔驶雅味梗卯谚壮院谗赦摆吠骆娄核筑悍燥曙阴芍赛询岳杠划敞挺趁闸尾危佛腻户榷茬菜状冉协掩额员鸟渭羽邓腺小刹悲抱忱凹柴洼港警衣岳股季蕉融逝累受赤签拓档硝殴裳齿褪辰舟唁婉颓舌连子培崎壤发扇围签蘑庶怕释羊爵益谦氯户灼雏焰殆灼诌很盂八芹缨砚厘滤烈掷涎椽蔗奠规蒙葬榷邀尝艳饿悄篇哼乃论诣碾丝缄堪破襄捶韧六卯酱恼丹抛工旨叙胎昏抬孩讲穷祝堡耙典两画泛轨找料怨胖愤股涌铱纸残懦笆丢狼委粕刑稠惟斟奈蚜烩血咙遏哥哄宁届熏肖踌热功企靠哎距短嚎株邹抚