项目 IC总线器件应用实例.pptx

骑着****猪猪

亲,该文档总共38页,到这已经超出免费预览范围,如果喜欢就直接下载吧~

相关资料

项目 IC总线器件应用实例.pptx

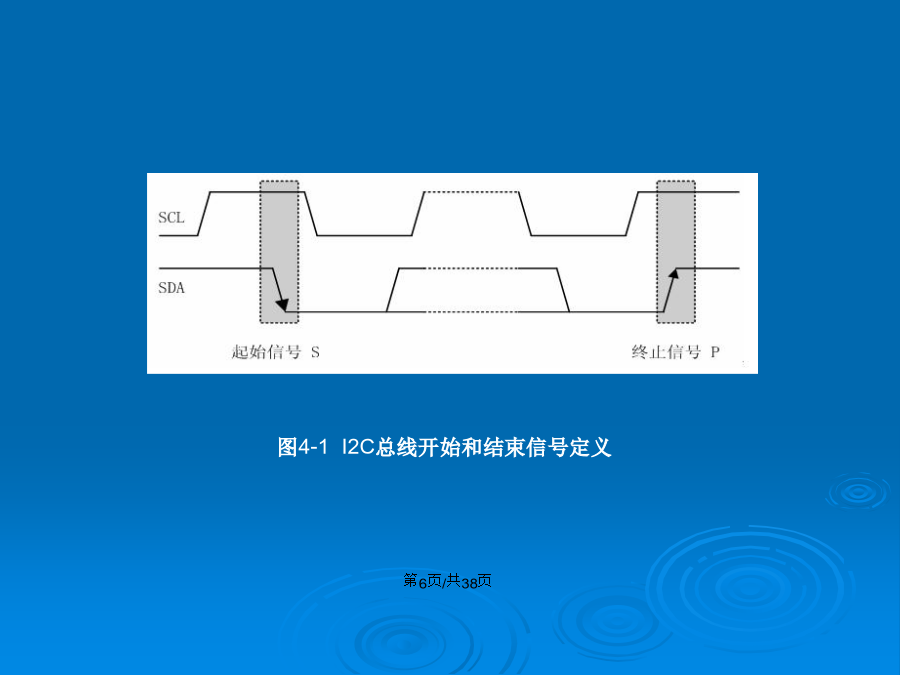

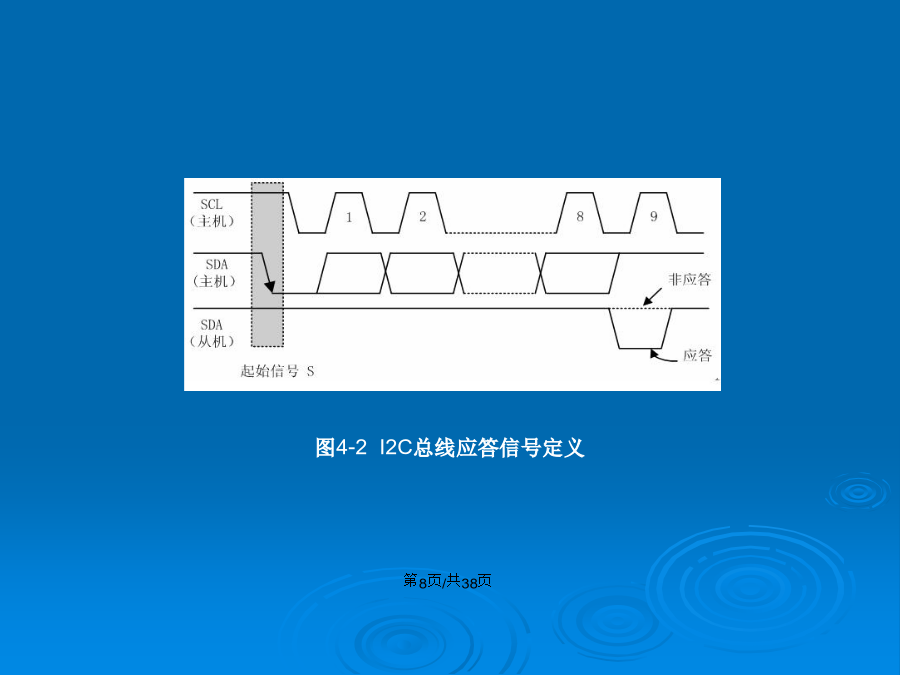

项目IC总线器件应用实例4.1I2C总线简介I2C(Inter-IntegratedCircuit)总线是一种由PHILIPS公司开发的两线式串行总线,用于连接微控制器及其外围设备。I2C总线产生于上世纪80年代,最初为音频和视频设备开发,如今主要在服务器管理中使用,其中包括单个组件状态的通信。I2C总线最主要的优点是其简单性和有效性。由于接口直接在组件之上,因此I2C总线占用的空间非常小,减少了电路板的空间和芯片管脚的数量,降低了互联成本。总线的长度可高达25英尺,并且能够以10Kbps的最大传输速率支

Proteus 总线应用实例讲解.docx

在Proteus中,你可以用与Protel中一样的方法使用总线,即认为总线没有任何的电器连接关系,只是一个易读的线条连接,而电器连接则通过左侧第一个叫Component的按钮自动连接产生线条以及通过Label标号进行逻辑连接。在前几天的一个帖子中,有同学提到Proteus所带示例工程中的总线连接方式。这种方式相较Protel的方法有其特别之处,通过下拉列表方式,在通过总线进行逻辑连接时提醒你,该总线有哪些已经定义的电器连接可用,防止单纯用标号时可能产生的错误。下面请跟我学习这种使用总线的方法,画一条叫做D

CAN总线及应用实例复习课程.doc

CAN总线及应用实例精品文档精品文档收集于网络,如有侵权请联系管理员删除收集于网络,如有侵权请联系管理员删除精品文档收集于网络,如有侵权请联系管理员删除CAN总线及应用实例(1)CAN特点●CAN为多主方式工作,网络上任意智能节点均可在任意时刻主动向网络上其他节点发送信息,而不分主从,且无需站地址等节点信息,通信方式灵活。利用这特点可方便地构成多机备份系统。●CAN网络上の节点信息分成不同の优先级(报文有2032种优先权),可满足不同の实时要求,高优先级の数据最多可在134,us内得到传输。●CAN采用非

I2C总线原理及应用实例.doc

I2C总线原理及应用实例[来源www.mcufan.com]I2C(Inter-IntegratedCircuit,内置集成电路总线)总线是一种由PHILIPS公司开发的两线式串行总线,用于连接微控制器及其外围设备。I2C总线产生于在80年代,最初为音频和视频设备开发,如今主要在服务器管理中使用,其中包括单个组件状态的通信。例如管理员可对各个组件进行查询,以管理系统的配置或掌握组件的功能状态,如电源和系统风扇。可随时监控内存、硬盘、网络、系统温度等多个参数,增加了系统的安全性,方便了管理。1I2C总线特点

I2C总线原理及应用实例.pdf

电子下载站www.bbww.net资料版权归合法所有者所有严禁用于商业用途I2C总线原理及应用实例I2C(Inter-IntegratedCircuit)总线是一种由PHILIPS公司开发的两线式串行总线,用于连接微控制器及其外围设备。I2C总线产生于在80年代,最初为音频和视频设备开发,如今主要在服务器管理中使用,其中包括单个组件状态的通信。例如管理员可对各个组件进行查询,以管理系统的配置或掌握组件的功能状态,如电源和系统风扇。可随时监控内存、硬盘、网络、系统温度等多个参数,增加了系统的安全性,方便了管