约束与时延分析.pptx

骑着****猪猪

亲,该文档总共53页,到这已经超出免费预览范围,如果喜欢就直接下载吧~

相关资料

约束与时延分析.pptx

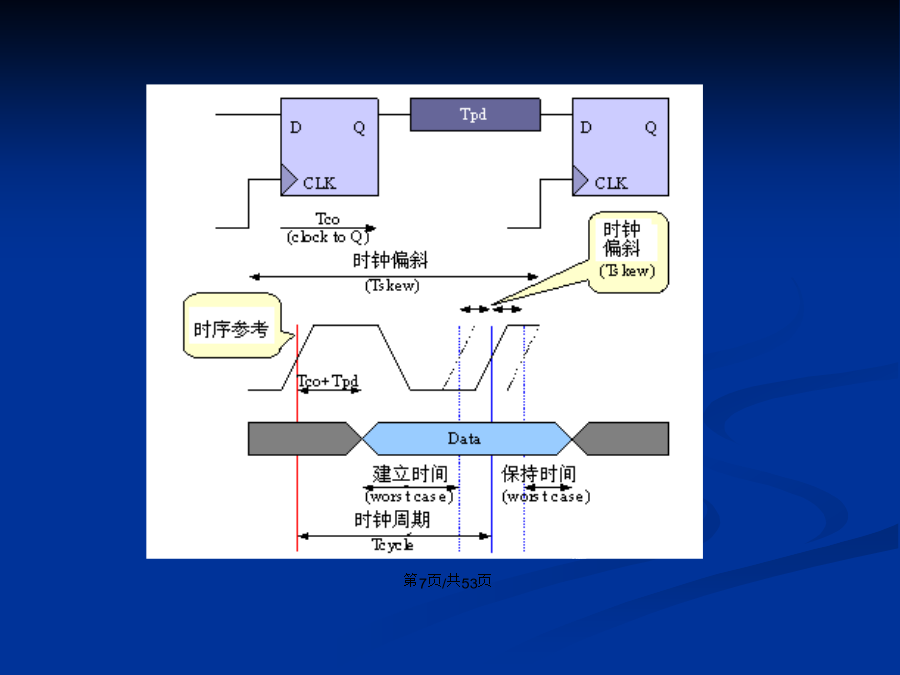

会计学本章主要内容6.1约束的目的6.2管脚约束及电气标准设定6.2.1管脚约束文件Xilinx公司的管脚约束文件.ucf文件的语法规则:通用规则:.ucf文件对于大小写敏感,也就是是说同一单词的大小写不同表示不同的含义,标识符必须与代码中的名字一致。但是约束中的关键字对大小写不敏感。语句以分号结尾,一个语句可以多行表述。语句之间不分先后次序,不过建议管脚约束顺序与代码中管脚列表顺序一致。采用“#”或者“”的方式来进行注释6.3时序约束的基本概念图6–1简单的时序模型6.3.1路径图6–3时序逻辑波形示意

URLLC业务概率时延约束及资源预留的分析与研究.pptx

汇报人:目录PARTONEPARTTWOURLLC业务定义URLLC业务特点URLLC业务应用场景PARTTHREE概率时延约束定义概率时延约束分类概率时延约束影响因素PARTFOUR资源预留技术概述资源预留技术分类资源预留技术实现方法PARTFIVE优化策略概述基于概率时延约束的优化策略基于资源预留的优化策略优化策略实施方案PARTSIX实验验证概述实验环境搭建实验过程及结果分析实验结论及建议PARTSEVEN研究成果总结未来研究方向展望THANKYOU

URLLC业务概率时延约束及资源预留的分析与研究.docx

URLLC业务概率时延约束及资源预留的分析与研究URLLC(Ultra-ReliableandLowLatencyCommunications)是5G通信中的一种关键技术,旨在实现对时延高度敏感的应用场景,如工业自动化、智能交通、远程医疗等。本文将围绕URLLC业务的概率时延约束与资源预留进行分析与研究。一、概率时延约束分析概率时延约束是指在一定时间内业务数据传输的时延需满足一定的概率要求。在URRLLC场景中,由于实时性要求较高,时延约束是关键指标之一。时延约束的分析可以从两个方面进行:业务特性和网络架

基于MPH的时延约束Steiner树算法.docx

基于MPH的时延约束Steiner树算法基于MPH的时延约束Steiner树算法在现代计算机网络中,网络拓扑结构的建立与优化是网络带宽利用率和延迟性能的重要关键。Steiner树算法是一种高效的网络拓扑优化算法,通过在网络中添加一些额外的节点,以实现创建更加优化的网络拓扑结构。然而,在一些特定的网络拓扑应用场景(如移动通信网络和互联网中的实时应用),除了满足最短路径或最小生成树等基本约束条件之外,还需要满足时延约束等一系列限制条件。因此,如何在满足时延约束的前提下进行Steiner树的构建是当前研究的热点

新的基于MPH的时延约束Steiner树算法.docx

新的基于MPH的时延约束Steiner树算法随着计算机技术的发展和应用领域的不断拓展,网络通信成为不可或缺的一部分。然而,网络连接中常常发生的问题是网络时延。网络时延会导致数据传输速率变慢,影响网络的效率和性能。为了解决这个问题,研究人员提出了基于MPH(Maximumpossiblehop)的时延约束Steiner树算法,该算法能够有效地提高网络传输效率。MPH是指最大可能跳数,是计算两个节点之间最短路径的一种方法。MPH可以用于计算网络中任何两个节点之间的最短路径,并且可以被用作测量网络中节点到节点之