基于FPGA的USB3.0中扰码及解扰码电路设计的任务书.docx

快乐****蜜蜂

在线预览结束,喜欢就下载吧,查找使用更方便

相关资料

基于FPGA的USB3.0中扰码及解扰码电路设计的任务书.docx

基于FPGA的USB3.0中扰码及解扰码电路设计的任务书任务书一、任务背景随着信息时代迅猛发展,对数据传输速率的需求也越来越迫切。USB(UniversalSerialBus,通用串行总线)作为一种非常重要的数据传输接口,其运行速率的提升也变得迫在眉睫。USB3.0标准是USB技术的全新版本,其数据传输速率高达5Gbps,是USB2.0标准的10倍以上,很好地解决了USB2.0在移动存储、高清视频等应用场景中速率过低的问题。而FPGA(Field-ProgrammableGateArray,现场可编程门阵

基于FPGA的USB3.0扰码及解扰码电路研究与设计的开题报告.docx

基于FPGA的USB3.0扰码及解扰码电路研究与设计的开题报告题目:基于FPGA的USB3.0扰码及解扰码电路研究与设计的开题报告1.研究背景和意义USB(UniversalSerialBus)接口已经成为现代计算机系统中最为普遍的接口之一。随着数据传输速度的不断提高,USB3.0成为了新时代的标志性技术。USB3.0比前代USB2.0的传输速度提高了十倍以上,从而大大加快了USB设备与计算机之间数据传输的速率。然而,USB3.0的传输速率的提高也增加了对数据传输安全的要求。在精准的数据传输时,扰码技术是

基于码重分布的自同步扰码盲识别方法.pdf

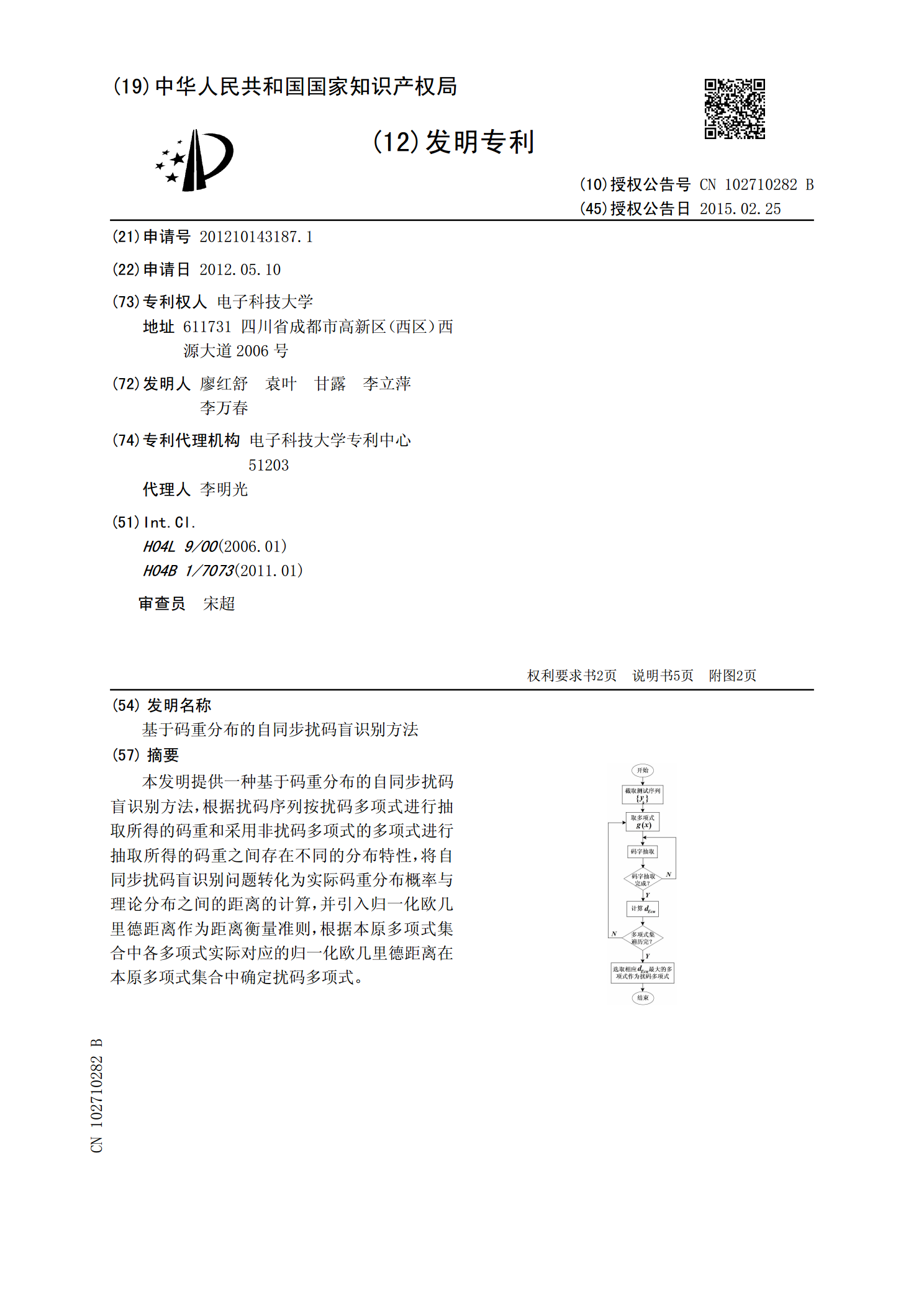

本发明提供一种基于码重分布的自同步扰码盲识别方法,根据扰码序列按扰码多项式进行抽取所得的码重和采用非扰码多项式的多项式进行抽取所得的码重之间存在不同的分布特性,将自同步扰码盲识别问题转化为实际码重分布概率与理论分布之间的距离的计算,并引入归一化欧几里德距离作为距离衡量准则,根据本原多项式集合中各多项式实际对应的归一化欧几里德距离在本原多项式集合中确定扰码多项式。

扰码配置方法和装置.pdf

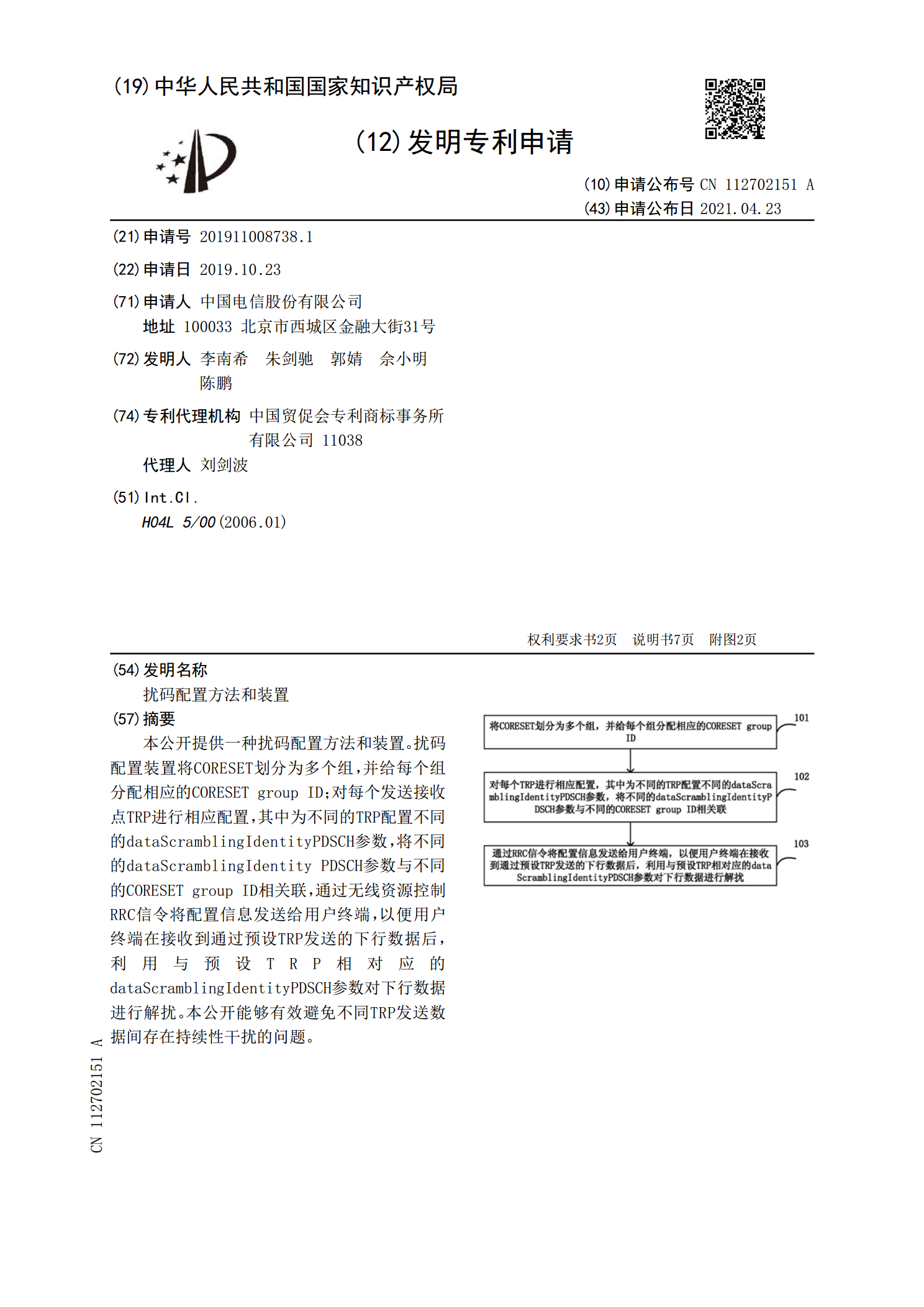

本公开提供一种扰码配置方法和装置。扰码配置装置将CORESET划分为多个组,并给每个组分配相应的CORESETgroupID;对每个发送接收点TRP进行相应配置,其中为不同的TRP配置不同的dataScramblingIdentityPDSCH参数,将不同的dataScramblingIdentityPDSCH参数与不同的CORESETgroupID相关联,通过无线资源控制RRC信令将配置信息发送给用户终端,以便用户终端在接收到通过预设TRP发送的下行数据后,利用与预设TRP相对应的dataSc

码间串扰的产生及消除.doc

码间串扰的产生及消除姓名:郭耀华学号:120104030030班级:通信工程1班什么是码间串扰所谓码间串扰,就是数字基带信号通过基带传输系统时,由于系统(主要是信道)传输特性不理想,或者由于信道中加性噪声的影响,使收端脉冲展宽,延伸到邻近码元中去,从而造成对邻近码元的干扰,我们将这种现象称为码间串扰。1011码间串扰如何产生直方脉冲的波形在时域内比较尖锐,因而在频域内占用的带宽是无限的。如果让这个脉冲经过一个低通滤波器,即让它的频率变窄,那么它在时域内就一定会变宽。因为脉冲是一个序列,这样相邻的脉冲间就会