Ka频段收发信机单元电路单片集成电路研究的中期报告.docx

快乐****蜜蜂

在线预览结束,喜欢就下载吧,查找使用更方便

相关资料

Ka频段收发信机单元电路单片集成电路研究的中期报告.docx

Ka频段收发信机单元电路单片集成电路研究的中期报告本报告对Ka频段收发信机单元电路单片集成电路的研究进行了中期总结和展望。首先,我们对Ka频段收发信机单元电路的特性和需求进行了分析和总结。Ka频段通常被定义为26.5GHz到40GHz的频段,因其具有广阔的带宽和高速数据传输能力而备受关注。Ka频段收发信机单元电路是指在这个频段内完成射频信号的接收、变频、滤波、放大等过程的电路单元。其特点包括高频率、高速传输、高增益和低噪声等。接下来,我们对当前Ka频段收发信机单元电路单片集成电路技术的研究现状进行了梳理。

一种小型化Ka频段收发信机.pdf

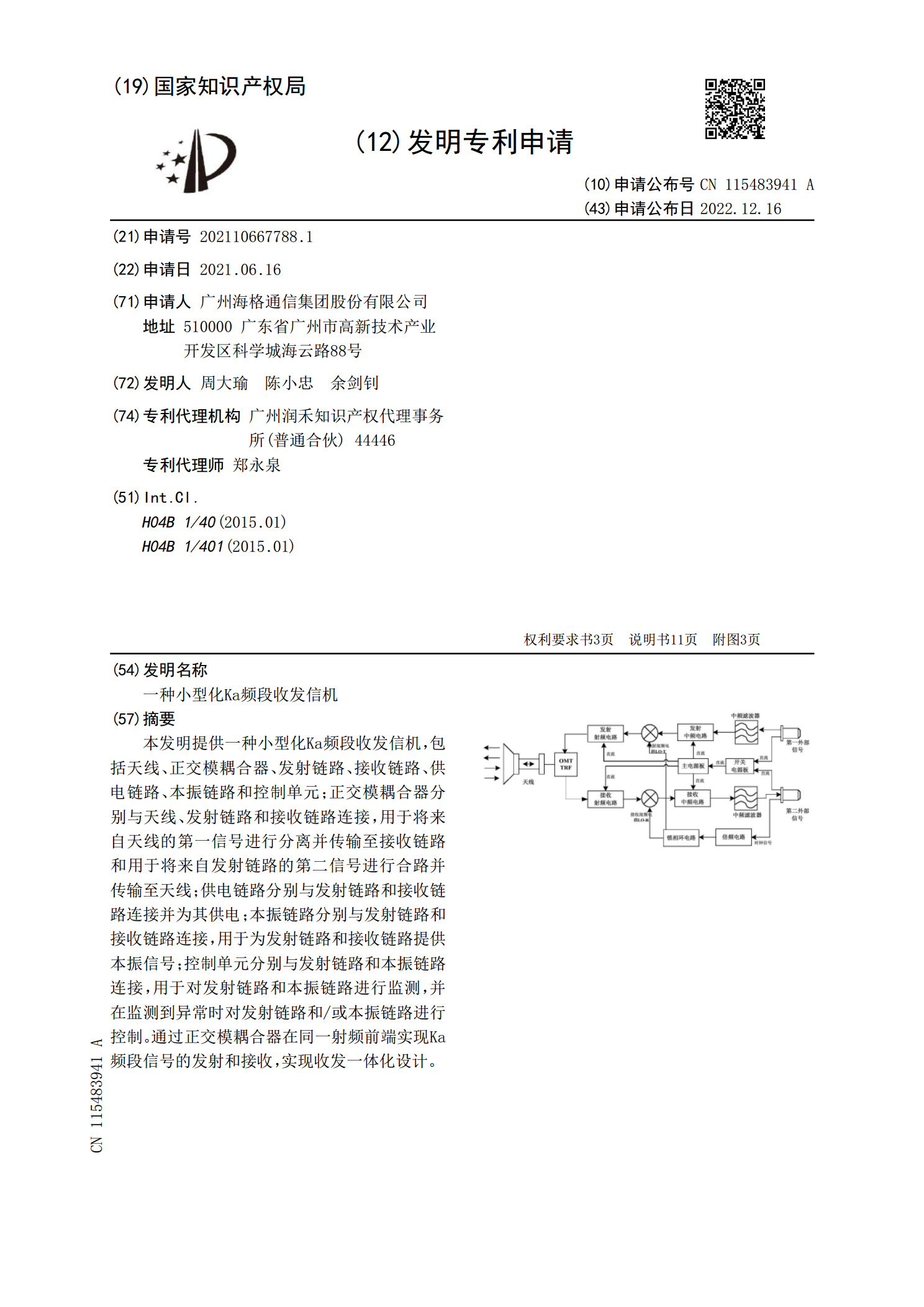

本发明提供一种小型化Ka频段收发信机,包括天线、正交模耦合器、发射链路、接收链路、供电链路、本振链路和控制单元;正交模耦合器分别与天线、发射链路和接收链路连接,用于将来自天线的第一信号进行分离并传输至接收链路和用于将来自发射链路的第二信号进行合路并传输至天线;供电链路分别与发射链路和接收链路连接并为其供电;本振链路分别与发射链路和接收链路连接,用于为发射链路和接收链路提供本振信号;控制单元分别与发射链路和本振链路连接,用于对发射链路和本振链路进行监测,并在监测到异常时对发射链路和/或本振链路进行控制。通过

Ka频段卫星通信地球站的研究的中期报告.docx

Ka频段卫星通信地球站的研究的中期报告本次研究旨在探讨Ka频段卫星通信地球站的技术特点、应用领域以及发展趋势。在调研分析的基础上,我们得出以下中期报告:一、技术特点1.高频段:Ka频段的工作频段位于26.5-40GHz,比C、Ku频段更高,能够提供更大的带宽。2.高速率:Ka频段卫星通信地球站提供的速率一般在100Mbps以上,最高可达1Gbps,能够满足高速率数据传输需求。3.小型化:Ka频段卫星通信地球站的设备尺寸较小,便于安装和移动,适用于移动通信、应急通信等场景。4.高价格:在高频段和高速率的同时

Ka频段有源倍频模块设计的中期报告.docx

Ka频段有源倍频模块设计的中期报告一、研究背景目前,随着通信技术的不断发展和普及,对高频、高速数字信号的需求越来越大,尤其是高频通信领域。为了满足这种需求,人们需要不断开发新的高性能、低成本、小型化的射频设备和模块。在射频收发中,高频信号的发射需要解决的一个关键问题就是如何实现高功率输出。传统的方法是使用高功率功率放大器,但同时也会引入一些问题,例如高功率放大器需要耗费大量电能,并且容易产生热量,会影响设备的性能和寿命。为了解决这个问题,有源倍频技术出现了。有源倍频技术通过将几个信号合并在一起,然后增强它

一种超宽带Ka频段收发信方法.pdf

本发明涉及一种超宽带Ka频段收发信方法。属于卫星移动通信技术领域。超宽带Ka频段收发信方法通过超宽带Ka频段收发信机实现,接收采用一次变频方案。将17.7GHz~21.2GHz分为三段,射频部分不做分段,频段具体划分由本振部分来完成,三个射频频段对应同一个中频频段,可以兼容现在通用的调制解调器。本振频率源为跳频源,根据不同的外部控制,输出不同的本振频率。发射采用一次变频方案。将27.5GHz~31GHz分成三个频段。发射频段划分,由射频部分的射频滤波器组合本振跳频源共同完成。本发明中的Ka频段收发信方法,