第二章 VHDL语言程序的基本结构.ppt

sy****28

亲,该文档总共64页,到这已经超出免费预览范围,如果喜欢就直接下载吧~

相关资料

第二章 VHDL语言程序的基本结构.ppt

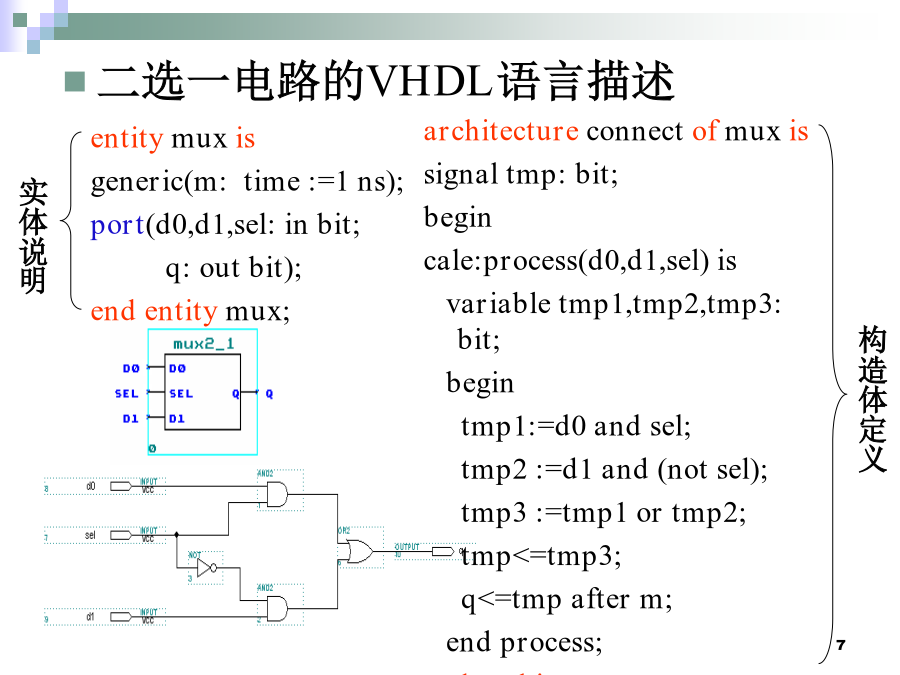

第二章VHDL语言程序的基本结构本章内容:完整VHDL语言程序结构2.1VHDL语言设计的基本单元及其构成outputnVHDL语言程序设计的基本单元architectureconnectofmuxissignaltmp:bit;begincale:process(d0,d1,sel)isvariabletmp1,tmp2,tmp3:bit;begintmp1:=d0andsel;tmp2:=d1and(notsel);tmp3:=tmp1ortmp2;tmp<=tmp3;q<=tmpafterm;end

VHDL程序基本结构.ppt

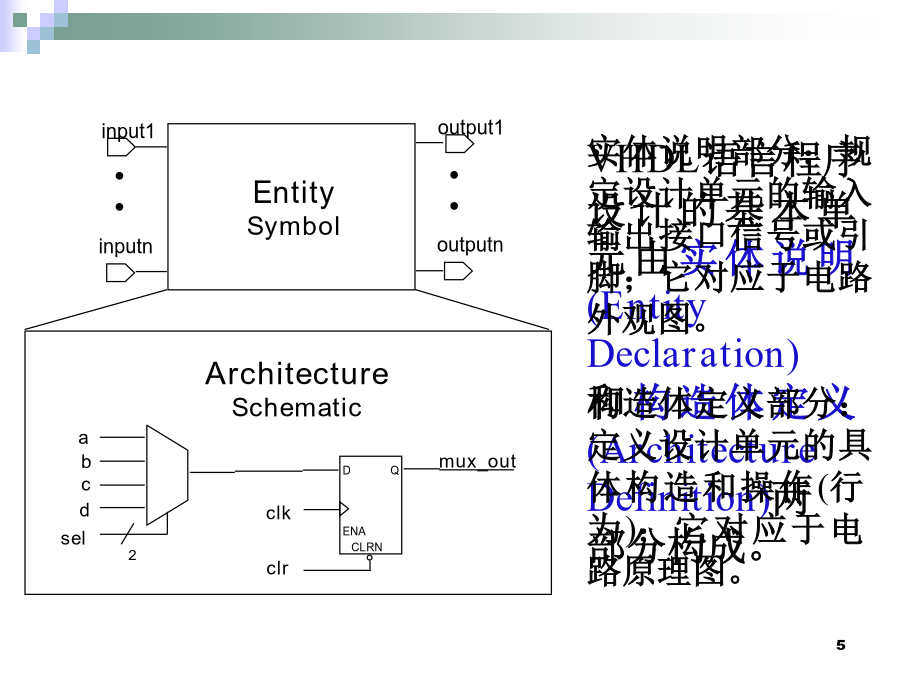

图2.4VHDL程序设计基本结构(1)库、程序包使用说明:用于打开(调用)本设计实体将要用到的库、程序包;程序包存放各个设计模块共享的数据类型、常数和子程序等;库是专门存放预编译程序包的地方。实体(ENTITY)是一个设计实体的表层设计单元,其功能是对这个设计实体与外部电路进行接口描述。它规定了设计单元的输入输出接口信号或引脚,是设计实体经封装后对外的一个通信界面。1.实体语句结构实体说明单元的常用语句结构如下:ENTITY实体名IS[GENERIC(类属表);][PORT(端口表);]END[ENTIT

VHDL程序基本结构.ppt

图2.4VHDL程序设计基本结构(1)库、程序包使用说明:用于打开(调用)本设计实体将要用到的库、程序包;程序包存放各个设计模块共享的数据类型、常数和子程序等;库是专门存放预编译程序包的地方。实体(ENTITY)是一个设计实体的表层设计单元,其功能是对这个设计实体与外部电路进行接口描述。它规定了设计单元的输入输出接口信号或引脚,是设计实体经封装后对外的一个通信界面。1.实体语句结构实体说明单元的常用语句结构如下:ENTITY实体名IS[GENERIC(类属表);][PORT(端口表);]END[ENTIT

第2讲VHDL程序基本结构及语言要素.ppt

第二讲VHDL程序基本结构及语言要素课题:VHDL程序基本结构及语言要素1.VHDL简介VHDL的英文全名是Very-High-SpeedIntegratedCircuitHardwareDescriptionLanguage,诞生于1982年。1987年底,VHDL被IEEE和美国国防部确认为标准硬件描述语言。自IEEE公布了VHDL的标准版本(IEEE-1076)之后,各EDA公司相继推出了自己的VHDL设计环境,或宣布自己的设计工具可以和VHDL接口。此后VHDL在电子设计领域得到了广泛的接受,并逐

VHDL程序基本结构ppt课件.ppt

图2.4VHDL程序设计基本结构(1)库、程序包使用说明:用于打开(调用)本设计实体将要用到的库、程序包;程序包存放各个设计模块共享的数据类型、常数和子程序等;库是专门存放预编译程序包的地方。实体(ENTITY)是一个设计实体的表层设计单元,其功能是对这个设计实体与外部电路进行接口描述。它规定了设计单元的输入输出接口信号或引脚,是设计实体经封装后对外的一个通信界面。1.实体语句结构实体说明单元的常用语句结构如下:ENTITY实体名IS[GENERIC(类属表);][PORT(端口表);]END[ENTIT