一种故障攻击检测电路及故障攻击防护方法.pdf

书生****瑞梦

亲,该文档总共13页,到这已经超出免费预览范围,如果喜欢就直接下载吧~

相关资料

一种故障攻击检测电路及故障攻击防护方法.pdf

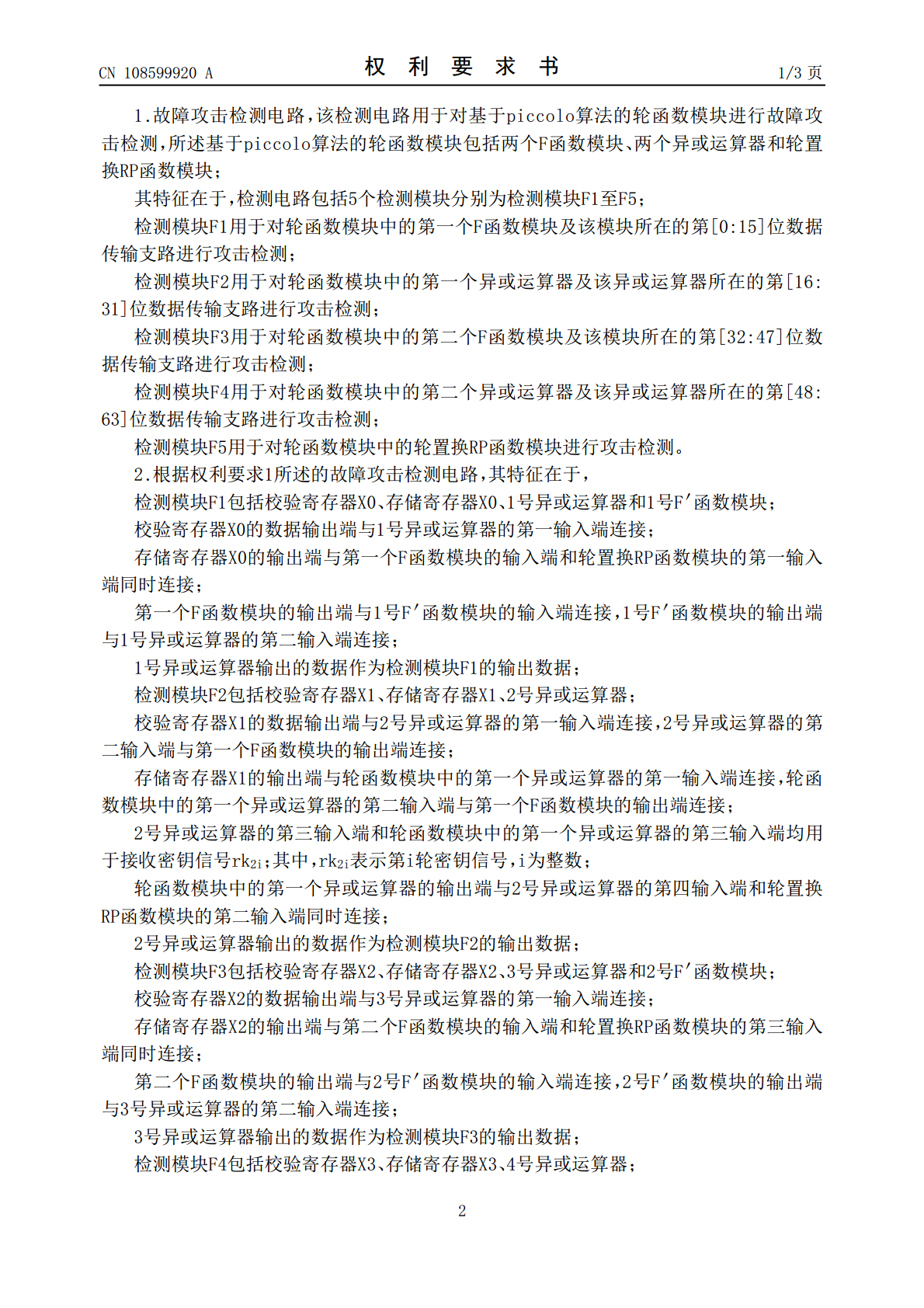

一种故障攻击检测电路及故障攻击防护方法,涉及密码算法领域。解决了现有技术中无法对安全芯片中基于piccolo算法的轮函数模块进行攻击检测及故障防护的问题。检测电路包括5个检测模块,且5个检测模块对基于piccolo算法的轮函数模块中的两个F函数模块、两个异或运算器和轮置换RP函数模块进行检测,及其对基于piccolo算法的轮函数模块中的两个F函数模块、两个异或运算器和轮置换RP函数模块所在的数据传输支路进行检测。本发明主要对由基于piccolo算法的轮函数模块构成的智能卡设备的攻击故障进行检测。

集成电路故障注入攻击仿真方法.docx

集成电路故障注入攻击仿真方法摘要:随着集成电路(IntegratedCircuit,IC)应用越来越广泛,IC的安全风险也越来越突出。其中,故障注入攻击(FaultInjectionAttack,FIA)是一种常见的攻击方式,可以破坏IC的功能和保护机制。因此,对FIA的仿真研究具有重要的意义。本文主要介绍了FIA的基本原理和分类,介绍了几种常用的FIA仿真方法,详细分析了仿真方法的优缺点,最后提出了未来FIA仿真研究的方向和挑战。一、绪论随着信息时代的到来,IC的应用越来越广泛。然而,IC的安全风险也相

分组密码算法抗功耗攻击和故障攻击的方法.docx

分组密码算法抗功耗攻击和故障攻击的方法摘要:分组密码算法是现代密码学中常用的一种加密技术,它被广泛应用于各个领域的信息保护。然而随着攻击手段的不断进步,分组密码算法面临着越来越多的安全威胁。功耗攻击和故障攻击是当前较为常见的攻击手段之一,本文主要探讨分组密码算法抵制功耗攻击和故障攻击的方法。(一)研究背景随着现代计算技术的不断发展,加密技术一直是信息安全领域中的一个热点。分组密码算法作为一种常用的加密方式,被广泛应用于各个领域,例如银行、电子商务、政府机构等。然而,随着攻击手段的不断升级,分组密码算法也面

Miller算法的故障攻击研究.docx

Miller算法的故障攻击研究AbstractFaultattackshavebecomeoneofthemostprominentthreatstosecurity,particularlyincryptography.Milleralgorithmisawell-knownalgorithmforpointmultiplicationinellipticcurvecryptography(ECC),whichisvulnerabletofaultattacks.Thispaperreviewsther

一种检测AES-JAMBU抵御差分故障攻击的方法.pdf

本发明提供了一种检测AES?JAMBU抵御差分故障攻击的方法,首先通过AES?JAMBU认证加密算法对明文消息进行处理,在此阶段控制两种不同的实验环境,一种是要令实验环境不受任何干扰,保证算法对明文消息处理的结果正确无误;另一种是在算法对明文消息处理的过程中,使用某些物理手段,对处理过程进行干扰,诱导其产生故障,获得错误的输出。通过计算正确结果和错误结果的差分值,来测评算法对差分故障攻击的抵御能力。然后通过判断所导入的故障的有效性,并确定故障导入的位置,进而恢复出密钥。本发明具有简单、快捷、准确且易于实现