一种并行写入多通道FIFO的方法及装置.pdf

猫巷****晓容

在线预览结束,喜欢就下载吧,查找使用更方便

相关资料

一种并行写入多通道FIFO的方法及装置.pdf

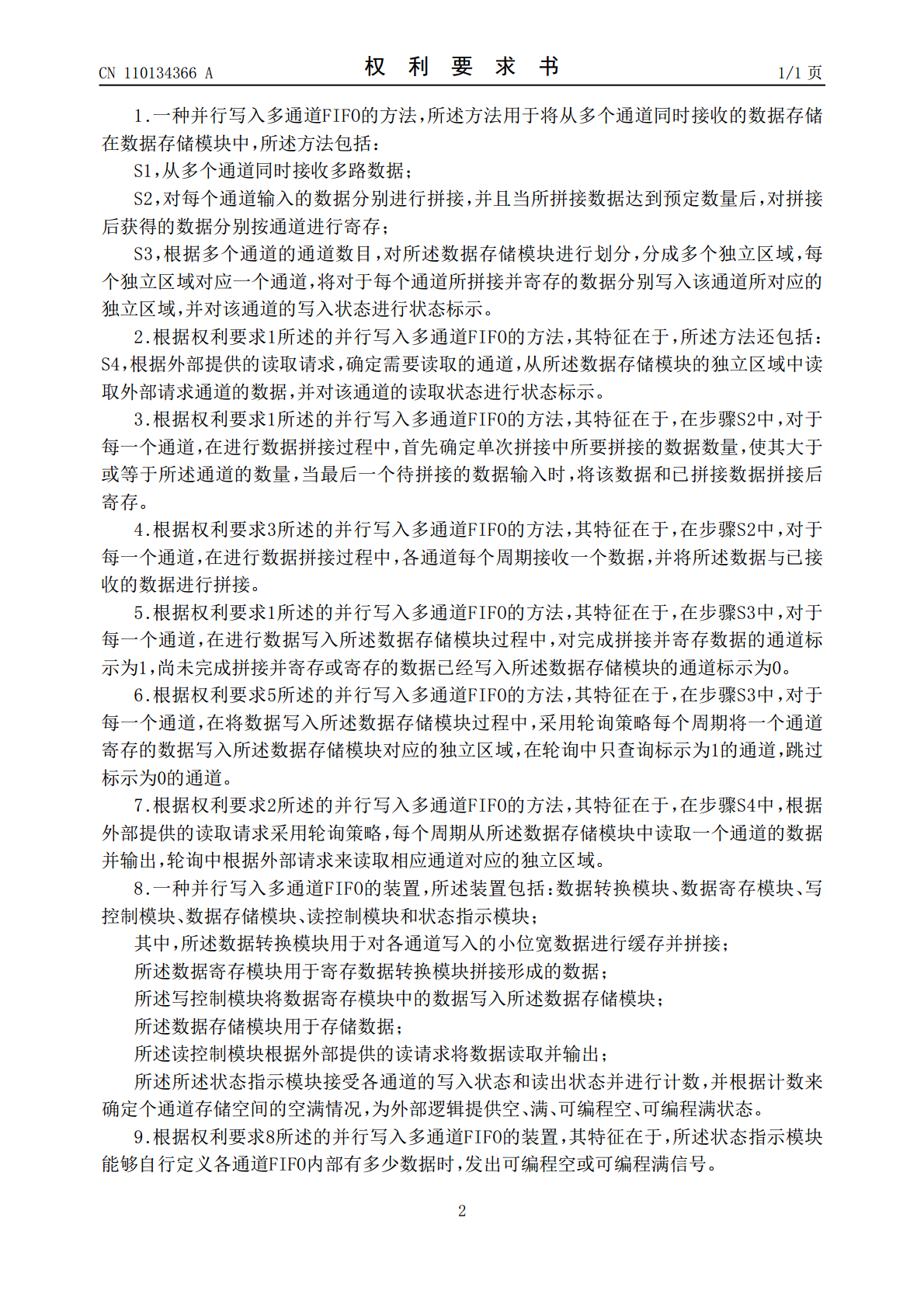

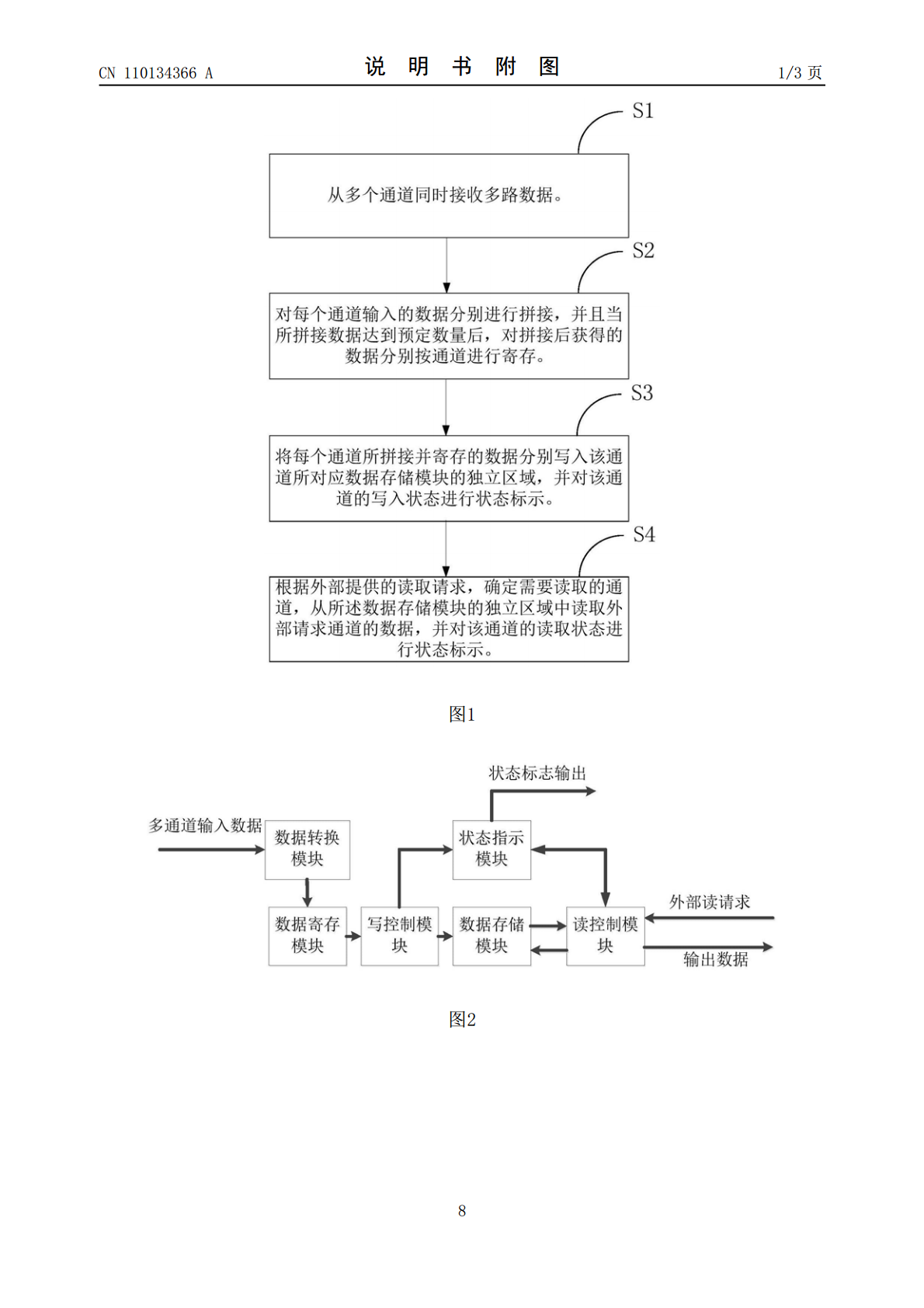

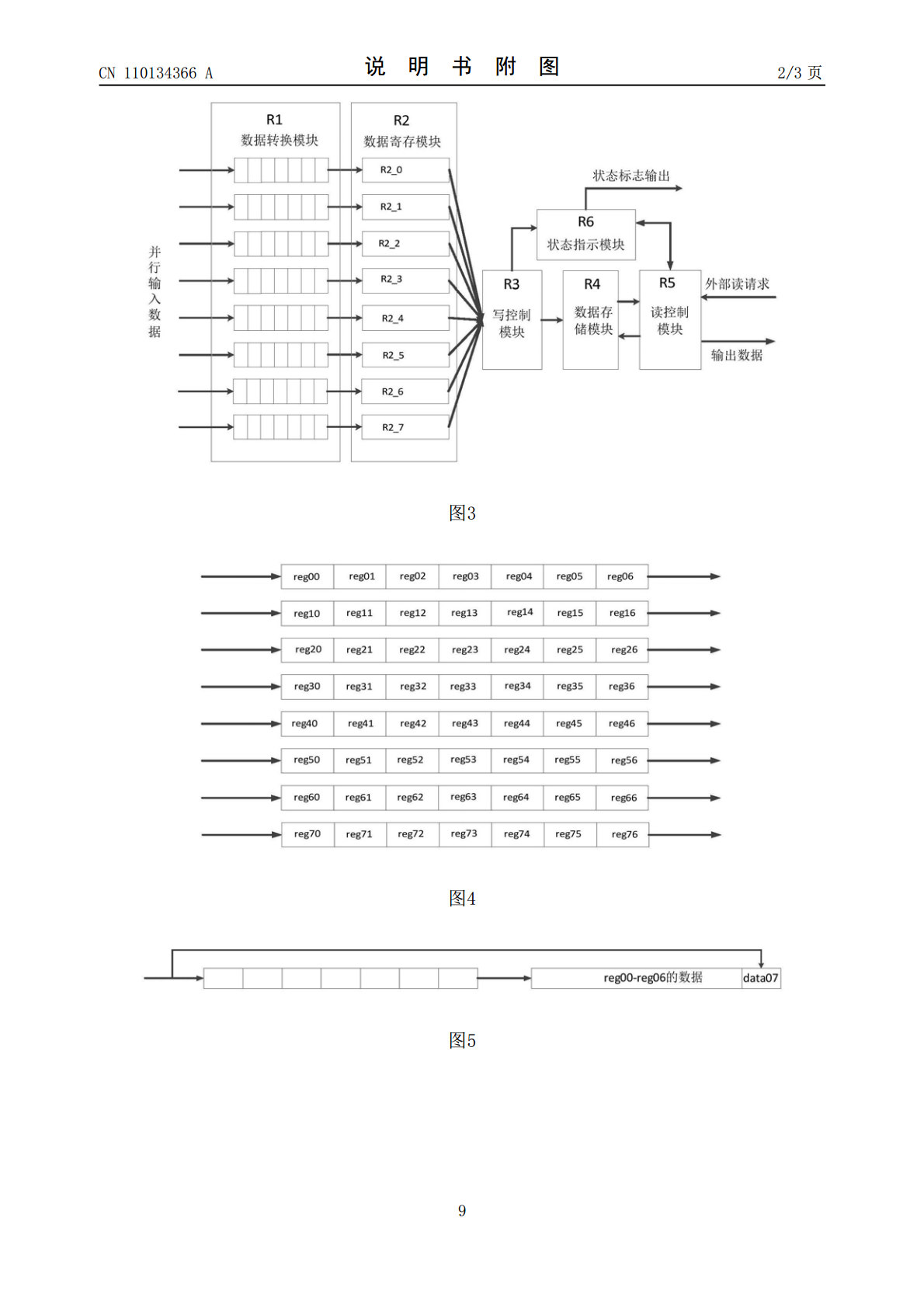

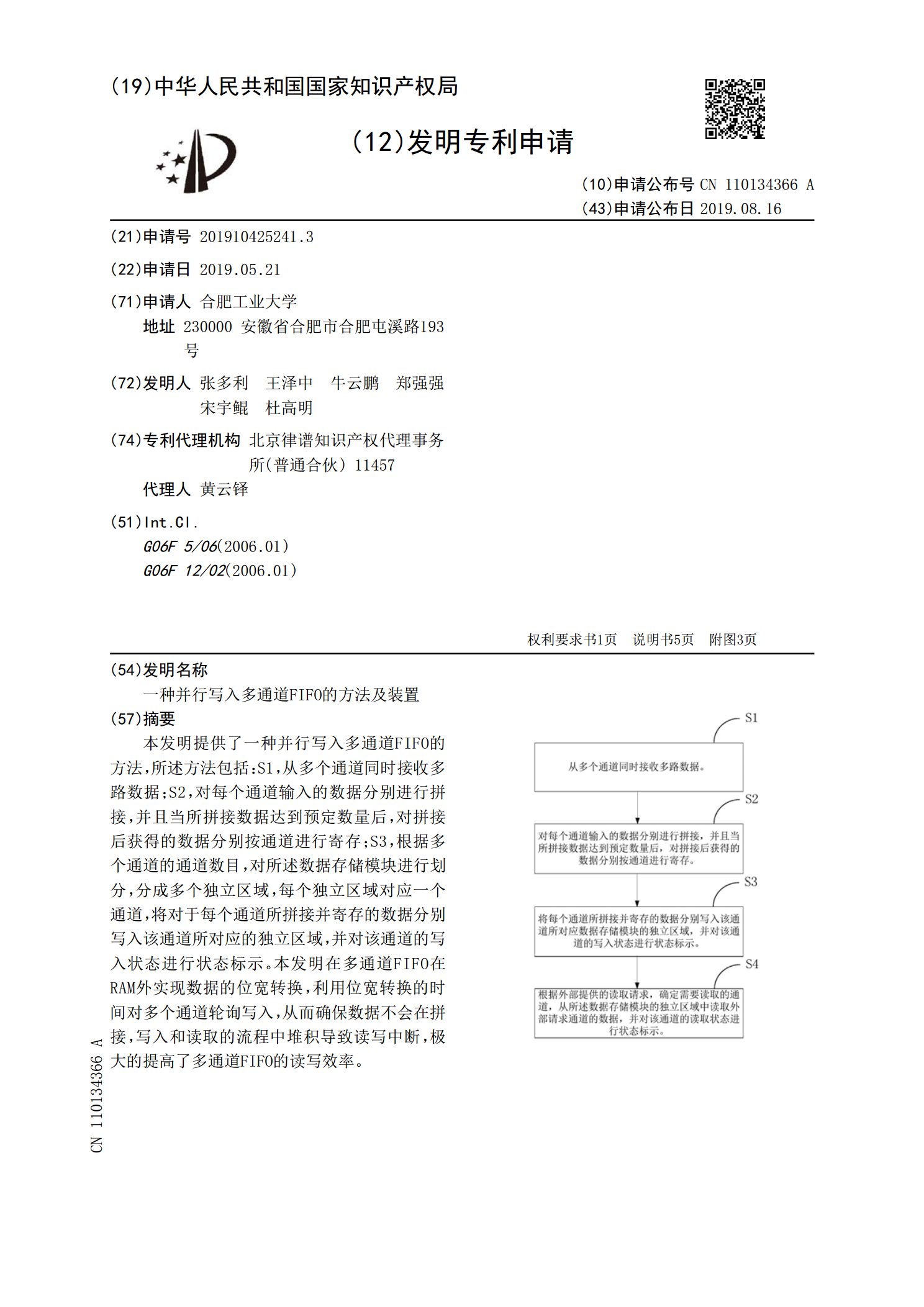

本发明提供了一种并行写入多通道FIFO的方法,所述方法包括:S1,从多个通道同时接收多路数据;S2,对每个通道输入的数据分别进行拼接,并且当所拼接数据达到预定数量后,对拼接后获得的数据分别按通道进行寄存;S3,根据多个通道的通道数目,对所述数据存储模块进行划分,分成多个独立区域,每个独立区域对应一个通道,将对于每个通道所拼接并寄存的数据分别写入该通道所对应的独立区域,并对该通道的写入状态进行状态标示。本发明在多通道FIFO在RAM外实现数据的位宽转换,利用位宽转换的时间对多个通道轮询写入,从而确保数据不会

一种阵列天线多通道并行测试装置、测试方法及校准方法.pdf

本发明提供了一种阵列天线多通道并行测试装置,包括指示天线、待测阵列天线、多通道矢量网络分析仪、测控计算机以及微波功率放大器;多通道矢量网络分析仪包括多个射频信号输入端和1个射频信号输出端,射频信号输出端经微波功率放大器与指示天线射频端口连接,多个射频信号输入端与待测阵列天线各阵元射频端口对应连接;指示天线设置在极化转台上,由极化控制器控制转动;待测阵列天线设置在转台上,由转台控制器控制转动;测控计算机通过控制待测阵列天线和指示天线转动,以及接收多通道矢量网络分析仪采集的幅度相位数据完成测试。本发明能够显著

多通道并行的光器件频谱响应测量方法及装置.pdf

本发明公开了一种多通道并行的光器件频谱响应测量方法,包括:步骤1、将微波信号调制于第一光频梳信号,生成多通道载波抑制光双边带信号;然后将其与第二光频梳信号耦合,生成多通道非对称光双边带信号,即为探测光信号;第一、第二光频梳信号的梳齿频率间隔不同;步骤2、令探测光信号通过待测光器件后进行光电转换,然后从中并行提取出待测光器件在每个通道的频谱响应;步骤3、将待测光器件在每个通道上的频响组合为待测光器件完整的频谱响应。本发明还公开了一种多通道并行的光器件频谱响应测量装置。本发明可同时实现高分辨率、大范围的快速高

一种基于FPGA和FIFO芯片的多通道HDLC数据处理装置.pdf

本发明公开了一种基于FPGA和FIFO芯片的多通道HDLC数据处理装置。该装置采用FPGA片上自带接收RAM和FPGA外挂接收FIFO芯片实现对接收HDLC数据和待发送数据的缓存,接收FIFO控制器通过高速轮询机制将所有通道接收RAM中数据高效快速传递到接收FIFO芯片,实现接收方向的大缓存,从而支持大数据突发业务;发送FIFO芯片根据各通道RAM状态将数据依次发送到对应通道RAM,发送FIFO芯片缓存大量的待发送数据,可使CPU一次操作写入大量数据,减少了CPU的频繁访问,有利于提高CPU效率利用。本发

到磁带的多主机并行写入.pdf

根据一实施例,一种用于将数据存储于一磁带上的方法包括:接收来自两个不同主机的数据;及使用多个传感器同时将来自所述主机的数据写入至该磁带。在另一途径中,一种用于将数据存储于一磁带上的方法包括:接收来自多个主机的建立一并行保留的请求;及将一线带中的一唯一磁条分配给发送了所述请求的所述主机中的每一个,其中该线带为将由一磁带头的多个传感器在磁带移动的一个方向上同时写入的数据磁道的一集合,且该线带被逻辑地分为所述磁条。又,该方法包括:接收来自所述主机的数据;及使用该多个传感器同时将来自所述主机的数据写入至该磁带。也