FPGA动态可重构数字电路容错系统的研究.pdf

qw****27

在线预览结束,喜欢就下载吧,查找使用更方便

相关资料

FPGA动态可重构数字电路容错系统的研究.pdf

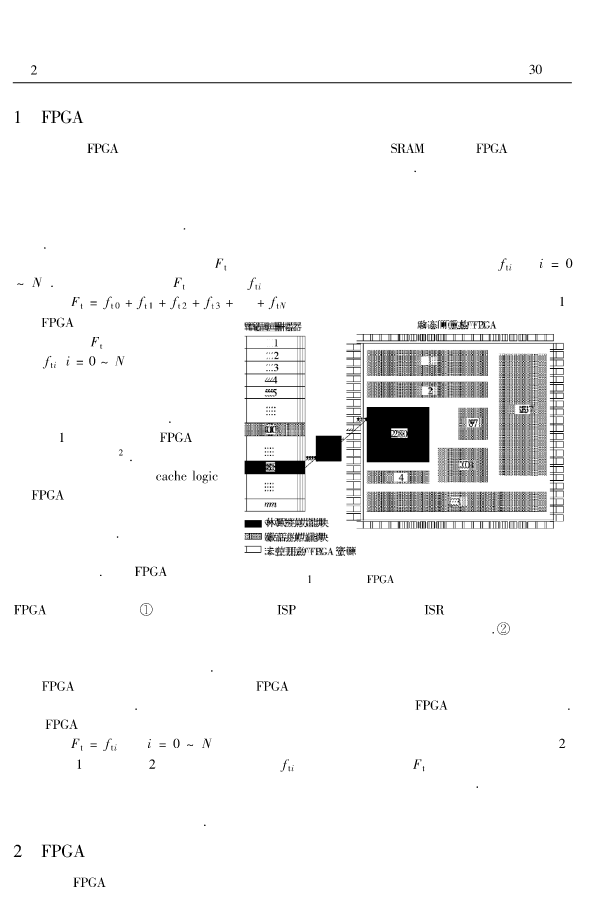

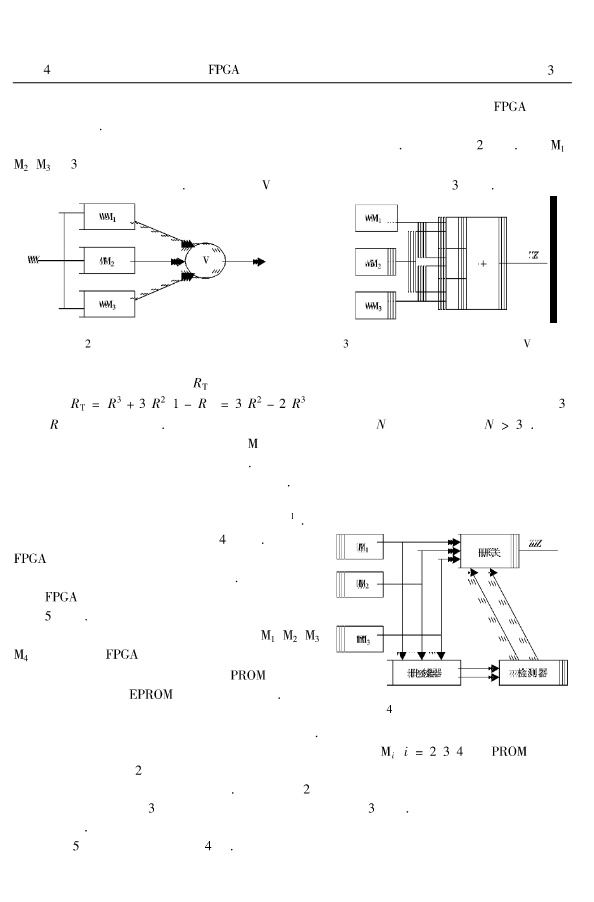

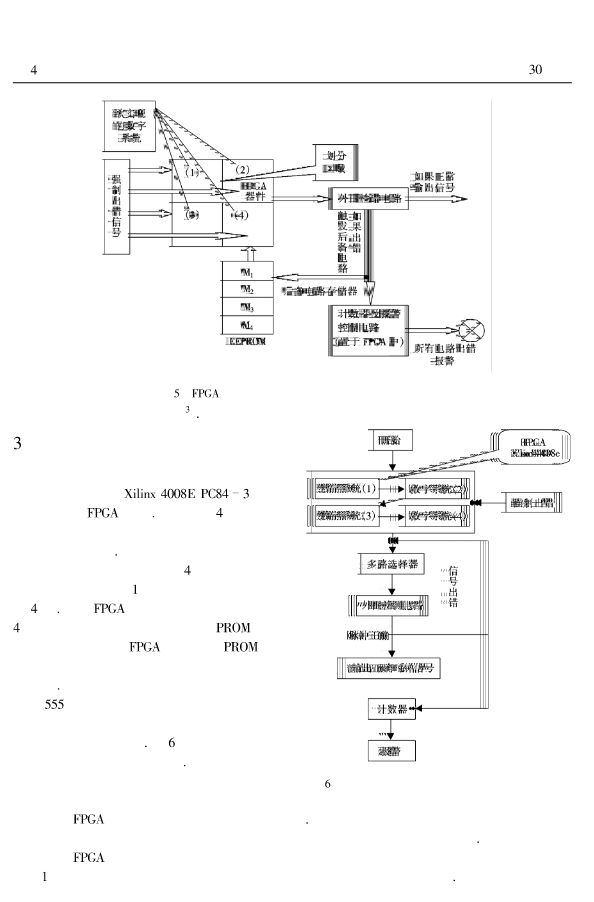

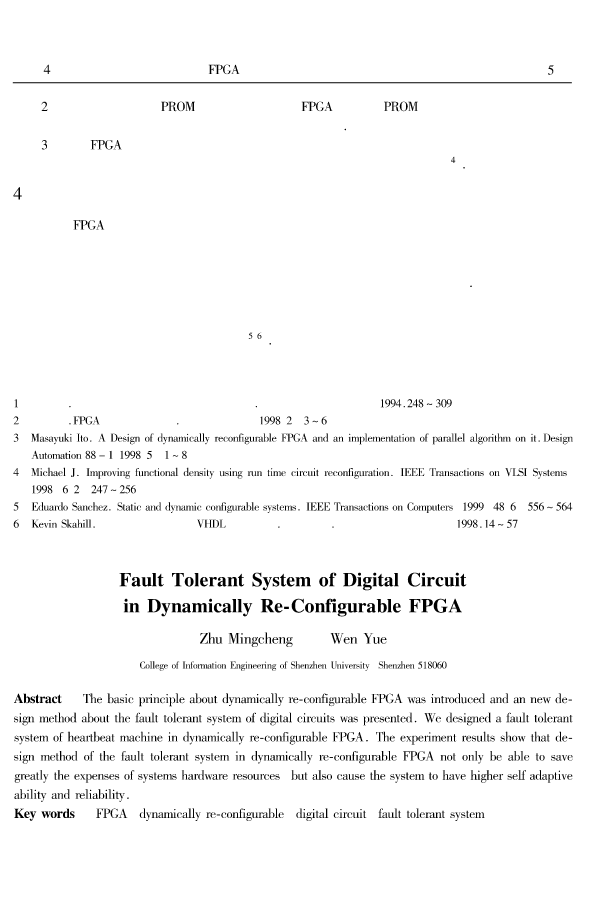

第!"卷第#期东南大学学报(自然科学版)3?9@!"*?@#$"""年%月&’()*+,’-.’(/01+./(*231).2/4(*567859.:;<=:<1>;6;?=)&79A$""""""""""""""""""""""""""""""""""""""""""""""""""""""""""-BC+动态可重构数字电路容错系统的研究!朱明程温粤(深圳大学信息工程学院,深圳DEF"G")摘要在介绍-BC+动态可重构技术原理的基础上,探讨了该技术在数字电路容错系统中的应用方法和构成原理,并针对某心脏起

SRAM型FPGA的可重构容错结构研究的开题报告.docx

SRAM型FPGA的可重构容错结构研究的开题报告【开题报告】一、选题依据和背景随着集成电路的不断发展和应用领域的扩展,芯片的可靠性和可重构性也成为了人们越来越关注的问题,尤其是在高可靠性应用领域,如航空航天、军事、医疗等方面。而FPGA(现场可编程门阵列)作为一种可重构的芯片,在芯片可靠性和可重构性强的优势下,已经被广泛应用于各种大型系统中,越来越受到人们的关注。不过,随着FPGA设计规模的增大,芯片设计的容错问题变得愈加迫切。因此,研究可重构容错的FPGA结构及其应用成为了当前FPGA热点及难点的问题之

基于动态可重构FPGA的时序电路在线故障检测与容错设计.docx

基于动态可重构FPGA的时序电路在线故障检测与容错设计摘要:在现代电子设备中,时序电路的故障检测和容错设计非常重要。本论文提出了一种基于动态可重构FPGA的在线时序电路故障检测和容错设计方法。该方法利用FPGA的动态可重构性和在线故障检测技术,实现了一种低成本、低复杂度的时序电路故障检测和容错设计方案。具体来说,该方案包括三个主要的技术:故障检测、故障定位和故障恢复。在故障检测方面,本论文利用FPGA的内置信号测量器和动态可重构技术,实时监测电路的运行状况,并检测出故障信号。在故障定位方面,本论文提出了一

基于FPGA的动态可重构技术研究.pptx

基于FPGA的动态可重构技术研究目录添加目录项标题FPGA技术概述FPGA的基本概念FPGA的发展历程FPGA的应用领域FPGA的优势与限制动态可重构技术介绍动态可重构技术的概念动态可重构技术的分类动态可重构技术的应用场景动态可重构技术的优势与挑战基于FPGA的动态可重构系统设计系统架构设计硬件资源优化动态配置管理实时重构实现基于FPGA的动态可重构技术研究现状与发展趋势研究现状发展趋势技术挑战与展望基于FPGA的动态可重构技术的应用案例分析通信领域应用案例图像处理领域应用案例控制系统应用案例其他领域应用

动态可重构FPGA布局算法的研究与改进.docx

动态可重构FPGA布局算法的研究与改进摘要:随着技术的不断进步,可重构逻辑芯片(FPGA)作为一种具有灵活性和可编程性的解决方案,被越来越广泛地应用于各个领域。其中,FPGA布局算法是实现高效和可靠FPGA设计的关键技术。因此,本论文研究了动态可重构FPGA布局算法的基本原理和算法,并提出了一种改进算法。关键词:可重构逻辑芯片,FPGA,布局算法,动态可重构FPGA,改进算法1.引言以可重构逻辑芯片(FPGA)为代表的可编程逻辑器件的快速发展,是计算机硬件设计领域的重要进展之一。FPGA具有灵活性、可重构