基于FPGA的多路数据采集系统设计.pdf

qw****27

在线预览结束,喜欢就下载吧,查找使用更方便

相关资料

基于FPGA的多路数据采集系统设计.pdf

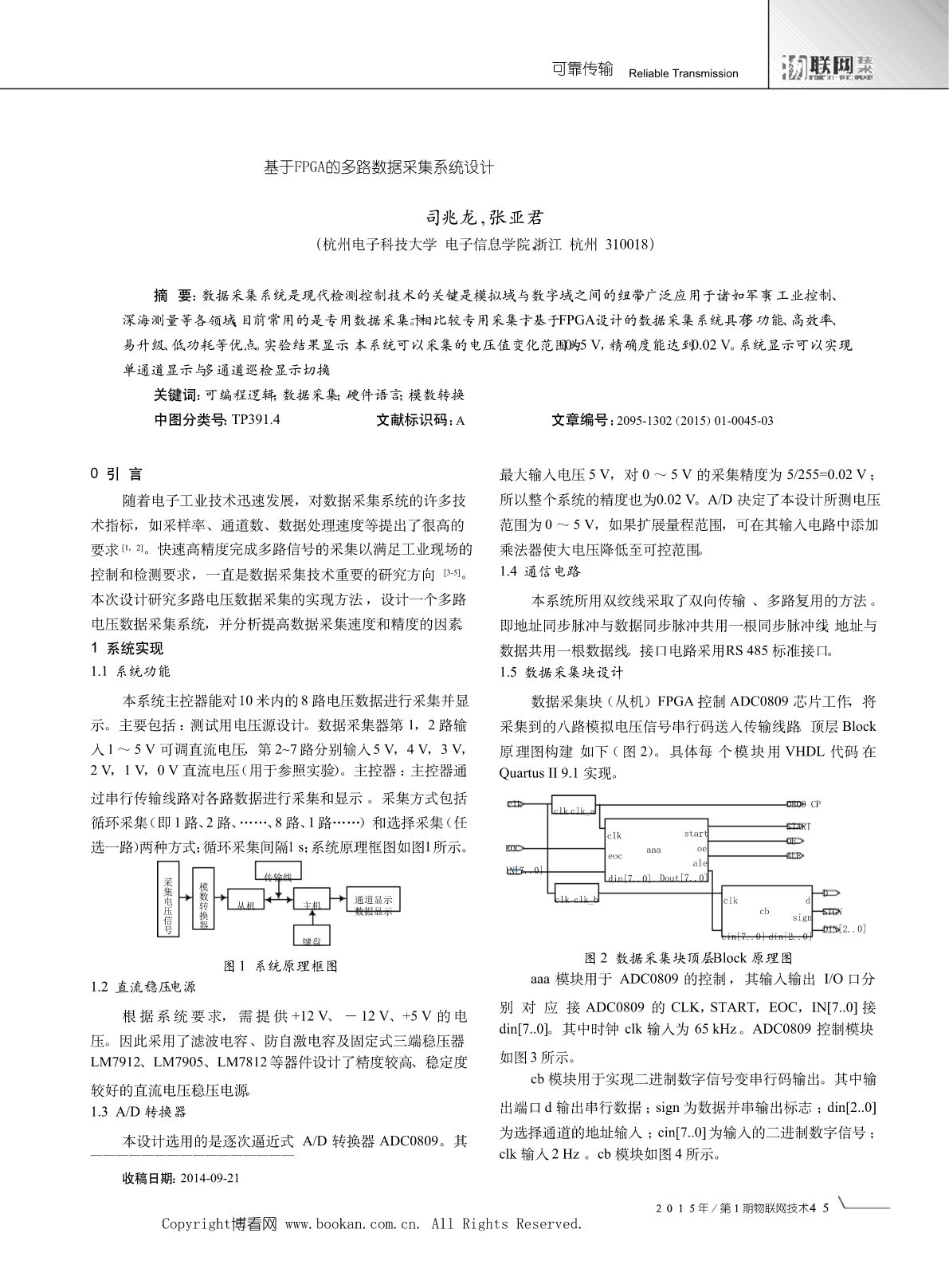

可靠传输ReliableTransmission基于FPGA的多路数据采集系统设计司兆龙,张亚君(杭州电子科技大学电子信息学院,浙江杭州310018)摘要:数据采集系统是现代检测控制技术的关键,是模拟域与数字域之间的纽带,广泛应用于诸如军事、工业控制、深海测量等各领域,目前常用的是专用数据采集卡。相比较专用采集卡,基于FPGA设计的数据采集系统具有多功能、高效率、易升级、低功耗等优点。实验结果显示,本系统可以采集的电压值变化范围为0~5V,精确度能达到0.02V。系统显示可以实现单通道显示与多通道巡检显示

基于FPGA的多路数据采集系统的设计.docx

基于FPGA的多路数据采集系统的设计随着科技的不断发展,数据采集系统在各个领域的应用越来越广泛。在工业控制、医疗监测、环境监测等领域中,多路数据采集系统的需求越来越高。基于FPGA的多路数据采集系统作为高性能时序控制器,具有传输速度快、实时性好、可编程性强等优势,受到越来越多的关注。本文将介绍基于FPGA的多路数据采集系统的设计与实现。一、多路数据采集系统多路数据采集系统是指能够同时采集多个信号并转换为数字信号的系统。在实际应用中,多路数据采集系统往往需要采集的信号种类繁多,对采集的精度、速度、实时性等方

基于FPGA的多路数据采集系统设计.pdf

万方数据基于FPGA的多路数据采集系统设计摘要:介绍了一种基于FPGA的高速多路数据采集系统的设计方案,描述了系统的主要组成及FPGA的实现方法,并用v∞L语言设用f阢A内部集成F1FO作为数据存储过渡的方案,有下《装备制造技术》2009年第12期高可到达40M。使用兀F0就可以充分发挥n施H存储器的陈靓坦,孙运强1’2制了一系列专用存储测试设备IIl。总的来说,国内在大容量存存储模块总体设计方案不会出现这一问题了M。FPGA内部集成FIFo作为数据过渡的设计方案M。(中北大学1.仪器科学与动态测试教育部

基于FPGA的多路数据采集系统设计.docx

基于FPGA的多路数据采集系统设计随着现代科技的不断发展,数据采集技术越来越成熟,数码相机、手机、传感器等设备的广泛应用,给我们带来了大量的数据。但是,这些数据对于我们而言还需要经过处理和分析,才能真正发挥其价值,因此,设计一套基于FPGA的多路数据采集系统显得尤为重要。一、系统架构设计以一个多路数据采集系统为例,该系统主要分为信号采集模块、信号处理模块、存储模块、通信模块四大部分。其中,信号采集模块通过采集多种数据源的信号,生成对应的数字信号,信号处理模块则通过对信号进行滤波、放大、计算等处理,使其符合

基于FPGA的多路光栅数据采集系统.docx

基于FPGA的多路光栅数据采集系统摘要:本篇论文介绍了一种基于FPGA的多路光栅数据采集系统。该系统主要包括三个部分:信号输入模块、数据采集模块和数据处理模块。信号输入模块负责将多路光栅的信号输入到系统中,数据采集模块负责对这些信号进行采样和存储,数据处理模块则对采集到的数据进行分析和处理。整个系统具有高速、高精度和实时性好的特点,非常适合用于机械结构振动分析、光栅测量和其他需要高速数据采集的领域。关键词:FPGA、多路光栅、数据采集、数据处理引言:近年来,随着科学技术的不断发展,各种高速数据采集系统得到