单片微机原理及应用课件_第6章_单片机存储器及系统扩展.ppt

qw****27

亲,该文档总共45页,到这已经超出免费预览范围,如果喜欢就直接下载吧~

相关资料

单片微机原理及应用课件_第6章_单片机存储器及系统扩展.ppt

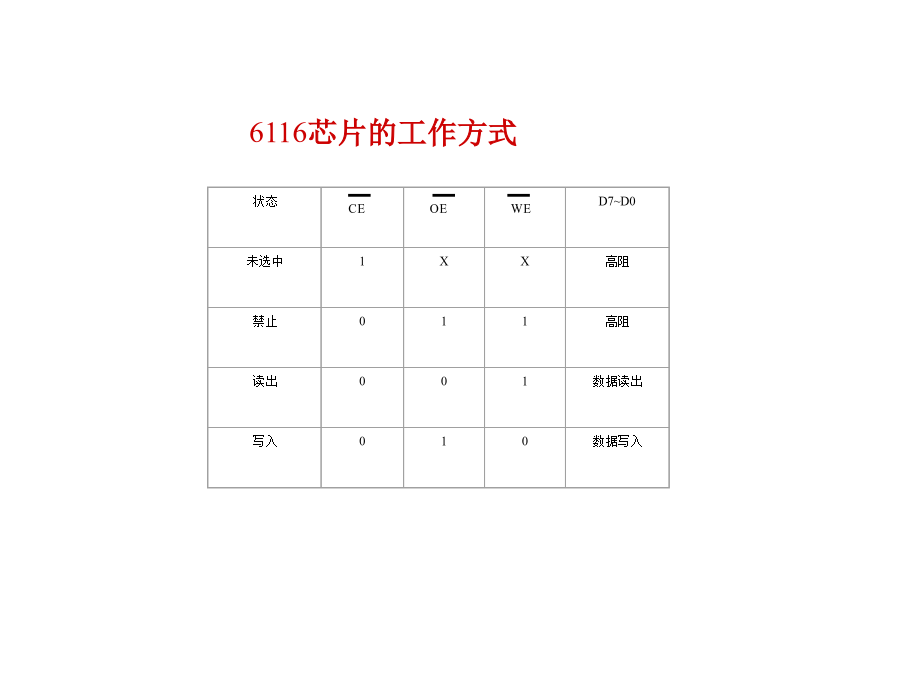

第6章单片机存储器及系统扩展技术6.1半导体存储器的分类一、半导体存储器的分类1、只读存储器(ROM)(1)掩膜工艺ROM(2)可一次性编程ROM(PROM)(3)紫外线擦除可改写ROM(EPROM)(4)电擦除可改写ROM(EEPROM或E2PROM)(5)快擦写ROM(flashROM)Intel公司的27系列产品:2716(2K)2732(4K)2764(8K)27128(16K)随机存储器RAM(也叫读写存储器)(1)双极型RAM(2)金属氧化物(MOS)RAM静态RAM(SRAM);加电即可保

单片微机原理及应用课件_第6章_单片机存储器及系统扩展技术.ppt

第6章单片机存储器及系统扩展技术6.1半导体存储器的分类一、半导体存储器的分类1、只读存储器(ROM)(1)掩膜工艺ROM(2)可一次性编程ROM(PROM)(3)紫外线擦除可改写ROM(EPROM)(4)电擦除可改写ROM(EEPROM或E2PROM)(5)快擦写ROM(flashROM)Intel公司的27系列产品:2716(2K)2732(4K)2764(8K)27128(16K)随机存储器RAM(也叫读写存储器)(1)双极型RAM(2)金属氧化物(MOS)RAM静态RAM(SRAM);加电即可保

单片微机原理及应用课件_第6章_单片机存储器及系统扩展技术1.ppt

第6章单片机存储器及系统扩展技术6.1半导体存储器的分类一、半导体存储器的分类1、只读存储器(ROM)(1)掩膜工艺ROM(2)可一次性编程ROM(PROM)(3)紫外线擦除可改写ROM(EPROM)(4)电擦除可改写ROM(EEPROM或E2PROM)(5)快擦写ROM(flashROM)Intel公司的27系列产品:2716(2K)2732(4K)2764(8K)27128(16K)随机存储器RAM(也叫读写存储器)(1)双极型RAM(2)金属氧化物(MOS)RAM静态RAM(SRAM);加电即可保

单片微机原理及应用课件_第6章_单片机存储器及系统扩展技术2.ppt

第6章单片机存储器及系统扩展技术6.1半导体存储器的分类一、半导体存储器的分类1、只读存储器(ROM)(1)掩膜工艺ROM(2)可一次性编程ROM(PROM)(3)紫外线擦除可改写ROM(EPROM)(4)电擦除可改写ROM(EEPROM或E2PROM)(5)快擦写ROM(flashROM)Intel公司的27系列产品:2716(2K)2732(4K)2764(8K)27128(16K)随机存储器RAM(也叫读写存储器)(1)双极型RAM(2)金属氧化物(MOS)RAM静态RAM(SRAM);加电即可保

单片微机原理及应用课件_第6章_单片机存储器及系统扩展技术3.ppt

第6章单片机存储器及系统扩展技术6.1半导体存储器的分类一、半导体存储器的分类1、只读存储器(ROM)(1)掩膜工艺ROM(2)可一次性编程ROM(PROM)(3)紫外线擦除可改写ROM(EPROM)(4)电擦除可改写ROM(EEPROM或E2PROM)(5)快擦写ROM(flashROM)Intel公司的27系列产品:2716(2K)2732(4K)2764(8K)27128(16K)随机存储器RAM(也叫读写存储器)(1)双极型RAM(2)金属氧化物(MOS)RAM静态RAM(SRAM);加电即可保