具有USB20接口的高速数据采集卡设计.ppt

天马****23

亲,该文档总共21页,到这已经超出免费预览范围,如果喜欢就直接下载吧~

相关资料

具有USB20接口的高速数据采集卡设计.ppt

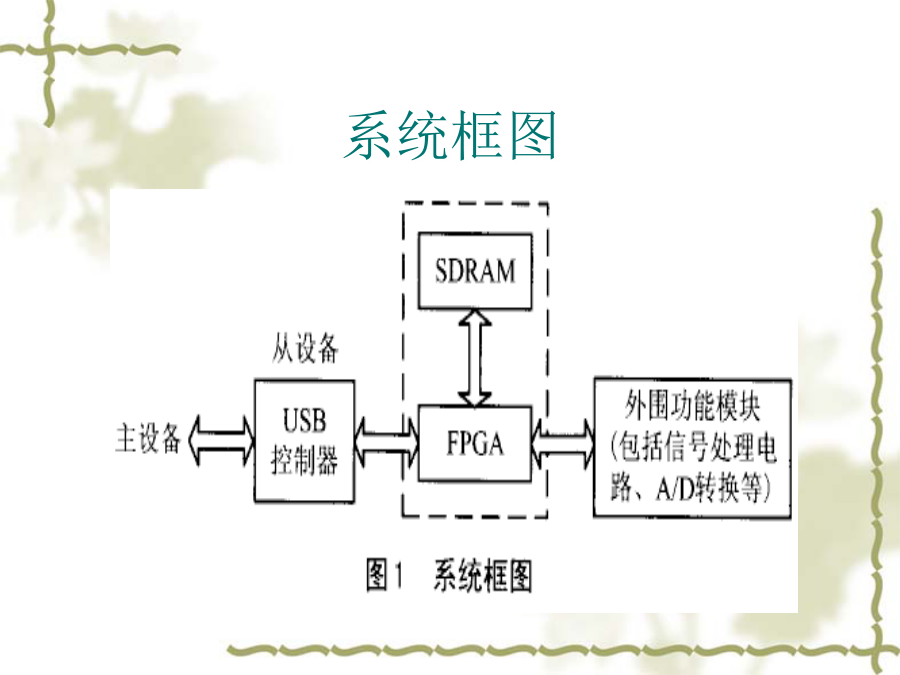

引言系统框图系统框图USB数据采集卡硬件EZ-USBFX2的微处理器是一个增强型的8051内核,性能可达标准8051的5~10倍,并与标准8051的指令完全兼容。增强型的8051内核使用RAM世馘作程序指令和数据存储器,从而使得EZ-USBFX2具有“软”特性,也就是说,可以通过自行编写程序指令来实现所需的功能。EZ-USBFZ2使用增强型SIE/USB接口(称为USB核),通过执行USB部本身的协议来简化8051代码编写的工作。这样采用硬件完成USB塄,简化了固件代码的编制。对于固件代码的使用,主机通过

USB接口的高速数据采集卡的设计与实现.docx

USB接口的高速数据采集卡的设计与实现USB接口的高速数据采集卡的设计与实现摘要:讨论了基于USB接口的高速数据采集卡的实现。该系统采用TI公司的TUSB3210芯片作为USB通信及主控芯片,完全符合USB1.1协议,是一种新型的数据采集卡。 关键词:USBA/DFIFO固件现代工业生产和科学研究对数据采集的要求日益提高,在瞬态信号测量、图像处理等一些高速、高精度的测量中,需要进行高速数据采集。现在通用的高速数据采集卡一般多是PCI卡或ISA卡,存在以下缺点:安装麻烦;价

USB接口的高速数据采集卡的设计与实现.docx

USB接口的高速数据采集卡的设计与实现摘要:讨论了基于USB接口的高速数据采集卡的实现。该系统采用TI公司的TUSB3210芯片作为USB通信及主控芯片,完全符合协议,是一种新型的数据采集卡。关键词:USBA/DFIFO固件现代工业生产和科学研究对数据采集的要求日益提高,在瞬态信号测量、图像处理等一些高速、高精度的测量中,需要进行高速数据采集。现在通用的高速数据采集卡一般多是PCI卡或ISA卡,存在以下缺点:安装麻烦;价格昂贵;受计算机插槽数量、地址、中断资源限制,可扩展性差;在一些电磁干扰性强的测试现场

基于USB20总线的高速数据采集系统设计.docx

基于USB2.0总线的高速数据采集系统设计摘要:本文主要介绍支持高速传输的EZ-USBFX2单片机CY7C68013,并详细说明用此芯片实现高速数据采集系统和相应的Windows驱动程序及底层固件程序的开发过程。关键词:数据采集固件1引言现代工业生产和科学研究对数据采集的要求日益提高,在瞬态信号测量、图像处理等一些高速、高精度的测量中,需要进行高速数据采集。现在通用的高速数据采集卡一般多是PCI卡或ISA卡,存在以下缺点:安装麻烦、价格昂贵;受计算机插槽数量、地址、中断资源限制,可扩展性差;在一些电磁干扰

PC在高速数据采集卡设计中的应用.docx

PC在高速数据采集卡设计中的应用随着科技的快速进步和应用领域的不断扩大,高速数据采集卡在工业自动化、科学研究、医疗诊断以及视频监控等领域中得到了广泛的应用。而PC作为目前应用最为广泛的计算机平台,其在高速数据采集卡设计中也起到了重要的作用。首先,PC作为高速数据采集卡的控制中心,具有强大的处理能力和存储容量,能够满足不同应用场景下的数据处理需求。在高速数据采集卡设计中,PC可以通过PCI、PCIe和USB等接口与采集卡进行连接,实现数据的高速传输和实时处理。同时,基于PC的软件平台可以将采集卡的数据进行更