基于FPGA的FIR滤波器设计.ppt

yy****24

亲,该文档总共16页,到这已经超出免费预览范围,如果喜欢就直接下载吧~

相关资料

基于FPGA的FIR滤波器设计.docx

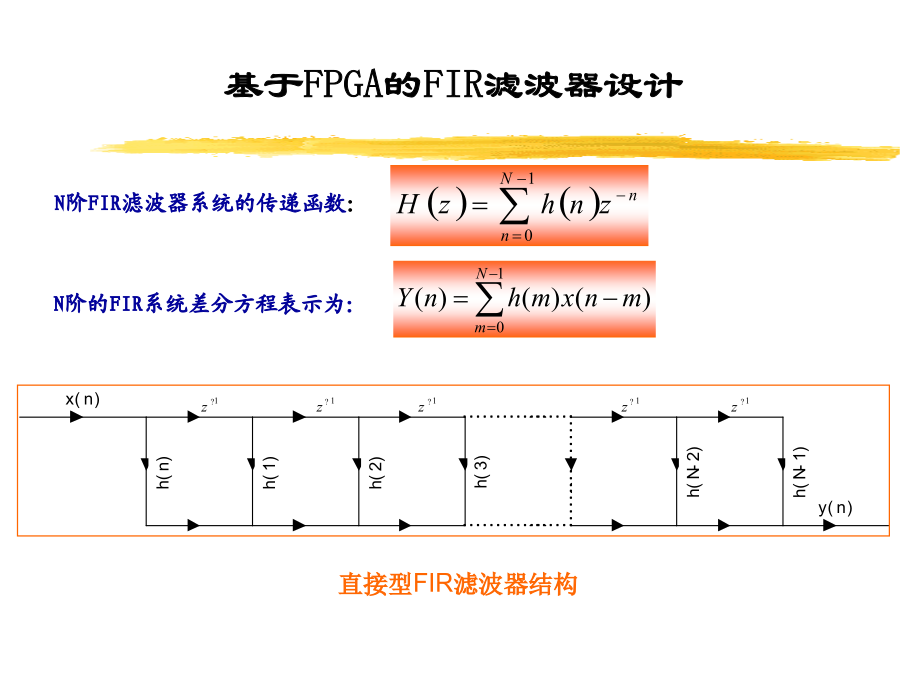

基于FPGA的FIR滤波器设计周剑敏+谢文雷+葛斌+陈虞苏摘要介绍了基于FPGA芯片进行FIR滤波器的设计过程,具体涉及到MATLAB对FIR滤波器的仿真、数据的量化和生成;FPGA对FIR滤波器的设计、仿真和数据生成,最后形成FPGA和MATLAB联合设计FIR滤波器。关键词FGPA;FIR;MATLAB中图分类号:TN911文献标识码:A文章编号:1671-7597(2014)03-0034-01滤波器在信息领域应用非常广泛。随着现代技术的发展,如何在FPGA上进行滤波器设计是非常迫切的。FPGA是通

基于FPGA的FIR滤波器设计.doc

---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------

基于FPGA的FIR滤波器设计.ppt

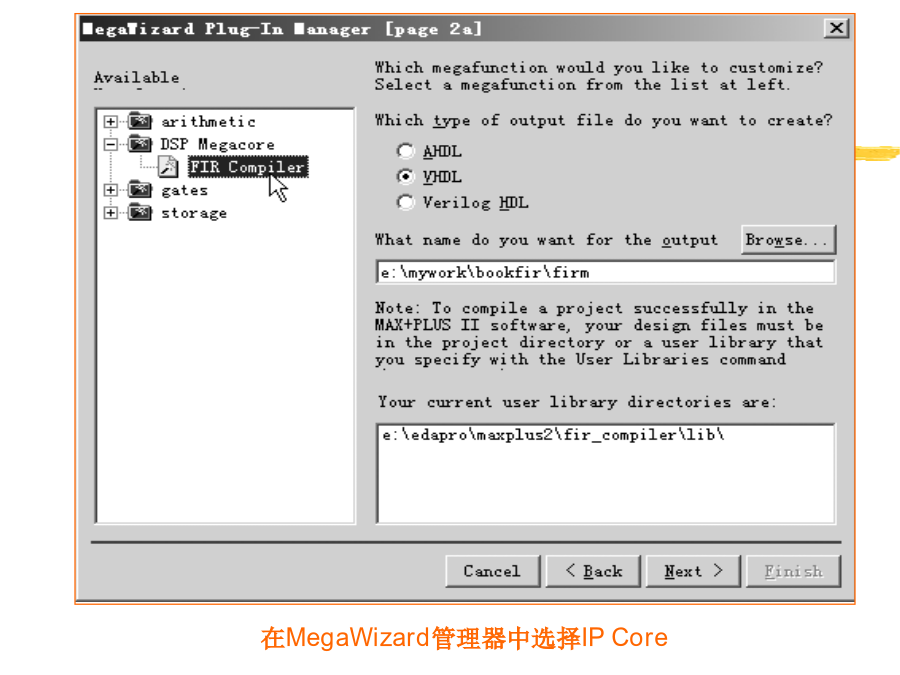

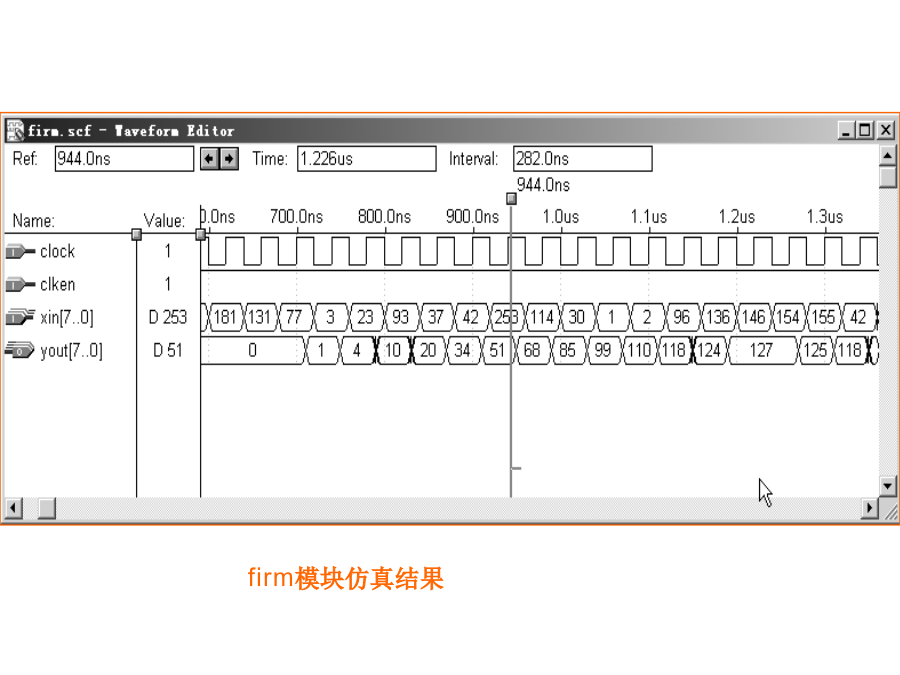

基于FPGA的FIR滤波器设计乘法器FIRCompiler安装设置UserLibraries在MegaWizard管理器中选择IPCoreFIR滤波器系数确定firm模块仿真结果借助Matlab设计滤波器系数滤波器的幅频响应typefactor_typeisarray(0to59)ofinteger;--定义长度为60的整型数组用于存放滤波器系数typereg_typeisarray(0to59)ofstd_logic_vector(9downto0);--定义长度为60的寄存器组,用于存放60级的延迟信

基于FPGA的FIR滤波器设计.docx

基于FPGA的FIR滤波器设计一、设计目的为了帮助学生深入理解和消化基本理论、进一步提高综合应用能力并且锻炼独立解决问题的能力,我们将《数字信号处理》、《集成电路原理与应用》和《《FPGA系统设计与应用》几门课程融合在一起开设的FPGA综合实验课程设计。本次完成的是利用FPGA来完成FIR滤波器的设计、程序设计和实验调试任务。二、设计要求(1)基本要求利用所学知识,采用VHDL语言完成FIR滤波器的设计仿真。要求用VHDL编程设计底层文件,顶层文件可任意(可用原理图方式或文本方式);完成仿真文件(包括MA

基于FPGA的FIR滤波器的设计.docx

基于FPGA的FIR滤波器的设计概述FIR滤波器是一种数字滤波器,它使用有限长的冲激响应滤波器(FIR)函数来滤波信号。FIR滤波器具有线性相位响应和最大通带响应。在本文中,我们将探讨基于FPGA的FIR滤波器设计。该设计具有很高的灵活性,能够适应多种不同类型的信号处理应用,性能稳定可靠。设计原理FPGA的FIR滤波器设计是基于数学原理和硬件设计技术的。在FIR滤波器中,输入信号与一组加权系数的卷积是所需的输出信号。这些加权系数是在FIR滤波器设计过程中确定的。硬件设计技术是通过将数字信号处理算法实现为硬