高速串行总线RapidIO与PCI+Express协议分析比较.pdf

qw****27

在线预览结束,喜欢就下载吧,查找使用更方便

相关资料

高速串行总线RapidIO与PCI+Express协议分析比较.pdf

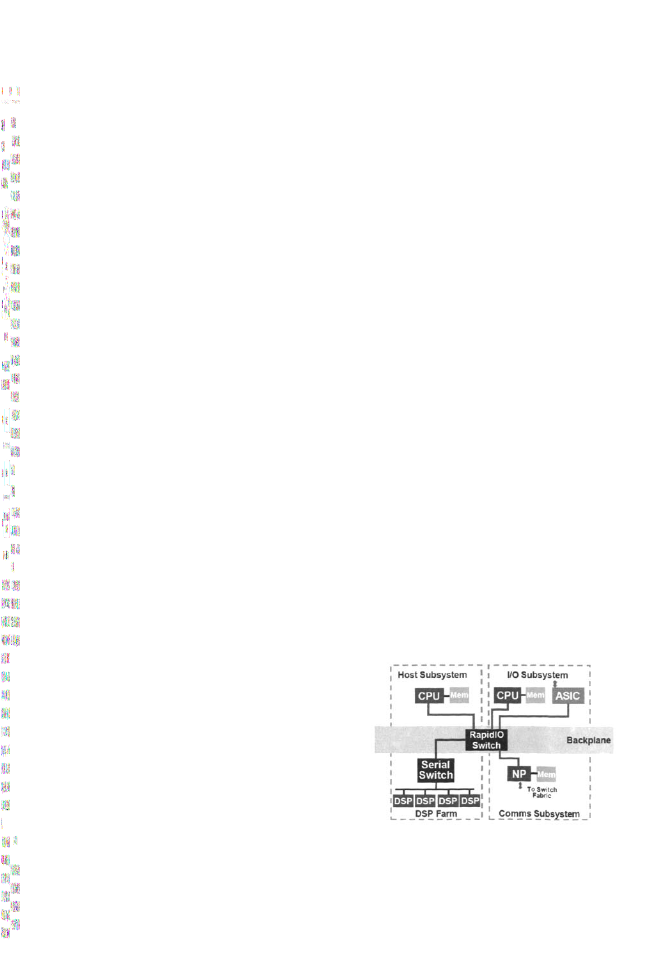

万方数据釜壕样<1⋯KB熊蓉⋯旒g眦rog特征蓑篓袭蓥⋯用.熊蓉羹鏊詈Express协议分析比较高速串行总线RapidlO与PCI梁小虎,王乐,张亚棣引言行总线标准。因此,对二者进行详细的分析比较,充分1基本性能比较(中国航空计算技术研究所,陕西西安710068)随着嵌入式系统的不断发展,对高性能的要求不断强化,更先进的处理器架构和高速缓存的出现,使处理器的性能得到很大提高,但是,处理器总线频率的增长速度相对于处理器的发展相差很大。处理器速率的增加虽然可以提升系统的数据处理速度,但是却无助于提升处理器与其

高速串行总线RapidIO与PCI Express技术分析比较.docx

高速串行总线RapidIO与PCIExpress技术分析比较高速串行总线RapidIO和PCIExpress都是用于在计算机系统中实现高速数据传输的常用技术,但是它们的实现方式和特性有所不同。本文将分析这两种技术的特点、应用场景和性能方面的比较。1.RapidIO技术简介RapidIO是一种针对高端通信和计算应用的串行总线技术。它提供了高带宽、低延迟和高可靠性的数据传输,被广泛用于嵌入式系统、网络通信和高性能计算中。在RapidIO中,数据通过分组传输方式进行传输,每个分组的大小通常为128字节,数据包括

RapidIO高速串行总线的研究与实现的任务书.docx

RapidIO高速串行总线的研究与实现的任务书任务书1.任务背景随着信息技术的迅猛发展,现代计算机系统逐渐向多核、多处理器方向发展,这些处理器需要高速、低延迟、可扩展的互连方式来保证系统的性能。传统的互连方式,如PCI和PCIExpress,已无法满足高速数据交换和低延迟的要求。而RapidIO高速串行总线,以其高速、可扩展和低延迟的特点,逐渐成为了现代计算机系统的首选互连方式。2.任务目标本项目的目标是研究和实现RapidIO高速串行总线,包括以下内容:(1)了解RapidIO总线的基本原理、架构和协议

高速串行总线信号完整性分析.docx

高速串行总线信号完整性分析高速串行总线信号完整性分析引言随着电子产品的普及和科技的不断发展,高速串行总线在现代计算机和通信系统中扮演着重要的角色。高速串行总线允许数据在系统内部和系统之间高速传输,从而提高了数据传输的效率。然而,在高速传输过程中,信号完整性成为一个重要且复杂的问题。信号完整性的保持对于系统的可靠性和稳定性非常关键。本论文将重点讨论高速串行总线信号完整性的分析。一、高速串行总线的概述高速串行总线是一种用于数据传输的通信接口,它使用一条线路上的连续的位串来传输数据。相比于并行总线,高速串行总线

基于Sigrity的高速串行总线GTX仿真分析.docx

基于Sigrity的高速串行总线GTX仿真分析基于Sigrity的高速串行总线GTX仿真分析摘要:高速串行总线在计算机通信领域中扮演着重要的角色,针对其信号完整性和设计可靠性问题的研究成为了热点。本文基于Sigrity仿真工具,对高速串行总线GTX进行了仿真分析。首先,针对GTX的基本特征和工作原理进行了简要介绍。接着,介绍了Sigrity仿真工具的基本原理和使用方法。然后,对GTX进行了电气仿真和时域仿真,分析了其信号完整性和时钟抖动问题,进一步优化了其设计。最后,对仿真结果进行了分析和讨论,并给出了后