基于NiosII的数字图像采集及处理.doc

kp****93

在线预览结束,喜欢就下载吧,查找使用更方便

相关资料

基于NiosII的数字图像采集及处理.doc

基于NiosII的数字图像处理—《数字图象处理》课程论文院系班级姓名学号2010.10.20基于NiosII的数字图像采集及处理摘要:本文是以NiosII软核CPU为核心处理器,在FPGA中构建SOPC,实现原来主要由DSP完成图像处理和图像显示控制,简化了硬件电路和软件程序的设计。系统采用软核CPU、DSP软模块、FPGA以及数字视频技术。从数字摄像头输入视频信号,据经视频解码芯片输出送至FPGA中,通过时序控制和NiosIIII软核把视频解码数据依序存储在SSRAM中,并进行裁剪、交织、颜色处理。最后

基于DSP的数字图像处理设计.doc

基于DSP的数字图像处理设计DSP一方面是DigitalSignalProcessing的缩写,意思是数字信号处理,就是指数字信号理论研究。DSP另一方面是DigitalSignalProcessor,意思是数字信号处理器,就是用来完成数字信号处理的器件。DSP的发展概况最初的DSP器件只是被设计成用以完成复杂数字信号处理的算法。DSP器件紧随着数字信号理论的发展而不断发展。在20世纪60年代,数字信号处理技术才刚刚起步。60年代中期以后,快速傅里叶算法的出现及大规模集成电路的发展大大促进了DSP技术与器

基于DSP的数字图像处理设计.doc

基于DSP的数字图像处理设计DSP一方面是DigitalSignalProcessing的缩写,意思是数字信号处理,就是指数字信号理论研究。DSP另一方面是DigitalSignalProcessor,意思是数字信号处理器,就是用来完成数字信号处理的器件。DSP的发展概况最初的DSP器件只是被设计成用以完成复杂数字信号处理的算法。DSP器件紧随着数字信号理论的发展而不断发展。在20世纪60年代,数字信号处理技术才刚刚起步。60年代中期以后,快速傅里叶算法的出现及大规模集成电路的发展大大促进了DSP技术与器

基于Matlab的数字图像增强处理.pdf

目录摘要........................................................................................................................1第一章绪论..........................................................................................................11.1课题研究目的及意义......

基于Labview的图像采集与处理.docx

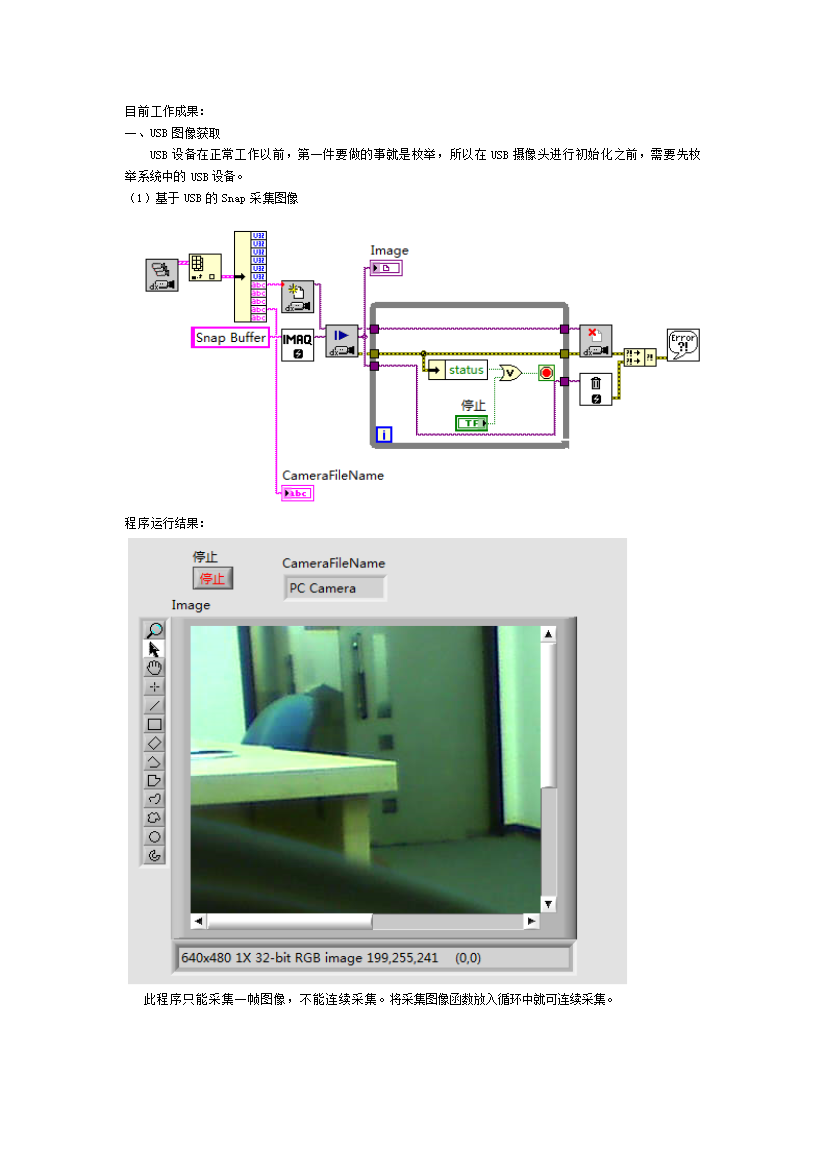

目前工作成果:一、USB图像获取USB设备在正常工作以前第一件要做的事就是枚举所以在USB摄像头进行初始化之前需要先枚举系统中的USB设备。(1)基于USB的Snap采集图像程序运行结果:此程序只能采集一帧图像不能连续采集。将采集图像函数放入循环中就可连续采集。循环中的可以计算循环一次所用的时间运行发现用Snap采集图像时它的采集速率比较低。运行程序时移动摄像头可以清楚的看到所采集的图像有时比较模糊。(2)基于USB的Grab采集图像运行程序之后发现摄像头采集图像的速率明显提高。二、图像处理图像灰