第5讲VHDL语言要素1.ppt

kp****93

亲,该文档总共42页,到这已经超出免费预览范围,如果喜欢就直接下载吧~

相关资料

第5讲VHDL语言要素1.ppt

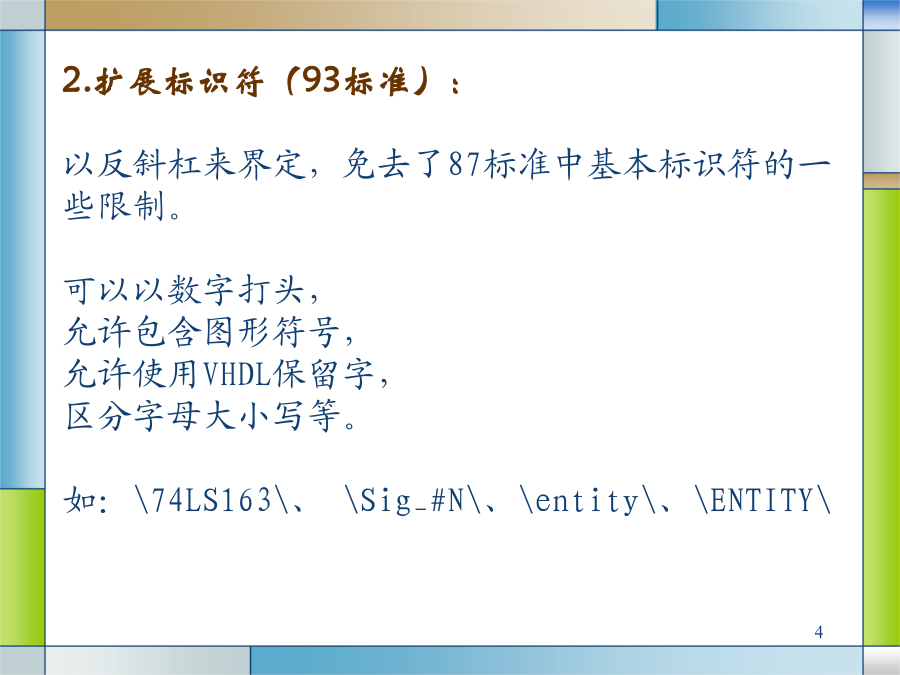

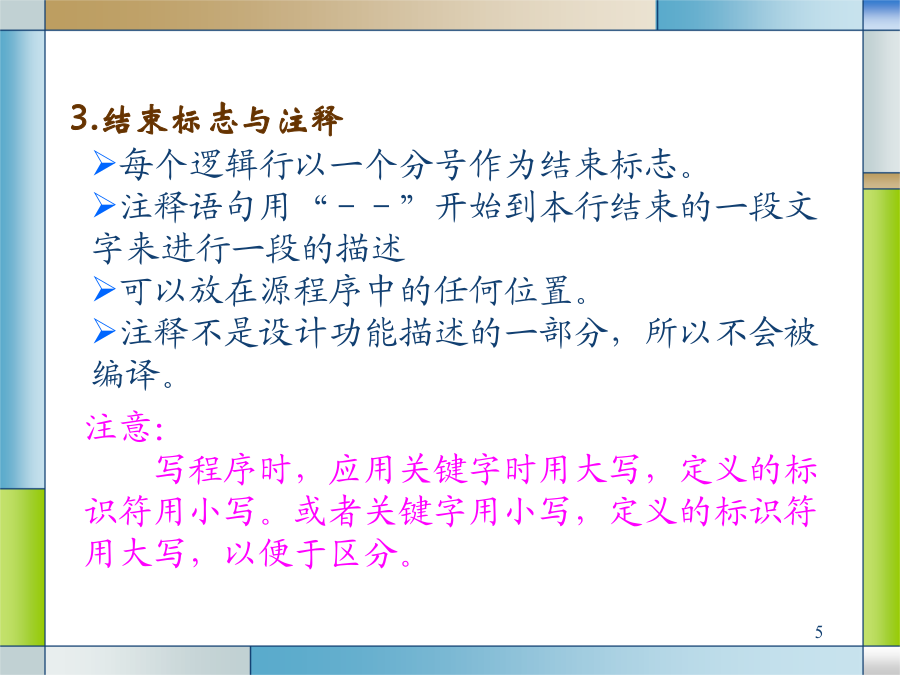

第5讲VHDL语言要素(1)VHDL语言要素有效的字符:包括26个大小写英文字母,数字包括0~9以及下划线“_”任何标识符必须以英文字母开头下划线“_”的前后必须有英文字母或数字标识符中的英语字母不分大小写标识符的命名不能与保留字(关键字)相同2.扩展标识符(93标准):以反斜杠来界定,免去了87标准中基本标识符的一些限制。可以以数字打头,允许包含图形符号,允许使用VHDL保留字,区分字母大小写等。如:\74LS163\、\Sig_#N\、\entity\、\ENTITY\注意:写程序时,应用关键字时用大

第2讲VHDL程序基本结构及语言要素.ppt

第二讲VHDL程序基本结构及语言要素课题:VHDL程序基本结构及语言要素1.VHDL简介VHDL的英文全名是Very-High-SpeedIntegratedCircuitHardwareDescriptionLanguage,诞生于1982年。1987年底,VHDL被IEEE和美国国防部确认为标准硬件描述语言。自IEEE公布了VHDL的标准版本(IEEE-1076)之后,各EDA公司相继推出了自己的VHDL设计环境,或宣布自己的设计工具可以和VHDL接口。此后VHDL在电子设计领域得到了广泛的接受,并逐

第3章 VHDL的语言要素.ppt

本章内容提要VHDL的标识符数据对象数据类型运算操作符3.1VHDL的标识符VHDL基本标识符的命名必须遵循如下规则:基本标识符由字母、数字和下划线组成第一个字符必须是字母最后一个字符不能是下划线不允许连续2个下划线保留字(关键字)不能用于标识符大小写是等效的下面是合法的标识符:Decoder_1,fft,sig_N,state,aaa扩展标识符用反斜杠来界定,可以以数字打头;例:\74ls173\,\controller_docode\都是合法的标识符允许包含图形符号和空格;例:\$500&T\,\AO

VHDL语言要素.ppt

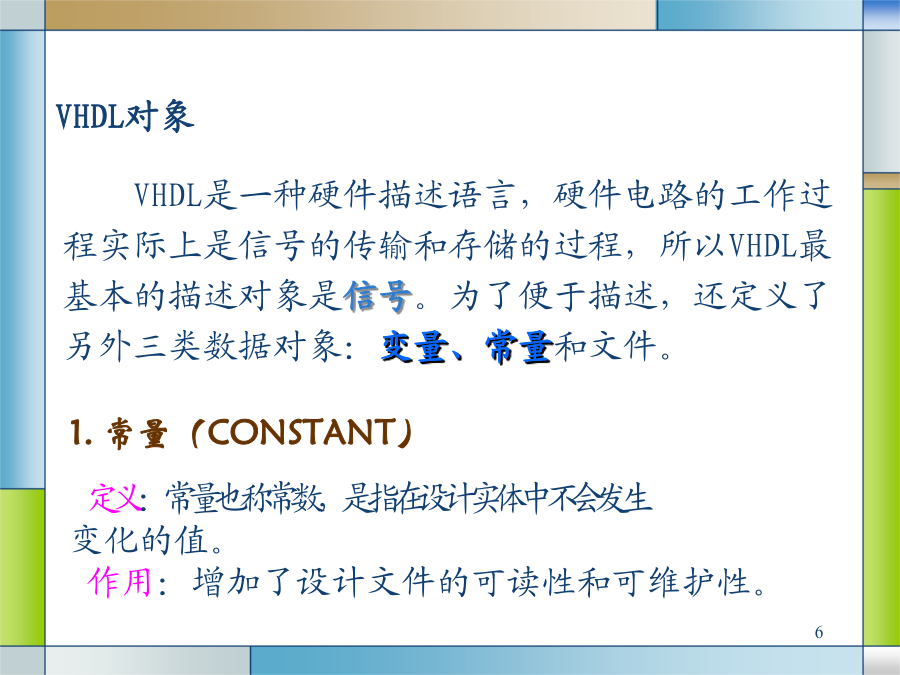

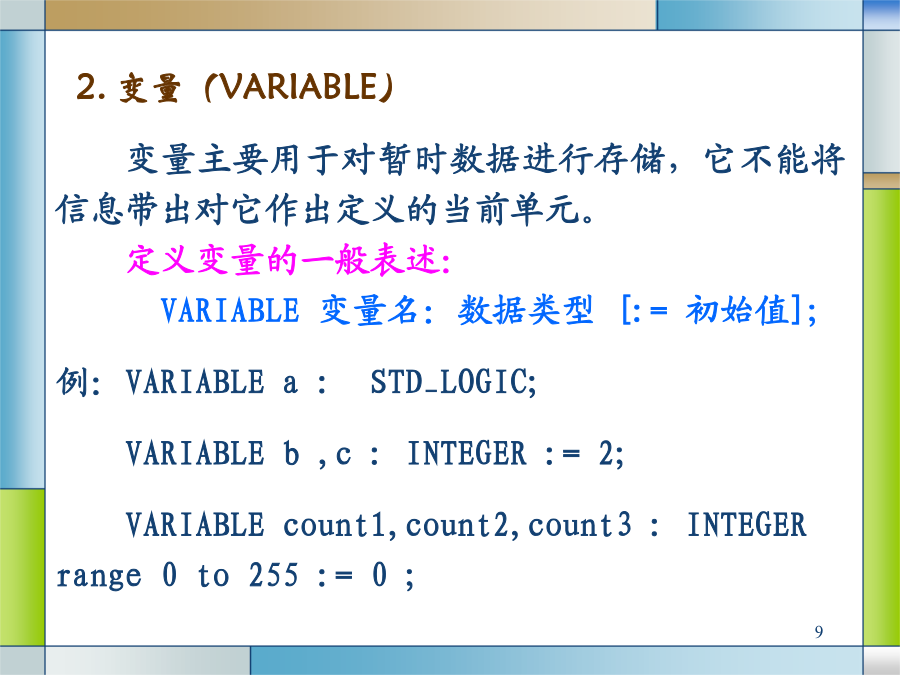

VHDL语言要素第三讲要点回顾标识符标识符数据对象常量变量信号信号信号赋初值注意信号与变量区别数据类型标准数据类型标准数据类型标准数据类型标准数据类型标准数据类型IEEE定义的逻辑位与矢量注意用户自定义的数据类型枚举类型的声明用户自定义的数据类型用户自定义的数据类型用户自定义的数据类型用户自定义的数据类型记录(RECODE)类型记录(RECODE)类型数据类型的转换函数VHDL属性VHDL属性数值类属性数值类属性数值类属性函数类属性EVENTEVENTEVENT和ACTIVE范围类属性运算符逻辑运算符逻辑

VHDL语言要素.ppt

第四章VHDL语言要素4.1VHDL文字规则1、数字型文字整数常规表示:5,678,1254,23_467_154(23467154)科学记数法表示:5E1,678E2(67800)数基表示法……signald1,d2,d3,d4,d5:integerrange0to255;d1〈=10#170#;--十进制表示,等于170d2〈=16#FE#;--十六进制表示,等于254d3〈=2#1111_1110#;--二进制表示,等于254d4〈=8#376#;--八进制表示,等于254d5〈=16#E#E1;-