CPLD技术及其应用1.ppt

kp****93

亲,该文档总共47页,到这已经超出免费预览范围,如果喜欢就直接下载吧~

相关资料

CPLD技术及其应用1.ppt

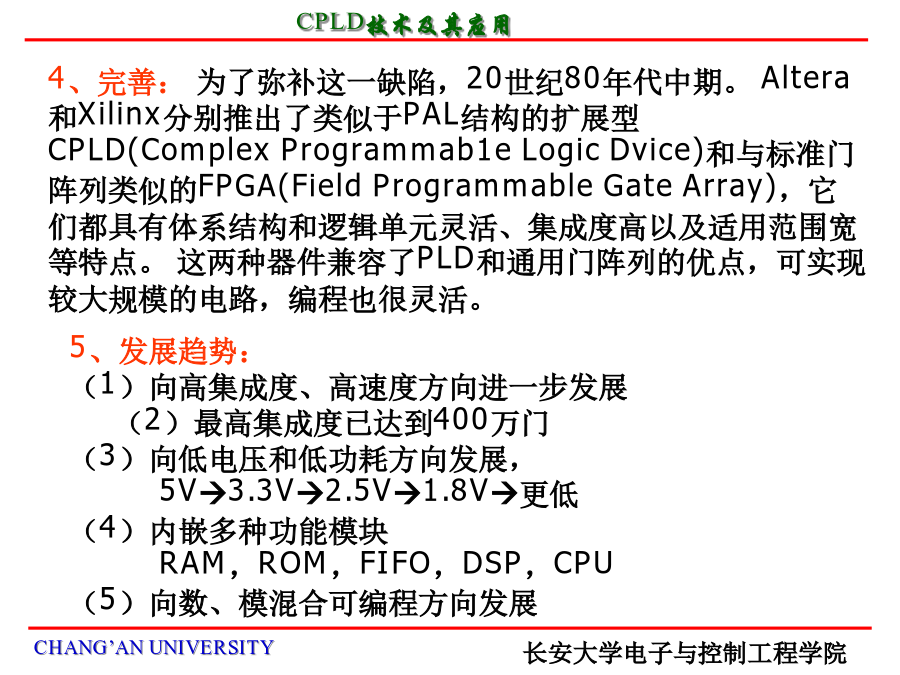

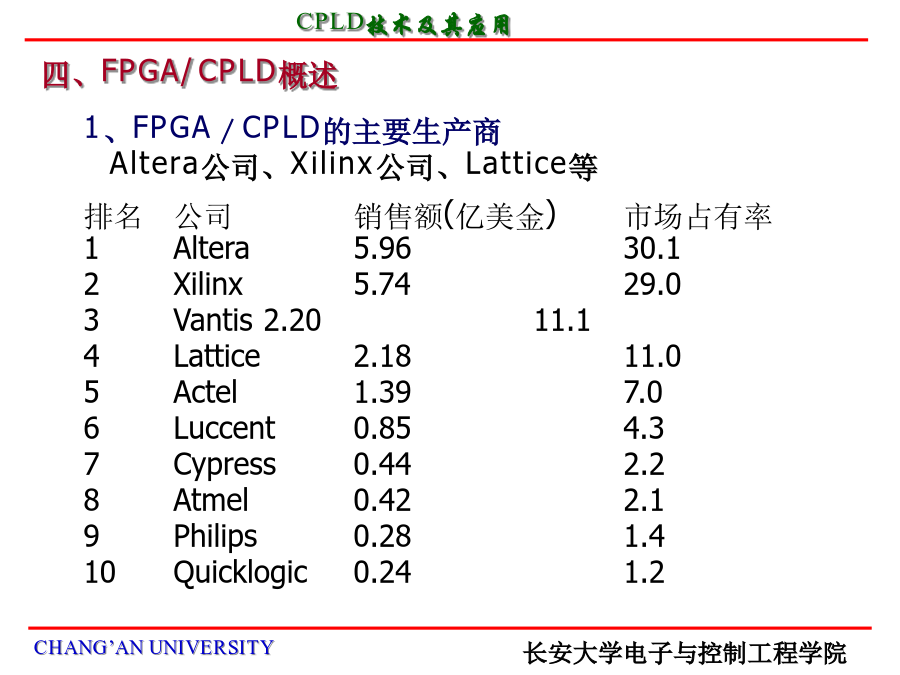

李登峰主要内容一、什么是CPLD?现场可编程门阵列:FPGA(FieldProgrammableGateArray)1、集成度高,可以替代多至几千块通用IC芯片2、极大减小电路的面积,降低功耗,提高可靠性3、具有完善先进的开发工具4、提供语言、图形等设计方法,十分灵活5、通过仿真工具来验证设计的正确性6、可以反复地擦除、编程,方便设计的修改和升级7、灵活地定义管脚功能,减轻设计工作量,缩短系统开发时间8、保密性好三、可编程逻辑器件的发展历史4、完善:为了弥补这一缺陷,20世纪80年代中期。Altera和X

单片机CPLD及其应用实验设备选型.docx

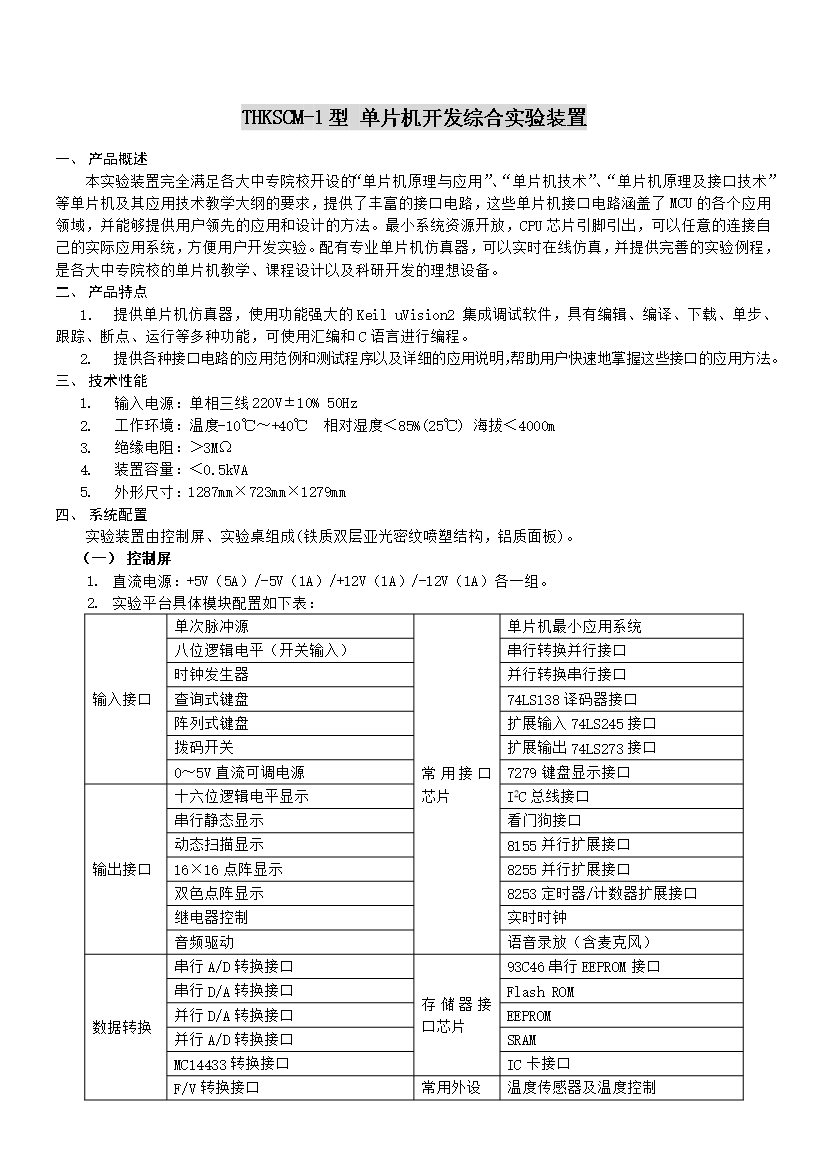

THKSCM-1型单片机开发综合实验装置产品概述本实验装置完全满足各大中专院校开设的“单片机原理与应用”、“单片机技术”、“单片机原理及接口技术”等单片机及其应用技术教学大纲的要求提供了丰富的接口电路这些单片机接口电路涵盖了MCU的各个应用领域并能够提供用户领先的应用和设计的方法。最小系统资源开放CPU芯片引脚引出可以任意的连接自己的实际应用系统方便用户开发实验。配有专业单片机仿真器可以实时在线仿真并提供完善的实验例程是各大中专院校的单片机教学、课程设计以及科研开发的理想设备。产品特点提供单片机仿真器使

单片机CPLD及其应用实验设备选型.docx

单片机·CPLD/FPGA及其应用系列天煌科技天煌教仪THKSCM-1型单片机开发综合实验装置产品概述本实验装置完全满足各大中专院校开设的“单片机原理与应用”、“单片机技术”、“单片机原理及接口技术”等单片机及其应用技术教学大纲的要求,提供了丰富的接口电路,这些单片机接口电路涵盖了MCU的各个应用领域,并能够提供用户领先的应用和设计的方法。最小系统资源开放,CPU芯片引脚引出,可以任意的连接自己的实际应用系统,方便用户开发实验。配有专业单片机仿真器,可以实时在线仿真,并提

单片机CPLD及其应用实验设备选型.docx

单片机·CPLD/FPGA及其应用系列天煌科技天煌教仪THKSCM-1型单片机开发综合实验装置产品概述本实验装置完全满足各大中专院校开设的“单片机原理与应用”、“单片机技术”、“单片机原理及接口技术”等单片机及其应用技术教学大纲的要求,提供了丰富的接口电路,这些单片机接口电路涵盖了MCU的各个应用领域,并能够提供用户领先的应用和设计的方法。最小系统资源开放,CPU芯片引脚引出,可以任意的连接自己的实际应用系统,方便用户开发实验。配有专业单片机仿真器,可以实时在线仿真,并提

单片机CPLD及其应用实验设备选型.doc

单片机·CPLD/FPGA及其应用系列102天煌科技天煌教仪THKSCM-1型单片机开发综合实验装置产品概述本实验装置完全满足各大中专院校开设的“单片机原理与应用”、“单片机技术”、“单片机原理及接口技术”等单片机及其应用技术教学大纲的要求提供了丰富的接口电路这些单片机接口电路涵盖了MCU的各个应用领域并能够提供用户领先的应用和设计的方法。最小系统资源开放CPU芯片引脚引