微机原理 第五章.ppt

kp****93

亲,该文档总共40页,到这已经超出免费预览范围,如果喜欢就直接下载吧~

相关资料

微机原理第五章.ppt

微机原理及应用CODE_SEGSEGMENT;定义作为代码段的逻辑段ASSUMECS:CODE_SEG,DS:DATA_SEG,SS:STACK_SEGSTART:MOVAX,DATA_SEG;程序执行起始点为STARTMOVDS,AX;将段寄存器指向用户数据段MOVAX,STACK_SEGMOVSS,AX;将堆栈指针指向用户定义堆栈MOVSP,OFFSETTOPLEADX,STRINGMOVAH,9;系统功能调用,在CRT显示字符串INT21HMOVAH,4CH;系统功能调用,程序结束返回操作系统INT

微机原理 第五章.ppt

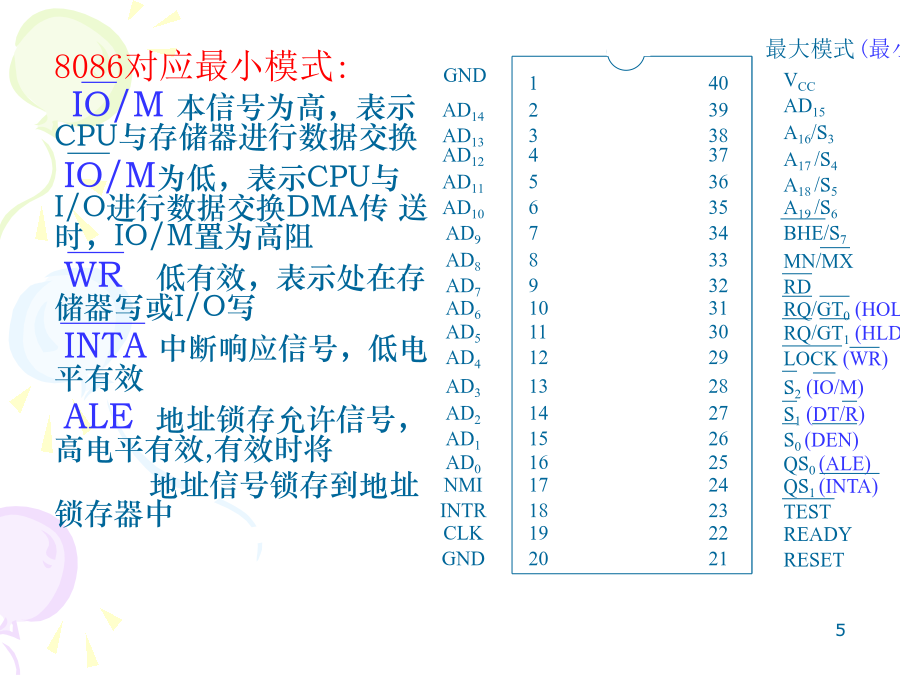

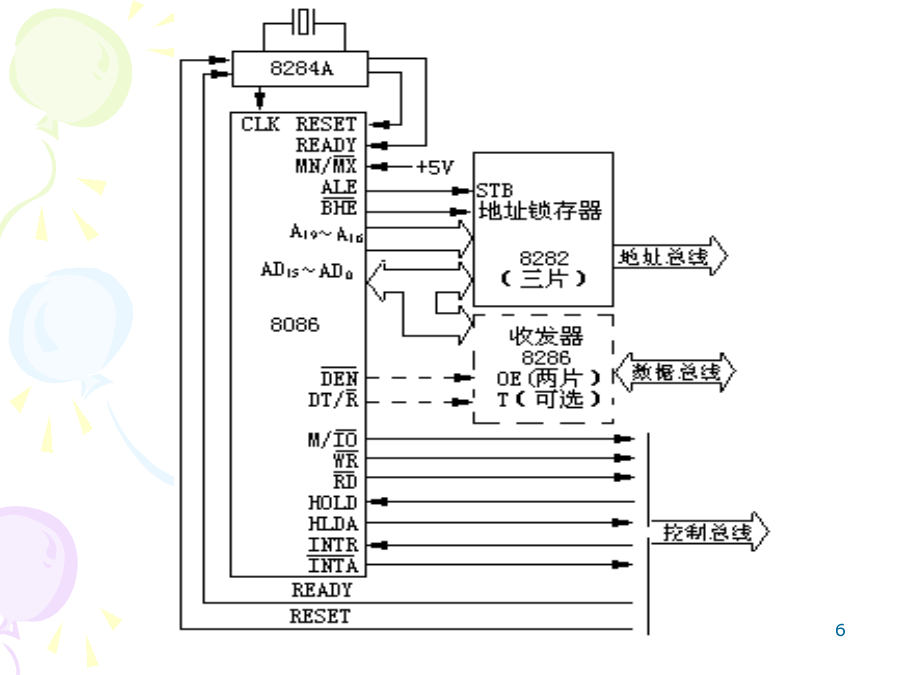

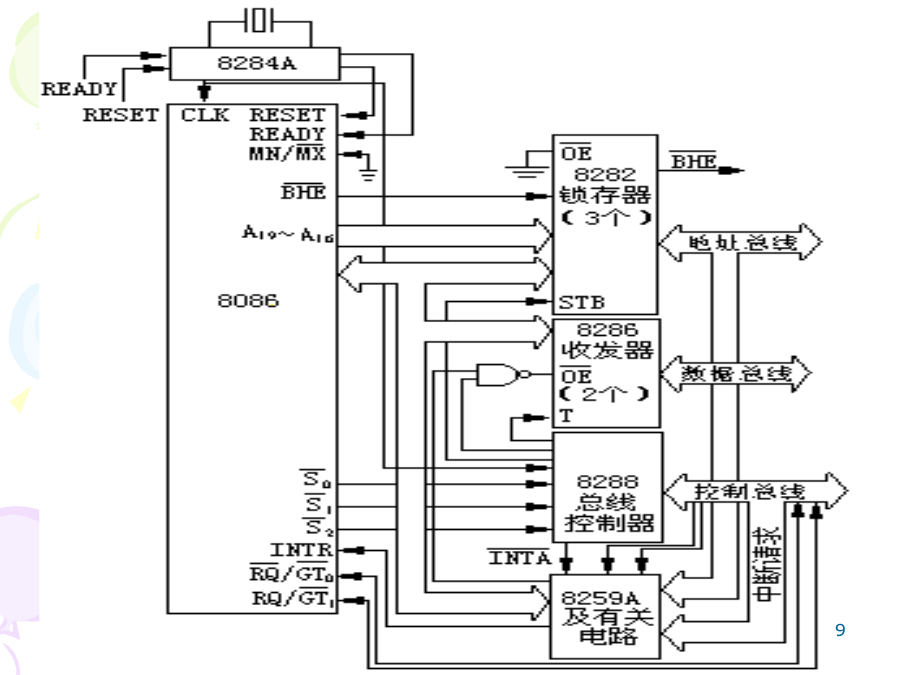

第五章处理器硬件特性(总线时序和系统总线)8088的两种模式最小模式:系统中只有一片8088,其存储容量不大,所要连的I/O端口也不多,总线控制逻辑电路被减到最小。最大模式:构成的系统较大,可能包含不只一片微处理器,或要求有较强的驱动能力,带有一个总线控制器8288。8088的引脚和功能8086的引脚和功能8086对应最小模式:IO/M本信号为高,表示CPU与存储器进行数据交换IO/M为低,表示CPU与I/O进行数据交换DMA传送时,IO/M置为高阻WR低有效,表示处在存储器写或I/O写INTA中断响应信

微机原理第五章.pptx

第五章指令系统(1)第五章指令系统(2)第五章指令系统(3)第五章指令系统(4)第五章指令系统(5)第五章指令系统(6)第五章指令系统(7)第五章指令系统(8)第五章指令系统(9)方案A:方案B:第五章指令系统(13)第五章指令系统(14)第五章指令系统(15)第五章指令系统(16)第五章指令系统(17)第五章指令系统(18)第五章指令系统(19)第五章指令系统(20)第五章指令系统(21)第五章指令系统(22)第五章指令系统(23)第五章指令系统(24)第五章指令系统(25)第五章指令系统(26)第五章

微机原理第五章总结.doc

微机原理--第五章2015/1/9Fio出版※为重点1.总线的概念、分类、总线标准名称1)数字计算机是由若干个部件组成的,这些部件间的信息交换是通过一组公共的标准线路进行的,这组用来进行信息传送的公用线路,称为总线。2)按总线在计算机系统中的位置:片内总线、系统总线、设备总线按传输信息的内容:地址总线、数据总线和控制总线(数据总线的根数(位数)与计算机的字长相同。属单向传输,其位数与存储容量有关。)3)ISA总线即工业标准总线、MCA总线即微通道总线、EISA总线、PCI总线即时钟同步型输入/输出总线IO

微机原理 第五章(DMA).ppt

直接存贮器存取(DMA)技术AB三.应用:常用于I/O设备与M之间有大的数据块交换、且有高的速度要求的场合。如:海量存储器(硬盘)与M之间的信息交换。一、主动态:接管并取得总线控制权,取代CPU而成为系统的主控者。DMAC通过三总线向M或I/O发出地址码及读/写信号,以控制M和I/O设备之间的数据传送。“写入”—有CPU向M中写入的含义,但是是I/O向其写入:DMA写操作:—MI/O—写操作DMAC发控制信号MEMW信号MDMAC发控制信号IOR信号I/OCPU对DMAC进行初始化操作内容包括:通道的选择