可编程串行接口芯片16550.ppt

kp****93

亲,该文档总共82页,到这已经超出免费预览范围,如果喜欢就直接下载吧~

相关资料

可编程串行接口芯片16550.ppt

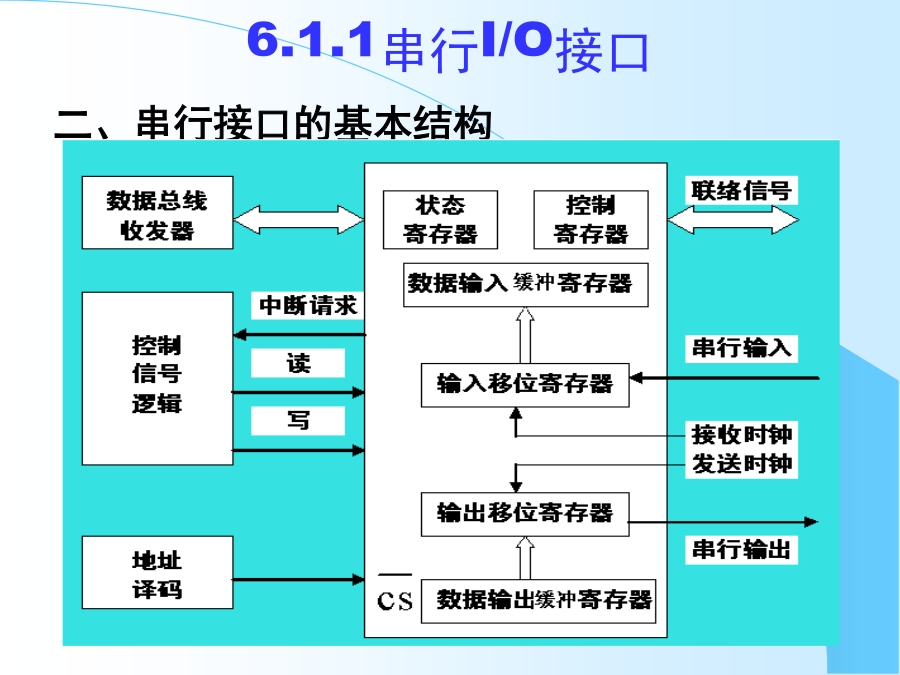

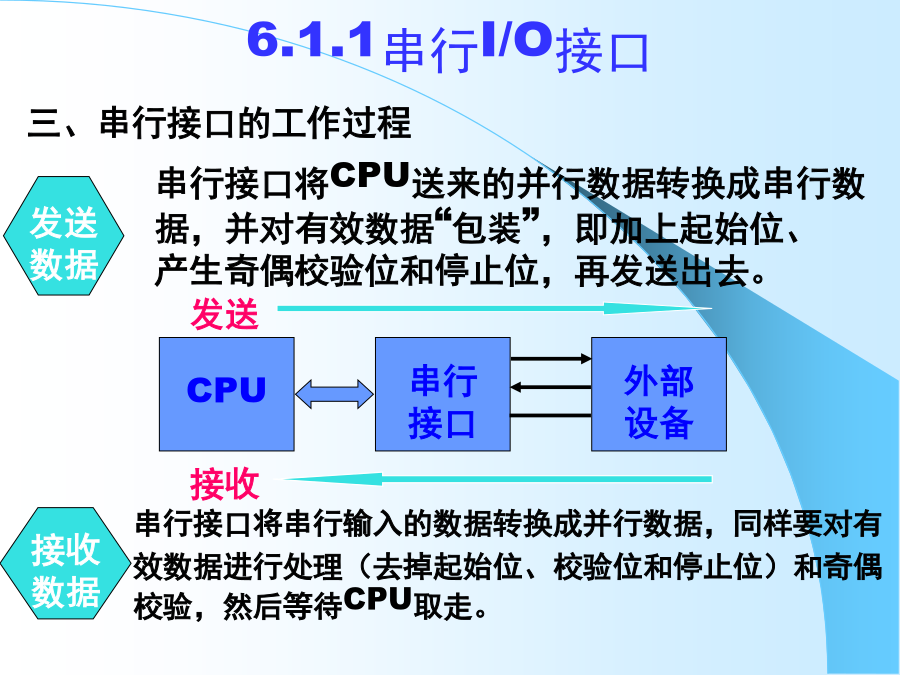

第6章可编程串行接口芯片165506.1串行接口系统概述6.1串行接口系统概述6.1.1串行I/O接口一、串行接口的基本功能功能1实现串行和并行数据格式之间的转换。二、串行接口的基本结构串行接口的基本结构如下:⑷输入缓冲寄存器:它从输入移位寄存器中接收并行数据,然后由CPU取走。三、串行接口的工作过程有效数据由CPU写入接口中的输出缓冲寄存器,再送到输出移位寄存器。同时将状态寄存器中的“发送准备好”位置“1”,并发出中断请求信号(用中断方式时),表示接口可以接收CPU写入下一个有效数据。在输出移位寄存器中

讲可编程串行通信接口芯片学习教案.pptx

会计学3.对于异步传送,可选择每个字符的数据位数(5—8位/字符),时钟频率为波特率的1、16或64倍,可产生1、1.5或2个位的停止位。能检查假启动位。能产生中止符,能自动检测和处理中止符。4.波特率:对同步传送DC——64K对异步传送DC——19.2K5.全双工,双缓冲的发送器和接收器。6.具有三种错误检测功能:奇/偶,溢出和帧错误。8251A的内部工作原理图:/为使8251配合cpu进行通信,通信之前:1.约定双方的通信方式(同步/异步),数据格式(数据位、停止位、校验位)、传输速率。2.控制数据的

微机原理及接口技术-第11章-串行通信和可编程接口芯片.ppt

第十一章串行通信和可编程接口芯片8251A11-1串行通讯的基本概念11-2可编程串行通讯接口芯片8251A11-3EIARS-232C串行口和8251A应用举例8251编程示例MOVDX,209HMOVAL,40H;复位命令。OUTDX,ALMOVAL,01001110B;方式字MOVDX,ALMOVAL,0011,0111B;命令字OUTDX,ALMOVDI,BUFF_TMOVCX,256;发送256字节NEXT:MOVDX209HINAL,DX;状态字ANDAL,01H;TXRDY?JZNEXTMO

可编程串行接口8250.ppt

可编程串行接口8250本节主要内容一、串行通信基本概念1、工作方式在做远距离传输时,需要通过MODEM将数字信号→模拟信号,可以利用电缆线传输(称为调制),接收方利用MODEM将模拟信号转换为数字信号(称为解调)。调制解调器的调制方式有以下三种:①振幅调制(AmplictuteShiftKeying,ASK)串行通信需要解决的问题2、同步通信与异步通信同步通信的优缺点异步串行通信方式异步通信时,字符/字节是一帧一帧的传送,每帧字符必须靠起始位来同步,在异步通信的数据传送中,传输线上允许空字符。2.波特率(

(计算机原理与接术可编程串行接口芯片8251A.pptx

第十一章串行通信和可编程接口芯片8251A本章内容串行通信的基本概念串行通信的基本概念串行通信的基本概念串行通信的基本概念串行通信的基本概念串行通信的基本概念串行通信的基本概念可编程串行接口芯片8251A可编程串行接口芯片8251A可编程串行接口芯片8251A可编程串行接口芯片8251AEIARS-232C串行口EIARS-232C串行口EIARS-232C串行口EIARS-232C串行口EIARS-232C串行口EIARS-232C串行口EIARS-232C串行口EIARS-232C串