多核DSP芯片TMS320C6678的DDR3接口设计_刘德保.pdf

qw****27

在线预览结束,喜欢就下载吧,查找使用更方便

相关资料

多核DSP芯片TMS320C6678的DDR3接口设计_刘德保.pdf

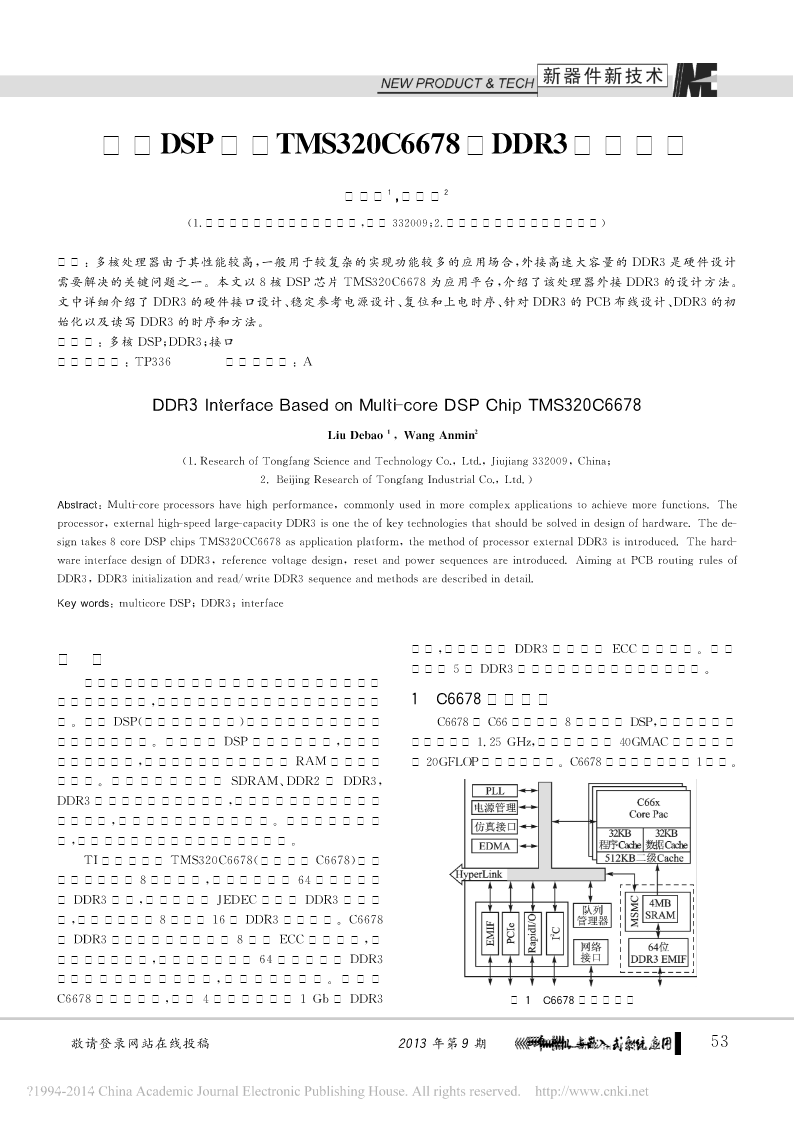

多核DSP芯片TMS320C6678的DDR3接口设计刘德保1,汪安民2(1.同方电子科技有限公司研究所,九江332009;2.同方工业有限公司北京研究所)摘要:多核处理器由于其性能较高,一般用于较复杂的实现功能较多的应用场合,外接高速大容量的DDR3是硬件设计需要解决的关键问题之一。本文以8核DSP芯片TMS320C6678为应用平台,介绍了该处理器外接DDR3的设计方法。文中详细介绍了DDR3的硬件接口设计、稳定参考电源设计、复位和上电时序、针对DDR3的PCB布线设计、DDR3的初始化以及读写DDR

TMS320C6678多核DSP的HyperLink应用.docx

TMS320C6678多核DSP的HyperLink应用AbstractTheTMS320C6678isamulti-coredigitalsignalprocessing(DSP)chipdesignedbyTexasInstruments.Thischipoffersahigh-performance,scalable,andlow-powersolutionforapplicationssuchaswirelessbasestations,videoprocessing,andradarsystem

基于SRIO交换芯片的DSP接口设计.docx

基于SRIO交换芯片的DSP接口设计现代数字信号处理器(DSP)的市场需求不断增加,要求DSP能够具备更高的性能、更低的功耗以及更高的设计灵活性。然而,DSP芯片的性能只有在正确的接口设计下才能得到充分发挥。因此,SRIO(SerialRapidIO)交换芯片成为了当前DSP设计中的一个重要组成部分。SRIO接口是一种面向高速串行通信的标准,它越来越受到DSP图像处理领域的欢迎。SRIO接口的特点是高速、低延时、低功耗、灵活、可靠和易于成本控制,逐步取代了其他高速串行接口协议,如PCIExpress(PC

基于SRIO交换芯片的DSP接口设计.pptx

,目录PartOneSRIO交换芯片的功能和特点SRIO交换芯片的应用场景PartTwoDSP接口的种类和特点基于SRIO交换芯片的DSP接口设计原理DSP接口设计的关键技术PartThreeSRIO交换芯片与DSP接口的连接方式连接方式的优缺点比较PartFour设计实例一:基于SRIO交换芯片的数字信号处理系统设计实例二:基于SRIO交换芯片的音频处理系统PartFive基于SRIO交换芯片的DSP接口设计的发展趋势基于SRIO交换芯片的DSP接口设计的挑战与机遇THANKS

基于EMIF接口的TMS320C6678多核程序自启动设计与实现.docx

基于EMIF接口的TMS320C6678多核程序自启动设计与实现TMS320C6678是德州仪器公司(TI)推出的一种高性能多核微处理器,具有12个VLIW型DSP核心和4个ARMCortex-A15核心。为适应复杂的应用场景,TMS320C6678需要与各种外部设备进行高速稳定的数据交换,这就需要使用EMIF(ExternalMemoryInterface)接口。本文将探索如何在TMS320C6678多核处理器上实现EMIF接口对程序的自启动设计。首先,我们需要了解EMIF接口是什么。EMIF接口是TM