高速DSP与串行AD转换器TLC2558接口的设计.pdf

as****16

在线预览结束,喜欢就下载吧,查找使用更方便

相关资料

高速DSP与串行AD转换器TLC2558接口的设计.pdf

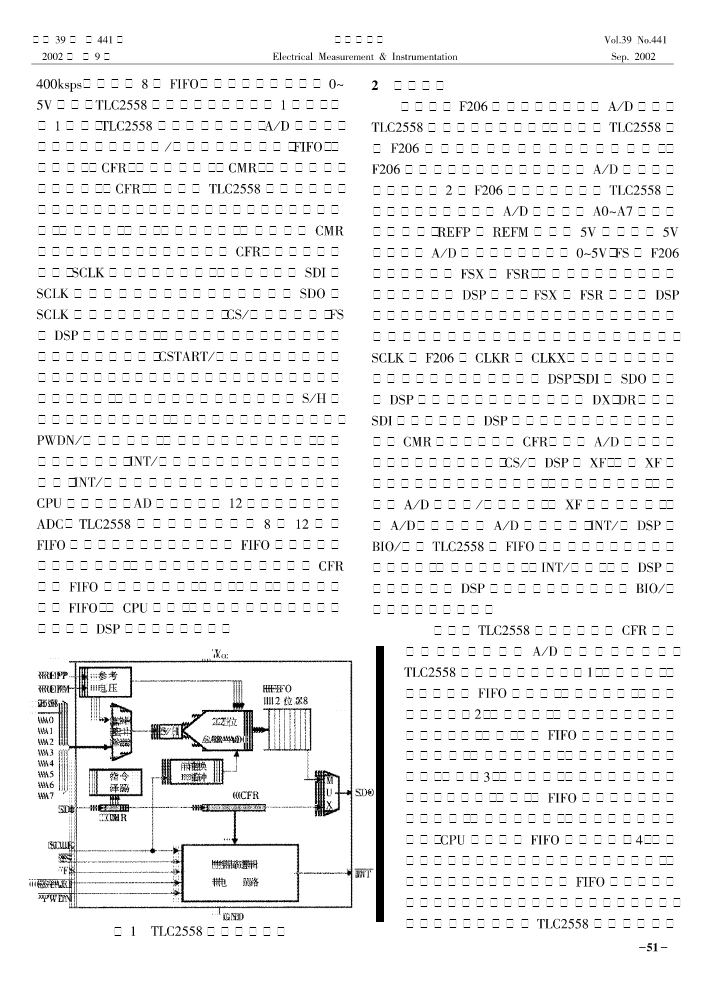

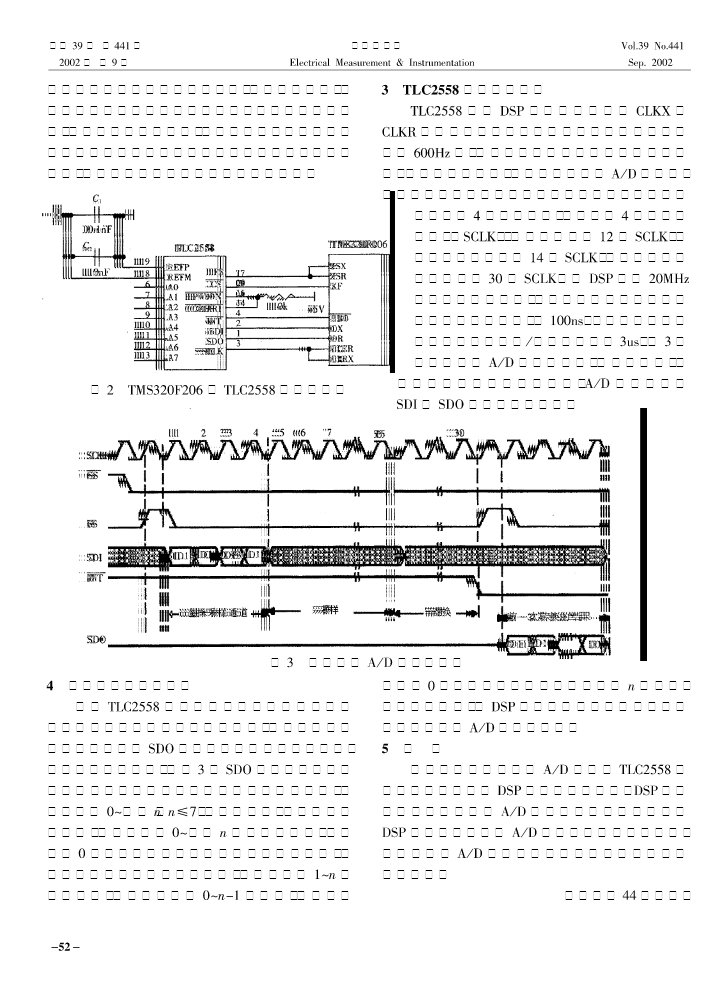

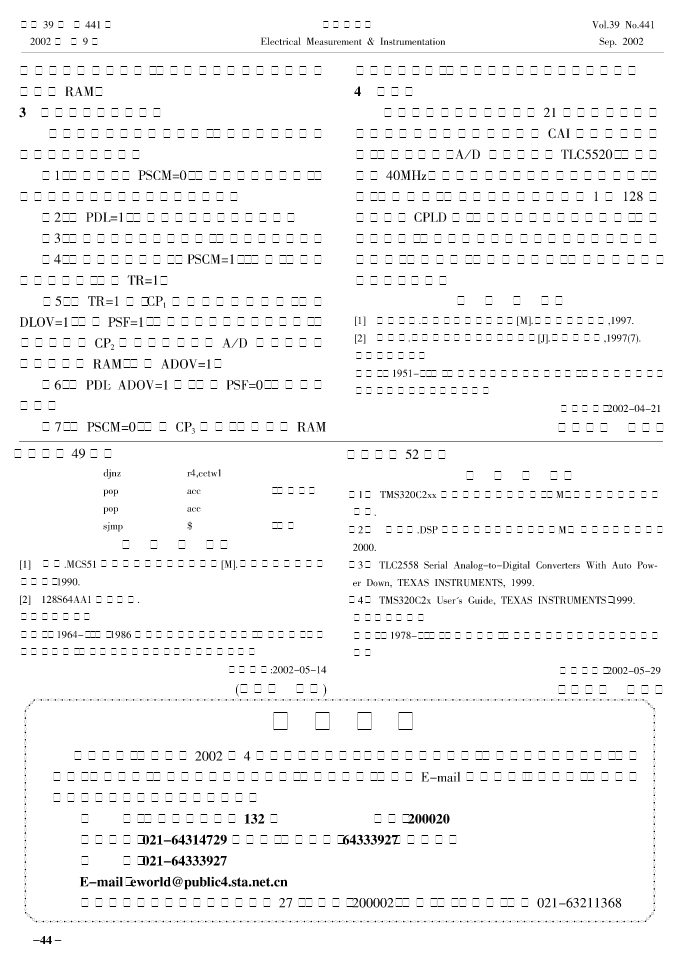

总第!"卷第##$期电测与仪表%&’(!")&(##$*++*年第"期,’-./01.2’3-2450-6-7/8974/056-7/2/1&7:-;(*++*高速#$%与串行&’#转换器()*+!!,接口的设计欧阳兵,吕艳萍,骆德昌,叶菁(武汉大学电气工程学院,武汉#!++<*)摘要:根据高速定点=:>芯片?3:!*+@*+A的特点,提出了使用串行BC=转换器?DE*FFG作为=:>系统的模拟量输入部分,解决了以往基于并行数据传输的BC=转换器不能与高速=:>进行很好配合的问题。在此基础上设计了=:>与

基于FPGA和高速串行接口AD转换器AD7476的接口应用.docx

基于FPGA和高速串行接口AD转换器AD7476的接口应用随着时代的发展和科技的进步,FPGA和高速串行接口AD转换器的应用越来越广泛。FPGA,即现场可编程门阵列,是一种可编程电路的芯片。AD转换器则是将模拟信号转换为数字信号的设备。利用FPGA和高速串行接口AD转换器的接口应用,可以实现很多有用的功能,比如数据采集、信号处理、图像识别等。FPGA和高速串口AD转换器接口的设计是一个繁琐而复杂的工作。因为FPGA芯片和高速串口AD转换器的规格和特点不同,因此需要针对不同的芯片进行适配和优化。要想设计出能

单片机与串行AD转换器TLC0834的接口设计.doc

单片机与串行AD转换器TLC0834的接口设计摘要:TLC0834是TI公司生产的八位逐次逼近模数转换器,具有输入可配置的多通道多路器和串行输入方式。文中以AT89C51CPU为核心,采用LTC0834八位串行A/D转换器设计了一个可将模拟信号转换为数字信号的电路。关键词:单片机A/D转换器TLC0834单片机控制系统通常要用到A/D转换。根据输出的信号格式,比较常用的A/D转换方式可分为并行A/D和串行A/D。并行方式一般在转换后可直接接收,但芯片的引脚比较多;串行方式所用芯片引脚少,封装小,在PCB板

单片机与串行AD转换器TLC0834的接口设计.doc

单片机与串行AD转换器TLC0834的接口设计摘要:TLC0834是TI公司生产的八位逐次逼近模数转换器,具有输入可配置的多通道多路器和串行输入方式。文中以AT89C51CPU为核心,采用LTC0834八位串行A/D转换器设计了一个可将模拟信号转换为数字信号的电路。关键词:单片机A/D转换器TLC0834单片机控制系统通常要用到A/D转换。根据输出的信号格式,比较常用的A/D转换方式可分为并行A/D和串行A/D。并行方式一般在转换后可直接接收,但芯片的引脚比较多;串行方式所用芯片引脚少,封装小,在PCB板

单片机与串行AD转换器TLC0834的接口设计.docx

单片机与串行AD转换器TLC0834的接口设计摘要:TLC0834是TI公司生产的八位逐次逼近模数转换器,具有输入可配置的多通道多路器和串行输入方式。文中以AT89C51CPU为核心,采用LTC0834八位串行A/D转换器设计了一个可将模拟信号转换为数字信号的电路。关键词:单片机A/D转换器TLC0834单片机控制系统通常要用到A/D转换。根据输出的信号格式,比较常用的A/D转换方式可分为并行A/D和串行A/D。并行方式一般在转换后可直接接收,但芯片的引脚比较多;串行方式所用芯片引脚少,封装小,在PCB板