第5章 微机原理与接口技术.ppt

qw****27

亲,该文档总共54页,到这已经超出免费预览范围,如果喜欢就直接下载吧~

相关资料

微机原理与接口技术微机原理与接口技术.pdf

微机原理与接口技术微机原理与接口技术第十五讲第十五讲15:23第六章第六章I/OI/O接口和总线接口和总线内容提要内内容容提提要要6-16-1I/OI/O接口接口一、一、I/OI/O接口的功能接口的功能二、简单的输入输出芯片二、简单的输入输出芯片三、三、I/OI/O端口及其寻址方式端口及其寻址方式四、四、CPUCPU与外设间的数据传送方式与外设间的数据传送方式五、五、I/OI/O译码电路译码电路6-26-2总线总线15:232第六章第六章I/OI/O接口和总线接口和总线一.一.I/OI/O接口的功能接口的

微机原理及接口技术微机原理第04章3.ppt

第4章第4章:例源程序文件wjl301.asm4.2.3.程序开始4.2.3.程序终止从上述程序中,我们可总结出如下结论:①SEGMENT和ENDS前面必须有标号,而且在相互配对的段,它们前面要使用相同的标号。②ASSUME语句可使汇编器知道CS、DS、SS指向哪个段,但它只在汇编时起作用,在运行时CPU并不知道除CS外的其它段地址,所以必须在程序中用指令进行赋值。③首条被执行的语句有一个标号,在程序的结尾使用END后跟上这个标号,用以标出这个程序的开始执行处。4.2.4过程定义伪指令汇编语言中,子程序要

第5章 微机原理与接口技术.ppt

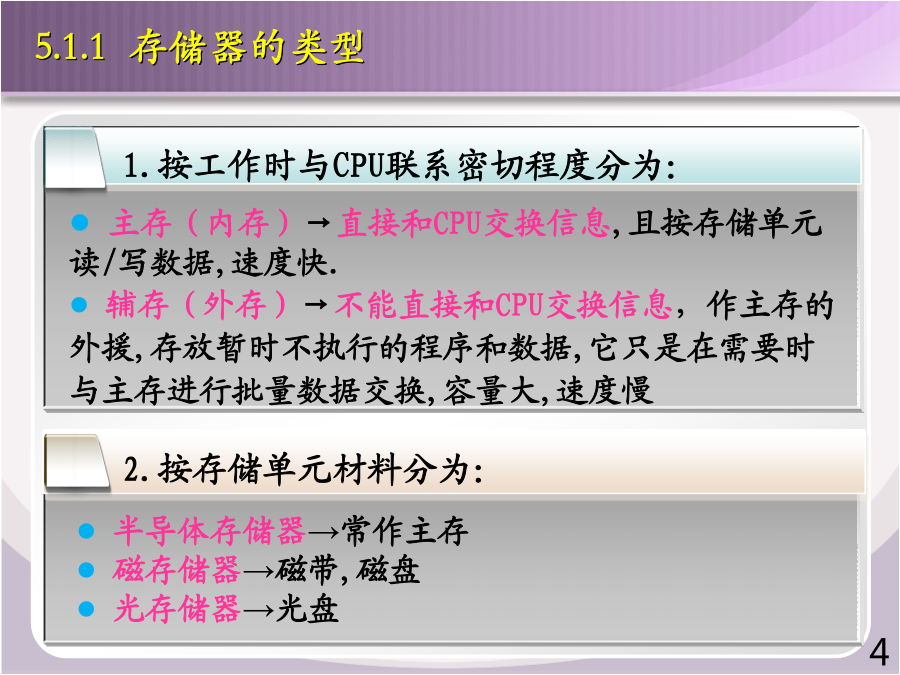

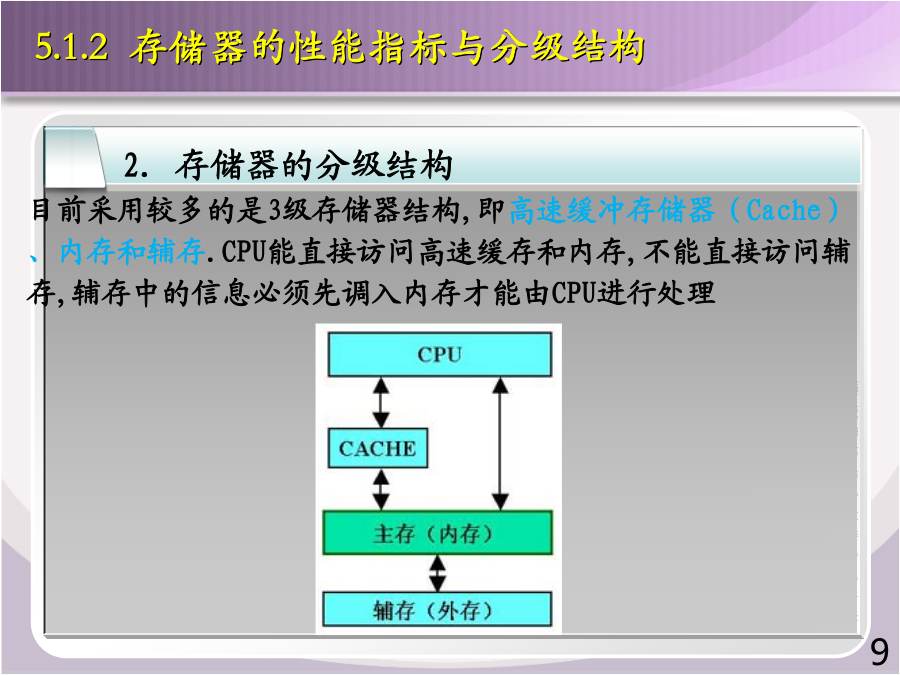

微机原理、汇编与接口技术5.1.1存储器的类型5.1.1存储器的类型5.1.2存储器的性能指标与分级结构5.1.2存储器的性能指标与分级结构5.1.2存储器的性能指标与分级结构5.1.2存储器的性能指标与分级结构半导体存储器存储器芯片的特征存储器芯片的特征存储器芯片的特征(续)存储芯片结构与译码方式5.2常用的存储器芯片1.EPROM常用EPROM以1片2716(2K×8)为最基本容量.如:2732→4K×8,2764→8K×8,27128→16K×8,27256→32K×82.EEPROM常用芯片有28

微机原理与接口技术第8章.ppt

第8章串行和并行接口8.1通用接口及其功能8.1通用接口及其功能8.2并行接口8.2并行接口8.2并行接口8.2并行接口8.2并行接口8.2并行接口8.2并行接口8.2并行接口8.2并行接口8.2并行接口8.2并行接口8.2并行接口8.2并行接口8.2并行接口8.2并行接口8.2并行接口8.2并行接口8.2并行接口8.2并行接口8.2并行接口8.2并行接口8.2并行接口8.2并行接口8.2并行接口8.2并行接口8.2并行接口8.2并行接口8.2并行接口8.2并行接口8.2并行接口8.2并行接口8.2并行接

微机原理与接口技术 第8章.ppt

第八章常用可编程接口芯片本章重点定时器/计数器8253/8254可编程定时/计数器8253/8254结构8253/8254寄存器地址分配8253的控制字例8-18253的初始化8253工作方式8253/8254方式08253/8254方式18253/8254方式28253/8254方式38253方式3示例方式2和方式3初值计算8253/8254方式48253/8254方式58253六种工作方式比较8253/8254芯片在微机上的应用微机系统中8253的通道0微机系统中8253的通道1微机系统中8253的通