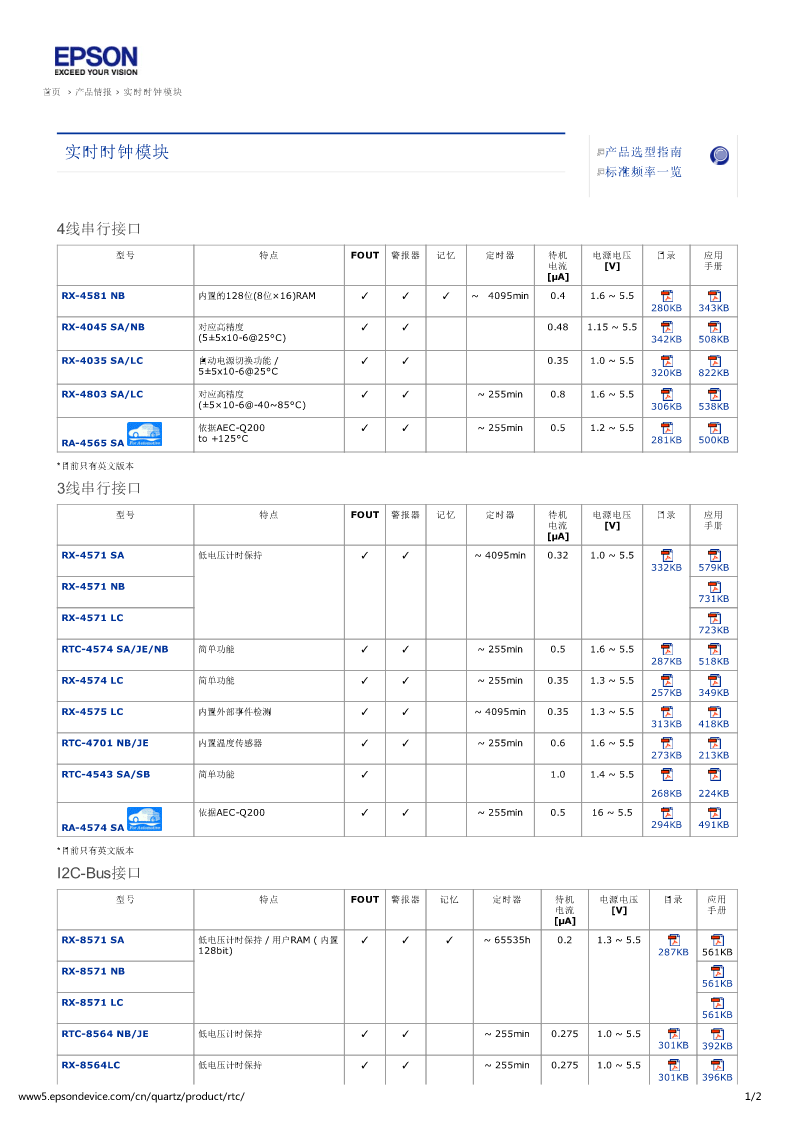

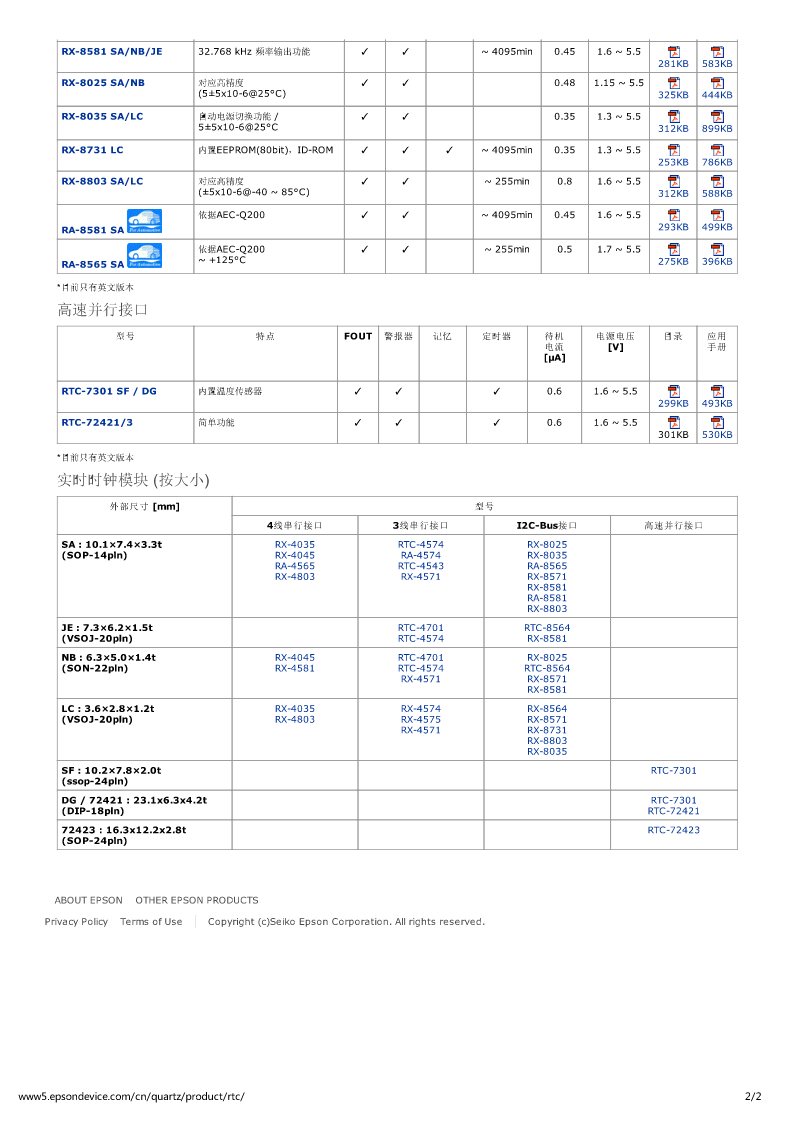

实时时钟模块.pdf

as****16

在线预览结束,喜欢就下载吧,查找使用更方便

相关资料

实时时钟模块.pdf

实时时钟芯片重要模块设计与分析.docx

实时时钟芯片重要模块设计与分析实时时钟芯片是一种用于计时和日期显示的集成电路,它通常用于嵌入式系统或电子设备中,以提供准确的时间和日期信息。实时时钟芯片的重要模块设计与分析是研究实时时钟芯片的核心内容,本文将从芯片架构、时钟信号源、时钟校准及时钟分频等方面进行论述和分析。一、芯片架构实时时钟芯片的架构设计是其功能实现的基础,一般包括时钟源、控制单元、计数单元和存储单元等部分。1.时钟源:时钟源用于提供稳定可靠的时钟信号,通常采用晶体振荡器作为时钟源。振荡器的频率决定了实时时钟的计时精度,常见的频率有32.

实时时钟设计.ppt

报告内容核心检索技术学术文献总库:文献总量6500万篇。文献类型包括:学术期刊、博士学位论文、优秀硕士学位论文、工具书、重要会议论文、年鉴、专著、报纸、专利、标准、科技成果、知识元、哈佛商业评论数据库、古籍等;还可与德国Springer公司期刊库等外文资源统一检索。我馆目前购买了该系统中的中国期刊全文数据库(1994年至今)、中国优秀硕士学位论文全文数据库和中国博士学位论文全文数据库(1999年至今)三个数据库。中国学术期刊全文数据库概述中国学术期刊全文数据库检索首页面新版平台旧版入口单库检索—选检索项(

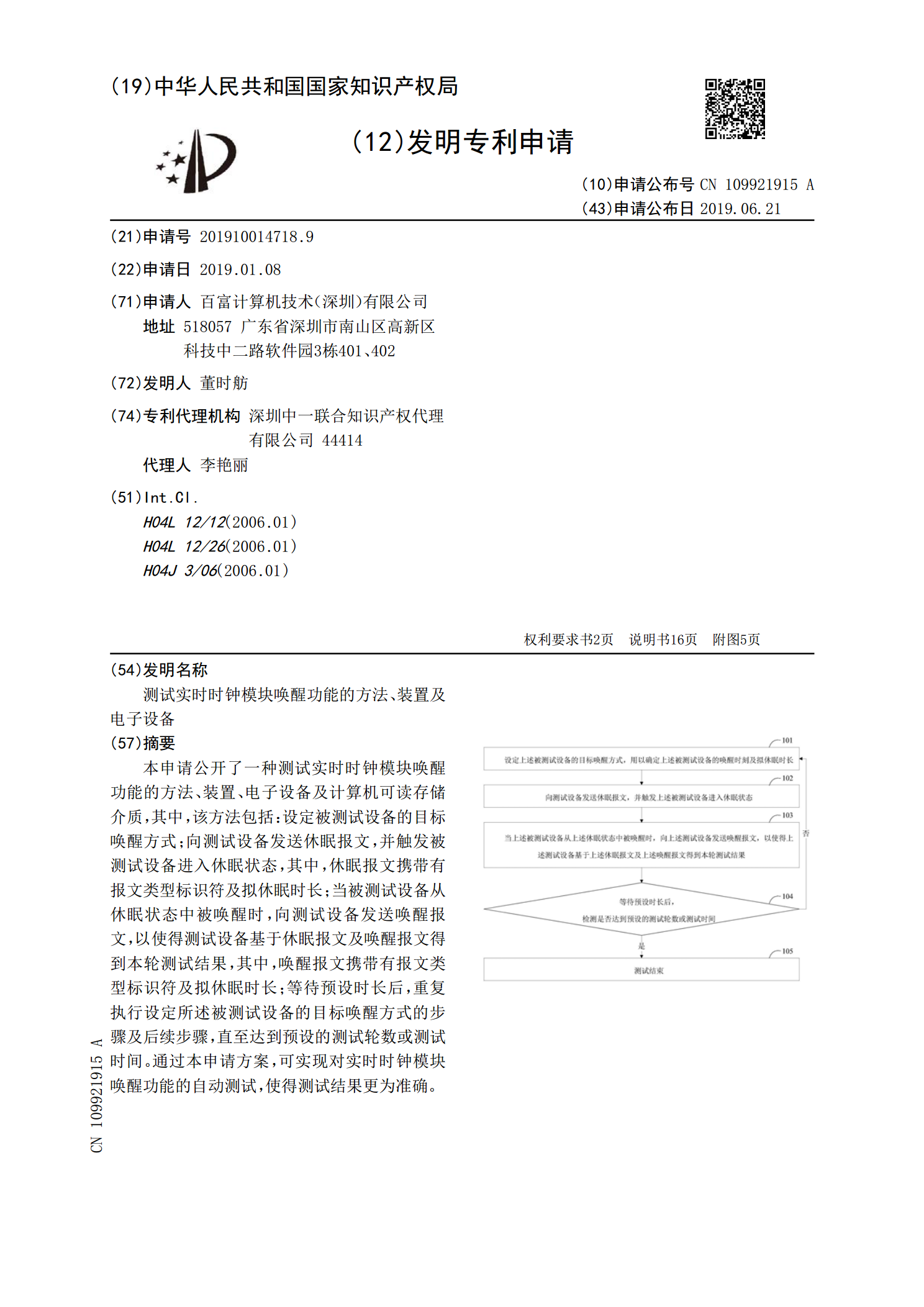

测试实时时钟模块唤醒功能的方法、装置及电子设备.pdf

本申请公开了一种测试实时时钟模块唤醒功能的方法、装置、电子设备及计算机可读存储介质,其中,该方法包括:设定被测试设备的目标唤醒方式;向测试设备发送休眠报文,并触发被测试设备进入休眠状态,其中,休眠报文携带有报文类型标识符及拟休眠时长;当被测试设备从休眠状态中被唤醒时,向测试设备发送唤醒报文,以使得测试设备基于休眠报文及唤醒报文得到本轮测试结果,其中,唤醒报文携带有报文类型标识符及拟休眠时长;等待预设时长后,重复执行设定所述被测试设备的目标唤醒方式的步骤及后续步骤,直至达到预设的测试轮数或测试时间。通过本申

51 时钟模块.ppt

第5章MSP430单片机片内外围模块5.1.1时钟模块系统时钟必须满足以下不同要求:基础时钟模块有3个时钟输入源:提供3种时钟信号:MSP430X1XX时钟模块系统频率和系统的工作电压关系:5.1.1.1低速晶体振荡器5.1.1.2高速晶体振荡器5.1.1.4DCO振荡器5.1.1.4基本时钟模块失效操作5.1.1.6基本时钟模块寄存器1.DCOCTLDCO控制寄存器2.BCSCTL1基本时钟系统控制寄存器1DIVA.0DIVA.1:控制ACLK分频。000不分频(默认不分频);0112分频;1024分频