一种存储阵列电路结构及大型存储阵列电路结构.pdf

猫巷****晓容

在线预览结束,喜欢就下载吧,查找使用更方便

相关资料

一种存储阵列电路结构及大型存储阵列电路结构.pdf

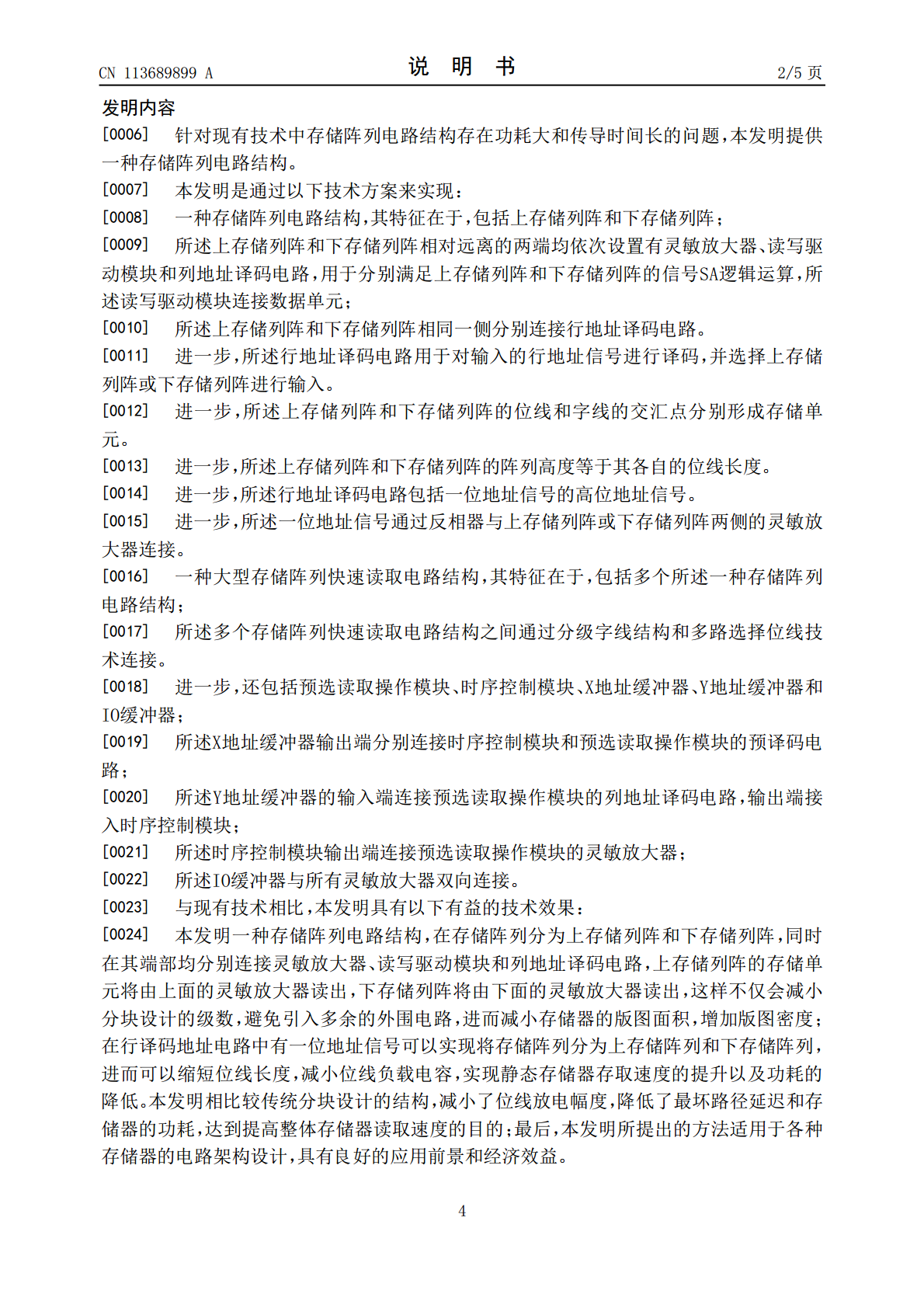

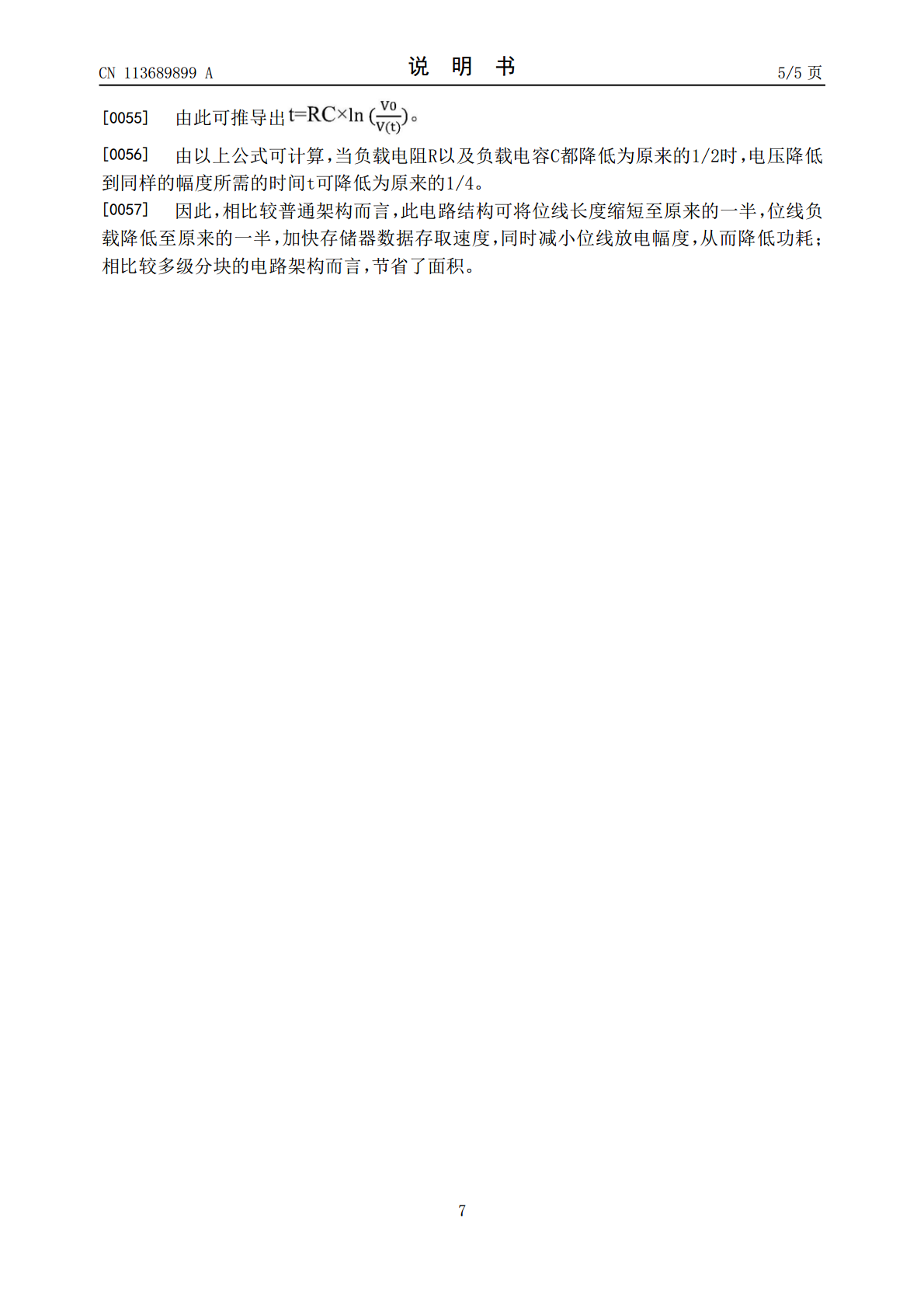

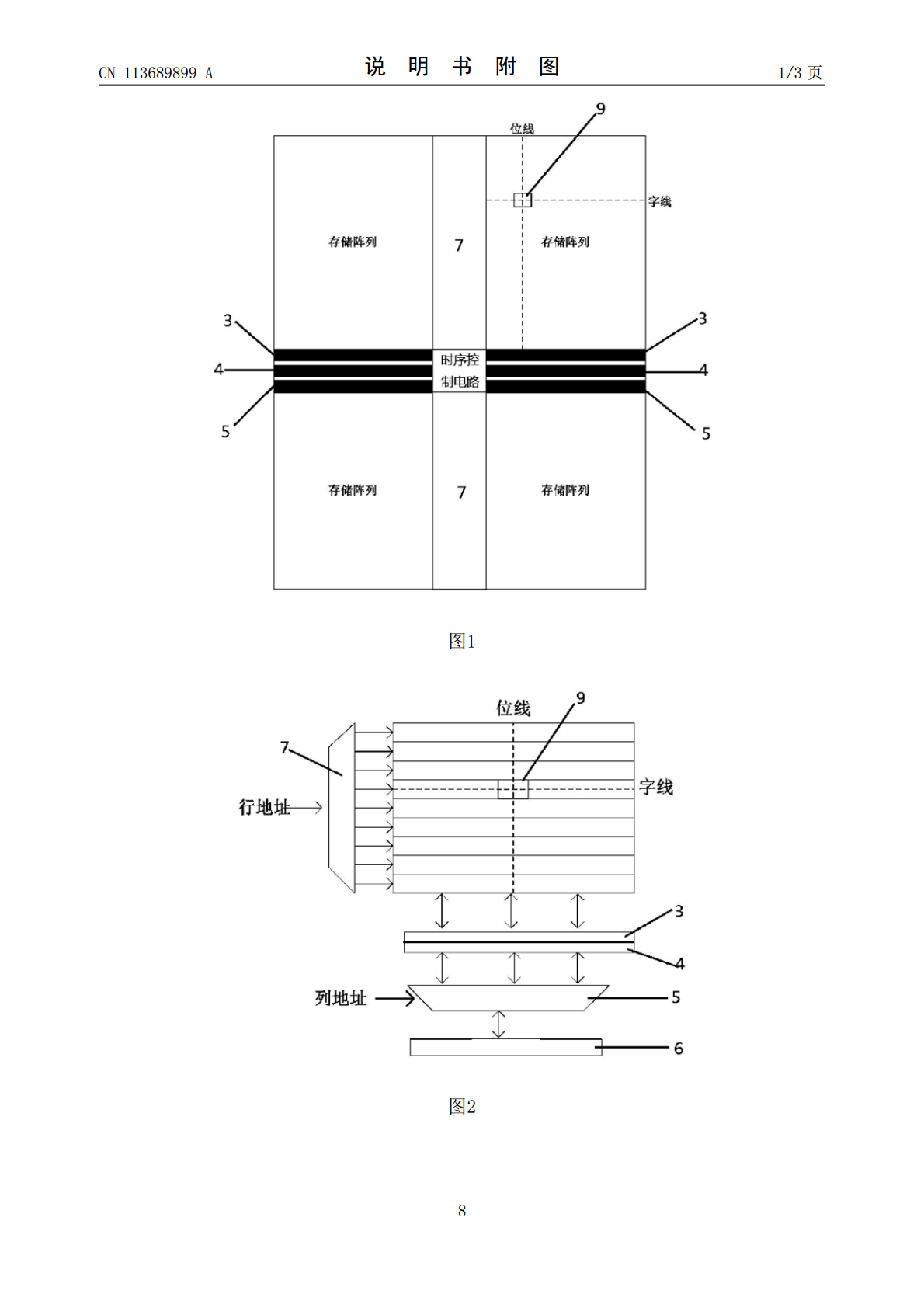

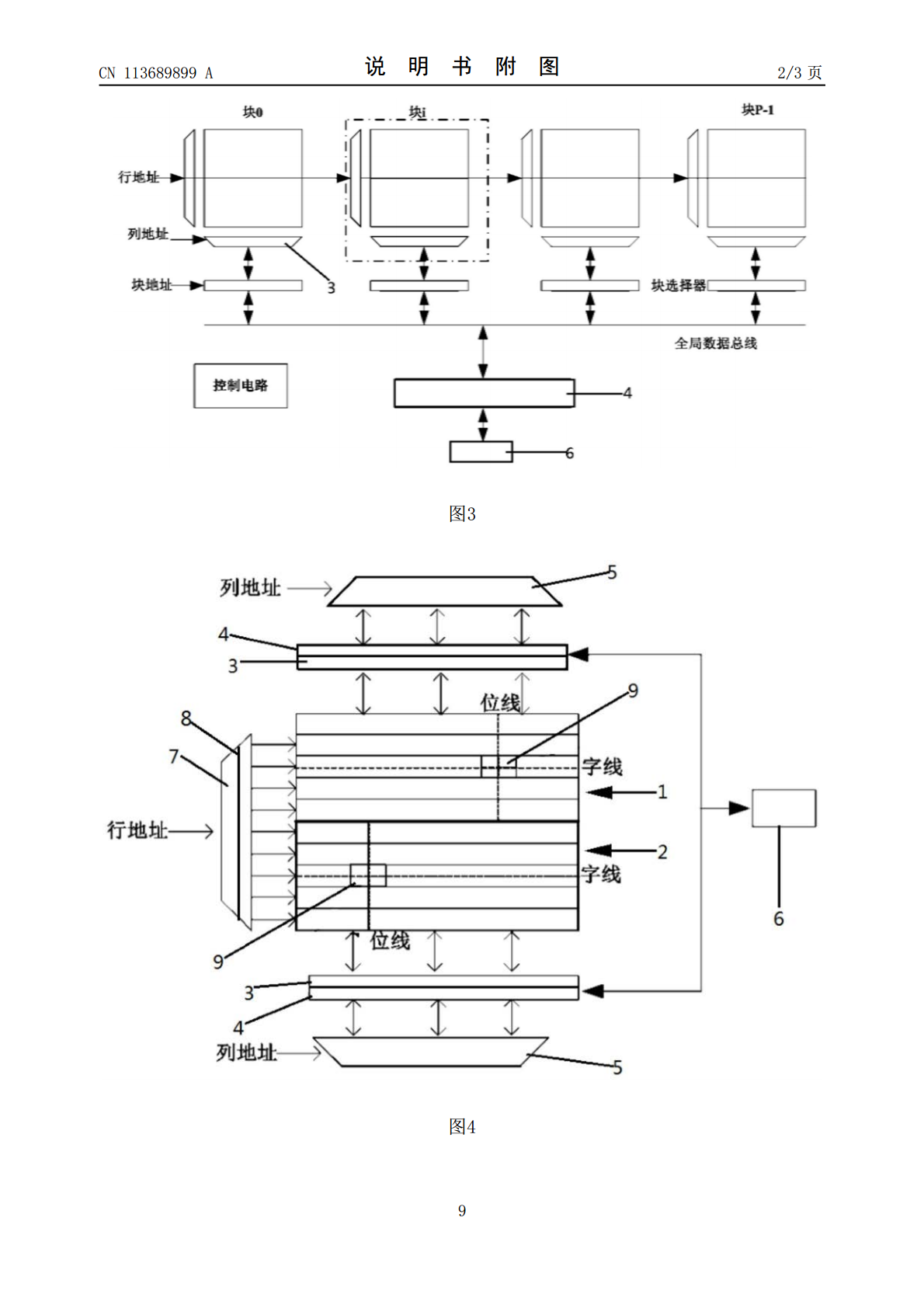

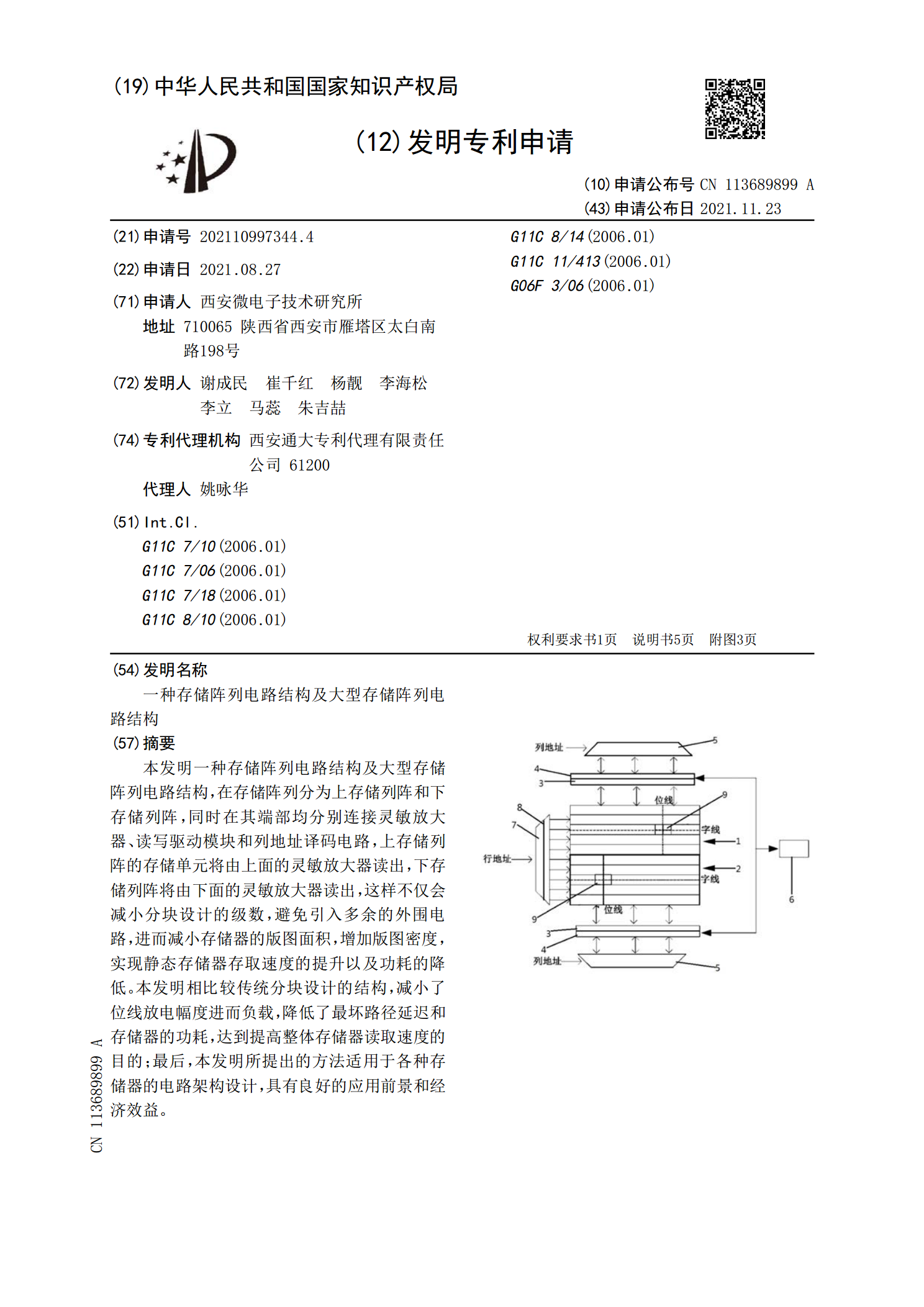

本发明一种存储阵列电路结构及大型存储阵列电路结构,在存储阵列分为上存储列阵和下存储列阵,同时在其端部均分别连接灵敏放大器、读写驱动模块和列地址译码电路,上存储列阵的存储单元将由上面的灵敏放大器读出,下存储列阵将由下面的灵敏放大器读出,这样不仅会减小分块设计的级数,避免引入多余的外围电路,进而减小存储器的版图面积,增加版图密度,实现静态存储器存取速度的提升以及功耗的降低。本发明相比较传统分块设计的结构,减小了位线放电幅度进而负载,降低了最坏路径延迟和存储器的功耗,达到提高整体存储器读取速度的目的;最后,本发

一种半导体存储器的阵列结构.pdf

本发明提供一种半导体存储器的阵列结构,具有纵向和横向两个互相垂直的方向,在复数个阵列排布的有源区中,每个有源区具有相同的外轮廓。奇数行的有源区与横向以相同的第一倾角等间距排布,并在纵向上依次对齐。偶数行的有源区与横向以相同的第二倾角等间距排布,并在纵向上依次对齐;第一倾角与第二倾角相对于横向分别形成有顺逆时钟不同方向的锐角旋转角度。复数个字线为平行于纵向的直线形且沿横向等间距排列。复数个位线位线为平行于横向的波浪线形且沿纵向等间距排列。字线将有源区分隔出位线接触区与节点接触区,位线与有源区的交汇处位于位线

一种磁存储阵列的测试结构及测试方法.pdf

本发明提供了一种磁存储阵列的测试结构及测试方法,测试结构包括下金属层、上金属层、磁隧道结阵列、原位磁场结构,磁隧道结阵列中包含有待测磁存储器件。原位磁场结构包括环绕待测磁存储器件的至少一匝金属线圈。通过在磁隧道结阵列的上下两个进行层的至少一个金属层内设置原位磁场结构,能够通过向至少一匝金属线圈通电流,以给作为单个或几个磁隧道结组成的待测磁存储器件施加垂直磁场,测试待测磁存储器件在读写过程中抗外磁场的干扰性能。且还能够通过原位磁场,计算出待测磁存储器件的热稳定因子等重要参数,以在WAT测试中能够获取到待测磁

存储单元阵列及其单元结构.pdf

本发明公开了一种只读存储器(ROM)单元阵列及其单元结构。该ROM单元阵列与多个行位线和多个列字线相连接且包括:沿着列方向布置的多个子单元阵列,每个子单元阵列包括多个单位单元结构。每个单位单元结构包括:限定出单元边界的单元基底区域,该区域包括被布置在衬底上的具有宽形块状轮廓且限定出连续共用源极节点的覆盖式OD层;设置在OD层之上,被布置成选择性地连接位线的漏极焊垫;桥接在漏极焊垫和OD层之间的垂直沟道结构;以及垂直地设置在漏极焊垫和OD层之间且布置成与字线相连接的栅极结构。子单元阵列边界完全被限定在OD层

SRAM存储阵列的内建自测试电路设计与实现.docx

SRAM存储阵列的内建自测试电路设计与实现SRAM(StaticRandomAccessMemory)是一种常见的存储器设备,特点是数据存取速度快、功耗低。然而,由于SRAM内部结构的复杂性,使得其在制造和测试过程中容易出现故障,从而降低了性能和可靠性。因此,设计和实现内建自测试电路(Built-InSelf-Test,简称BIST)成为了解决SRAM故障检测和诊断的关键技术。本论文将重点探讨SRAM存储阵列的内建自测试电路的设计与实现。首先,我们将介绍SRAM的基本原理和结构,以及常见的故障类型。接着,