基于FPGA和DSP的捷变相参目标检测装置及方法.pdf

景山****魔王

亲,该文档总共11页,到这已经超出免费预览范围,如果喜欢就直接下载吧~

相关资料

基于FPGA和DSP的捷变相参目标检测装置及方法.pdf

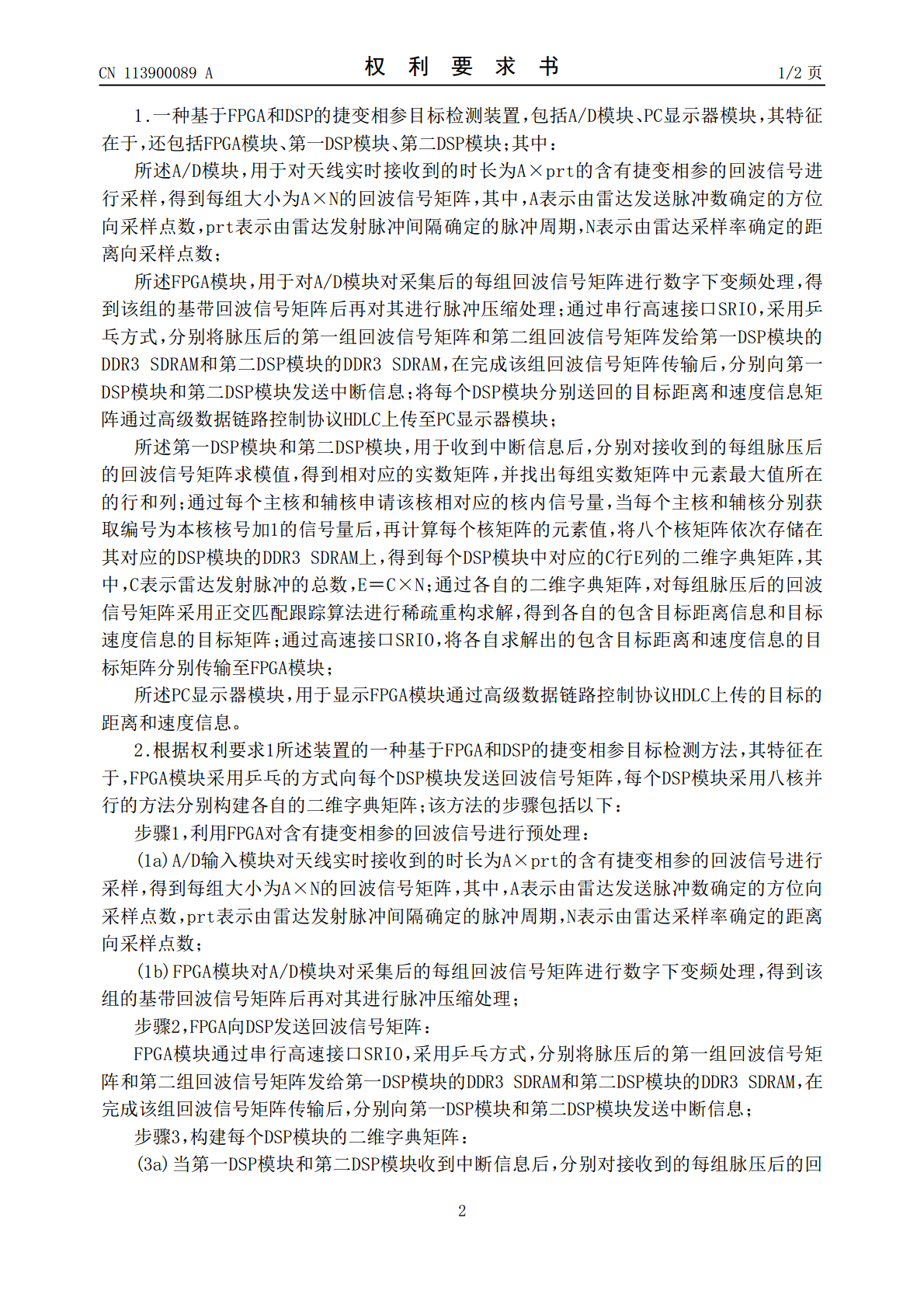

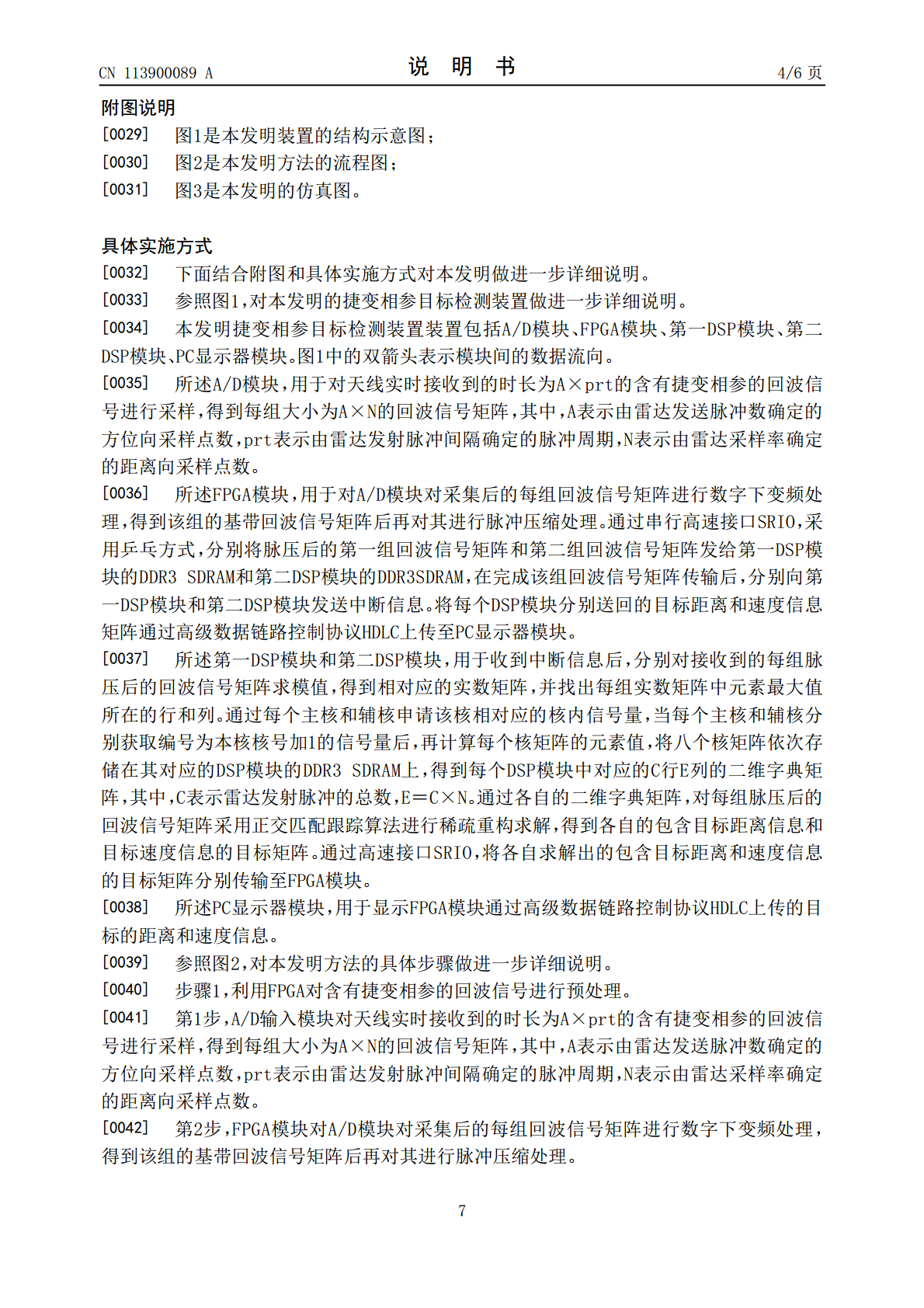

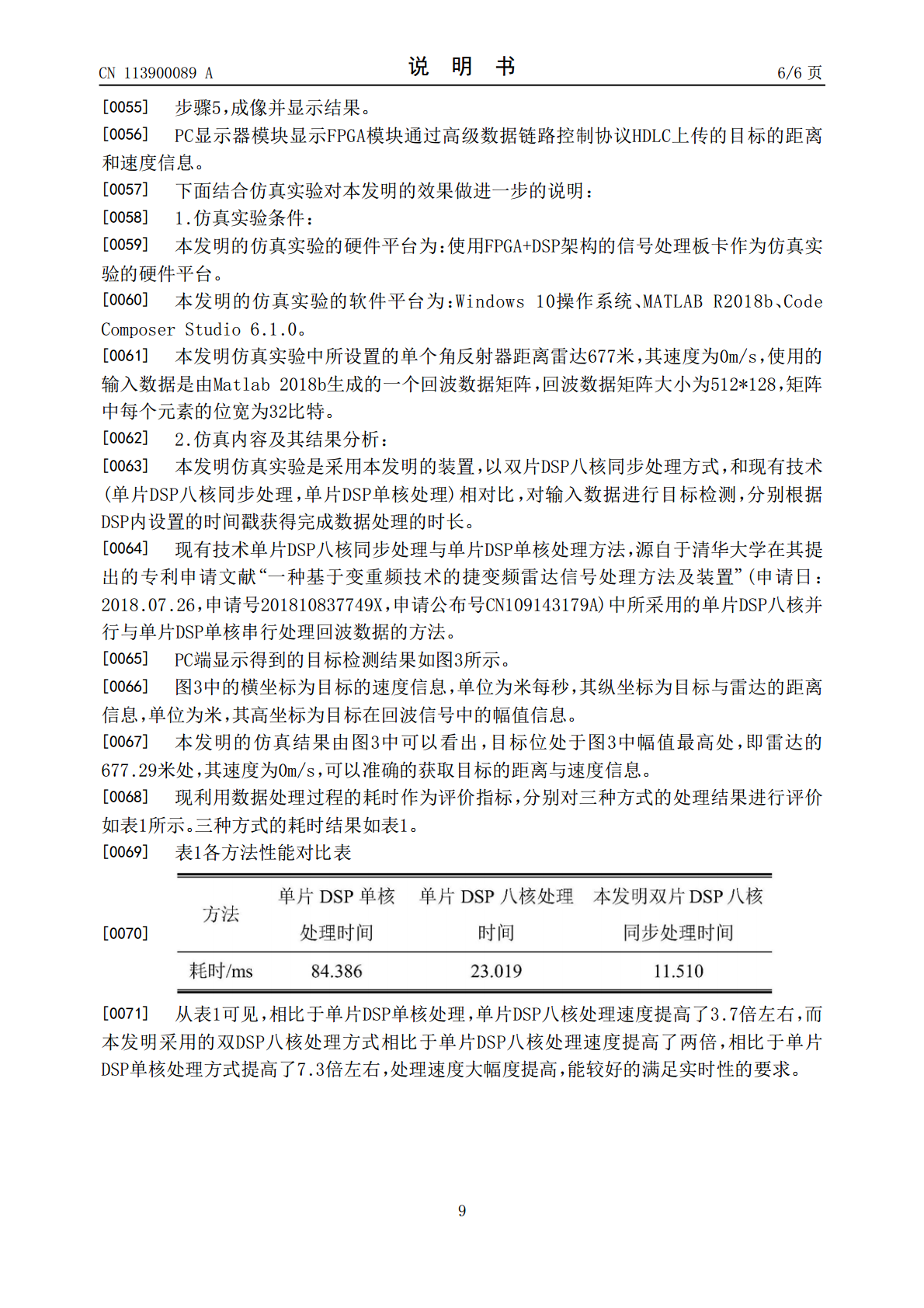

本发明公开了一种基于FPGA和DSP的捷变相参目标检测装置及方法,本发明的装置包括A/D模块、FPGA模块、第一DSP模块、第二DSP模块和PC模块。本发明方法的步骤包括:(1)利用FPGA对含有捷变相参的回波信号进行预处理;(2)FPGA向DSP发送回波信号矩阵;(3)构建每个DSP模块的二维字典矩阵;(4)获取目标速度和距离信息;(5)成像并显示目标距离和速度信息。本发明充分利用FPGA和DSP各自的架构特点,发挥多核DSP并行执行的优势和处理速度,在很好地满足实时性的前提下,提高了捷变相参目标检测的

基于相位对消捷变相参雷达杂波抑制的目标检测方法.pdf

本发明公开了一种基于相位对消捷变相参雷达杂波抑制的目标检测方法。实现步骤为:首先对雷达回波脉冲信号进行采样及脉冲压缩得到脉压回波,利用相位对消技术对脉压回波进行杂波抑制,并通过相位补偿对回波进行相位校正,最后通过非均匀傅里叶变换与均值类恒虚警检测方法,实现回波信号的相参积累与检测运动目标。解决了现有技术方法中在回波数据不足的情况下,无法准确估计杂波的多普勒频率范围,不能在实际主杂波区形成很深的杂波凹陷,从而不能有效地抑制杂波的问题。本发明无需大量回波数据,便可以在实际主杂波区形成很深的杂波凹陷,有效地抑制

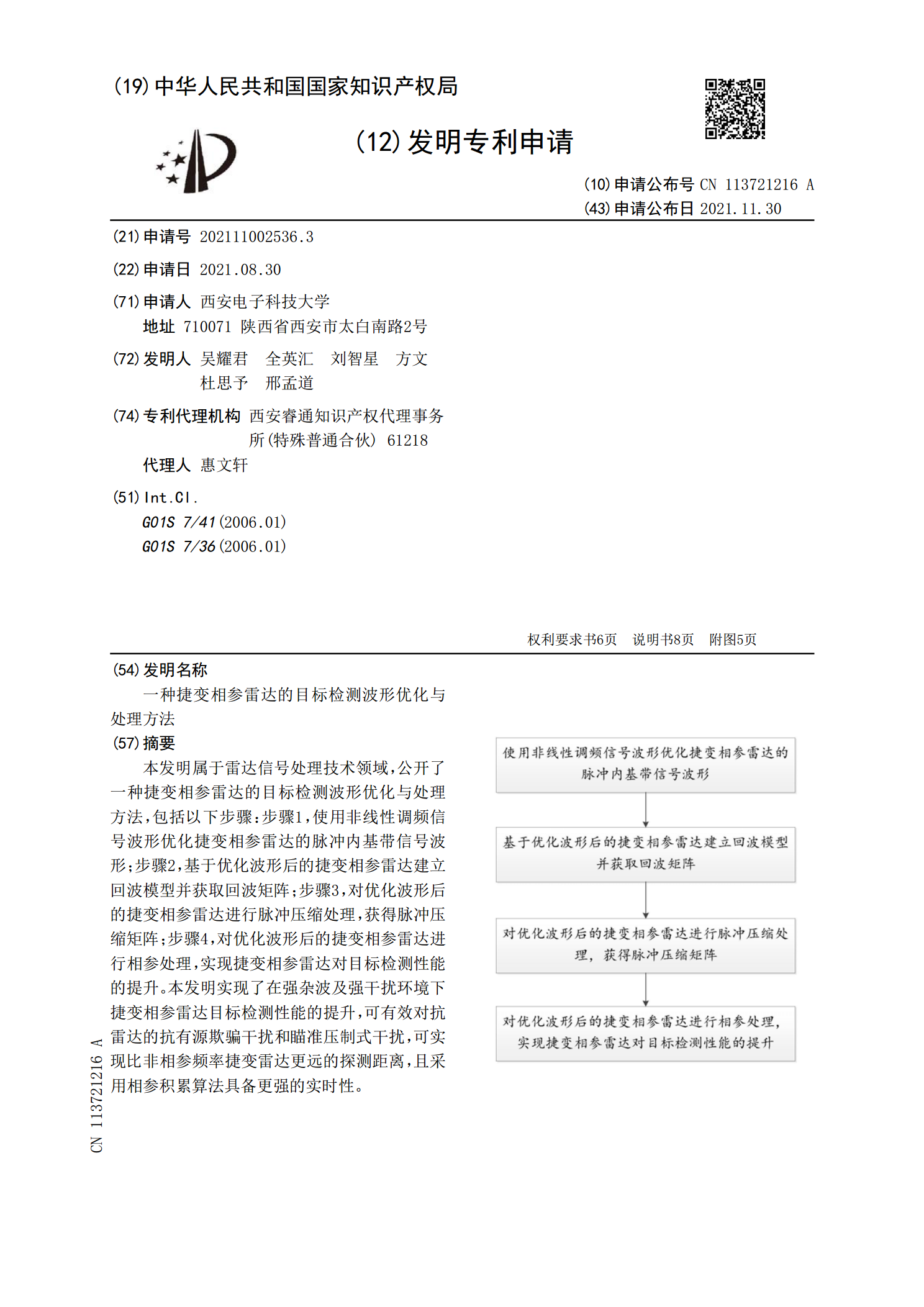

一种捷变相参雷达的目标检测波形优化与处理方法.pdf

本发明属于雷达信号处理技术领域,公开了一种捷变相参雷达的目标检测波形优化与处理方法,包括以下步骤:步骤1,使用非线性调频信号波形优化捷变相参雷达的脉冲内基带信号波形;步骤2,基于优化波形后的捷变相参雷达建立回波模型并获取回波矩阵;步骤3,对优化波形后的捷变相参雷达进行脉冲压缩处理,获得脉冲压缩矩阵;步骤4,对优化波形后的捷变相参雷达进行相参处理,实现捷变相参雷达对目标检测性能的提升。本发明实现了在强杂波及强干扰环境下捷变相参雷达目标检测性能的提升,可有效对抗雷达的抗有源欺骗干扰和瞄准压制式干扰,可实现比非

基于DSP和FPGA的目标跟踪平台设计与实现.docx

基于DSP和FPGA的目标跟踪平台设计与实现目标跟踪是计算机视觉中的重要问题之一,它是为了实现自动化控制和智能监控等应用而需解决的关键问题。目前,基于数字信号处理(DSP)和可编程逻辑器件(FPGA)的目标跟踪平台已经成为热门研究领域之一,由于其高速、高效、灵活性强等优势,普遍应用于无人机、机器人、智能监控和自动驾驶等领域。本文是基于DSP和FPGA的目标跟踪平台设计与实现的论文。文章主要分为三个部分:第一部分介绍目标跟踪的概念、技术背景和研究现状;第二部分是基于DSP和FPGA的目标跟踪平台设计;第三部

基于DSP和FPGA的光纤陀螺捷联惯导系统的硬件电路研究.docx

基于DSP和FPGA的光纤陀螺捷联惯导系统的硬件电路研究I.概览光纤陀螺捷联惯导系统(FiberOpticGyroInertialNavigationSystem,简称OGNS)是一种利用光纤陀螺仪和加速度计进行测量和计算的高精度惯性导航系统。随着科技的发展,光纤陀螺技术在惯导领域的应用越来越广泛。本文将对基于DSP和FPGA的光纤陀螺捷联惯导系统的硬件电路进行研究,以期为该领域的发展提供一定的参考价值。首先本文将介绍光纤陀螺的基本原理、结构和性能特点,以及其在惯导系统中的应用。然后针对基于DSP和FPG