一种可编程逻辑芯片的时钟偏移可调的芯片时钟架构.pdf

努力****骞北

亲,该文档总共12页,到这已经超出免费预览范围,如果喜欢就直接下载吧~

相关资料

一种可编程逻辑芯片的时钟偏移可调的芯片时钟架构.pdf

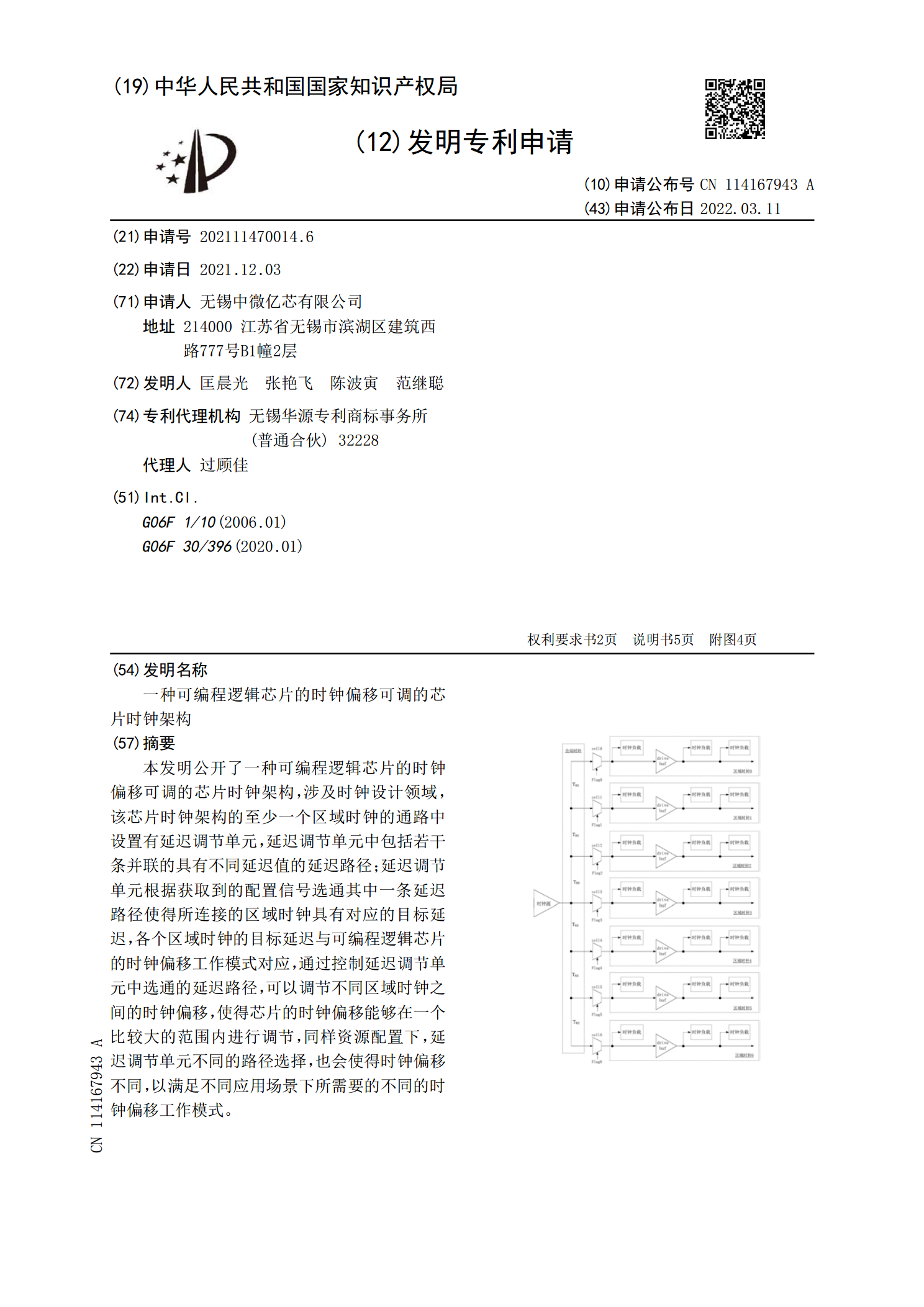

本发明公开了一种可编程逻辑芯片的时钟偏移可调的芯片时钟架构,涉及时钟设计领域,该芯片时钟架构的至少一个区域时钟的通路中设置有延迟调节单元,延迟调节单元中包括若干条并联的具有不同延迟值的延迟路径;延迟调节单元根据获取到的配置信号选通其中一条延迟路径使得所连接的区域时钟具有对应的目标延迟,各个区域时钟的目标延迟与可编程逻辑芯片的时钟偏移工作模式对应,通过控制延迟调节单元中选通的延迟路径,可以调节不同区域时钟之间的时钟偏移,使得芯片的时钟偏移能够在一个比较大的范围内进行调节,同样资源配置下,延迟调节单元不同的路

FPGA芯片时钟架构分析.docx

FPGA芯片时钟架构分析FPGA(Field-ProgrammableGateArray)芯片是一种可编程逻辑芯片,其具有灵活可编程性和高性能的特点,广泛应用于数字电路设计和嵌入式系统开发。在FPGA芯片中,时钟是其核心的组成部分之一,起着关键的作用。本文将对FPGA芯片的时钟架构进行分析,包括时钟树、时钟分配和时钟域划分等方面。首先,时钟树是FPGA芯片中实现时钟信号传输的重要组成部分。时钟树的主要任务是在整个芯片上分配时钟信号,并确保它们以稳定和准确的方式传播。时钟树通常由一个或多个主时钟源开始,然后

时钟芯片的扩展.ppt

1.DS1302DS1302是美国达拉斯(Dallas)半导体公司推出的一种高性能、低功耗、带RAM的实时时钟芯片,它可以对年、月、日、星期、时、分、秒进行计时,且具有闰年补偿功能。采用三线串行数据传输接口与CPU进行同步通信,内部有一个31B的高速RAM,工作电压范围为2.5~5.5V。2.MC146818MC146818是Motorola公司生产的时钟芯片。它支持时间(时、分、秒),也支持日期(世纪、年、月、日、星期)及闰月的自动调整。工作电流小(几A)。内部有64B的RAM,可设定报警时间(日、时

时钟芯片00.pptx

2024/2/72011年4月25日星期一2011年4月25日星期一2011年4月25日星期一2011年4月25日星期一2011年4月25日星期一2011年4月25日星期一2011年4月25日星期一2011年4月25日星期一2011年4月25日星期一2011年4月25日星期一2011年4月25日星期一2011年4月25日星期一2011年4月25日星期一2011年4月25日星期一2011年4月25日星期一2011年4月25日星期一2011年4月25日星期一2011年4月25日星期一2011年4月25日星期一

一种芯片时钟源检测电路及基于其的芯片时钟电路.pdf

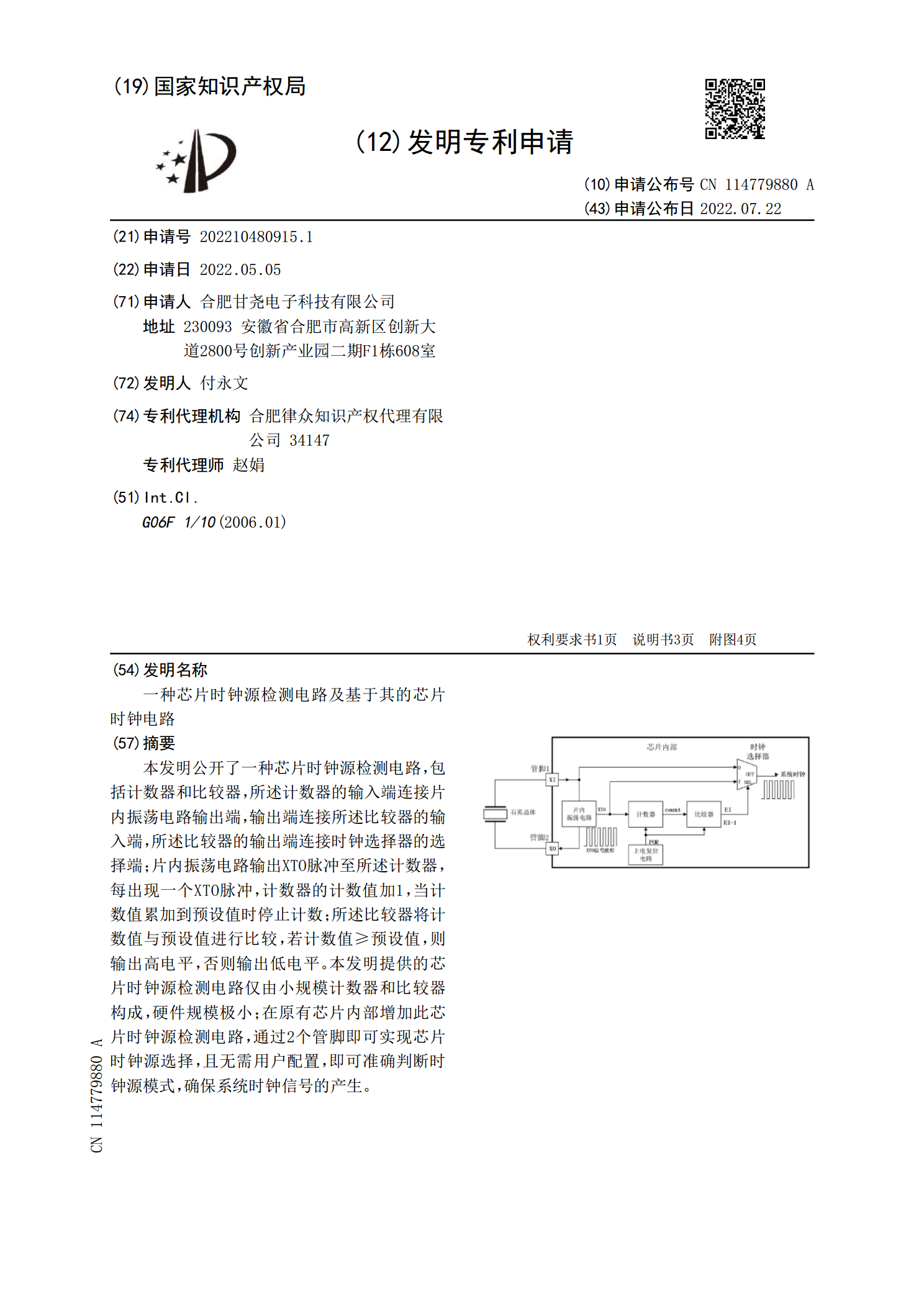

本实用新型公开了一种芯片时钟源检测电路,包括计数器和比较器,所述计数器的输入端连接片内振荡电路输出端,输出端连接所述比较器的输入端,所述比较器的输出端连接时钟选择器的选择端;片内振荡电路输出XTO脉冲至所述计数器,每出现一个XTO脉冲,计数器的计数值加1,当计数值累加到预设值时停止计数;所述比较器将计数值与预设值进行比较,若计数值≥预设值,则输出高电平,否则输出低电平。本实用新型提供的芯片时钟源检测电路仅由小规模计数器和比较器构成,硬件规模极小;在原有芯片内部增加此芯片时钟源检测电路,通过2个管脚即可实现