一种FPGA代码功能验证加速方法.pdf

霞英****娘子

在线预览结束,喜欢就下载吧,查找使用更方便

相关资料

一种FPGA代码功能验证加速方法.pdf

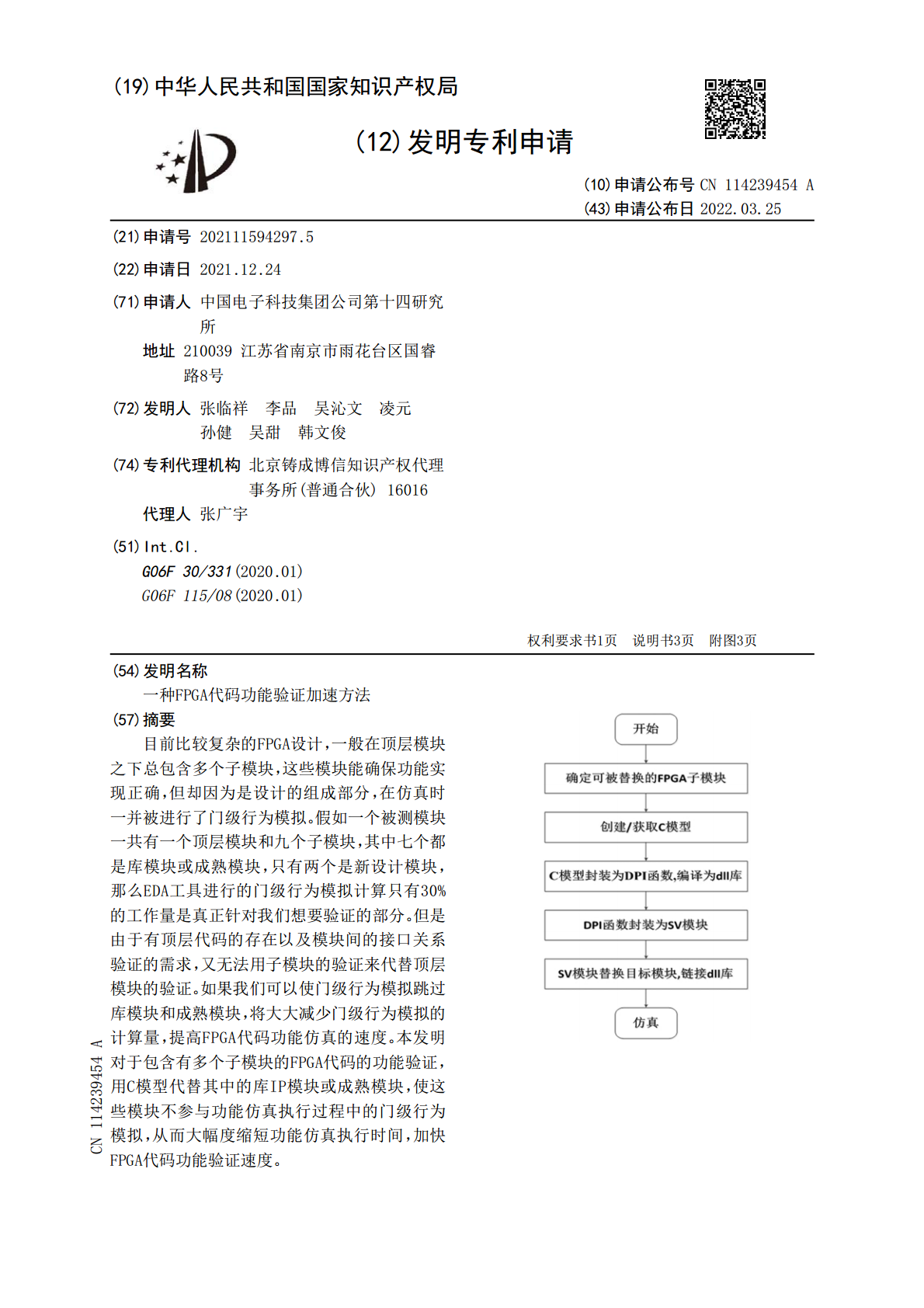

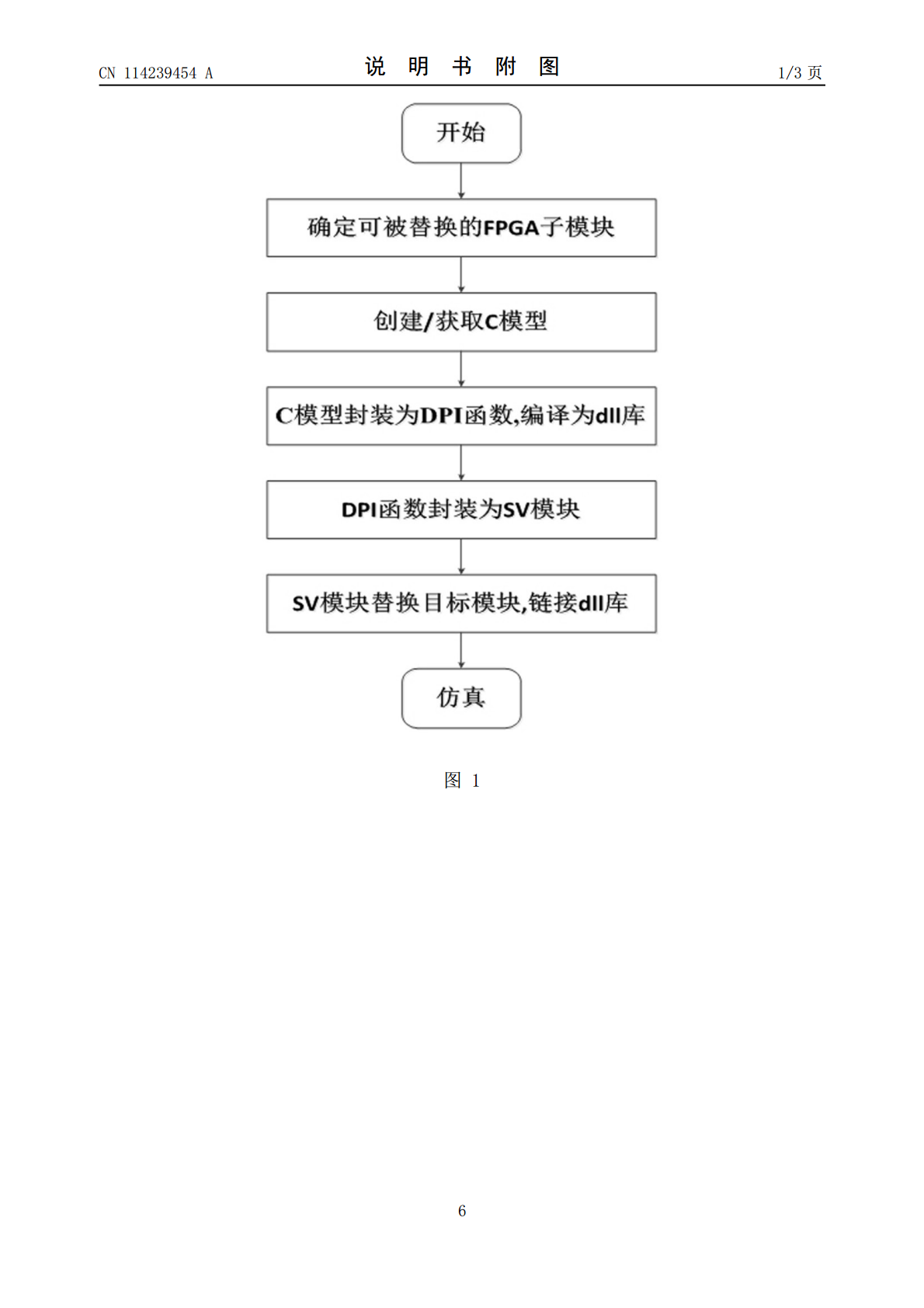

目前比较复杂的FPGA设计,一般在顶层模块之下总包含多个子模块,这些模块能确保功能实现正确,但却因为是设计的组成部分,在仿真时一并被进行了门级行为模拟。假如一个被测模块一共有一个顶层模块和九个子模块,其中七个都是库模块或成熟模块,只有两个是新设计模块,那么EDA工具进行的门级行为模拟计算只有30%的工作量是真正针对我们想要验证的部分。但是由于有顶层代码的存在以及模块间的接口关系验证的需求,又无法用子模块的验证来代替顶层模块的验证。如果我们可以使门级行为模拟跳过库模块和成熟模块,将大大减少门级行为模拟的计算

8位MCU功能测试及FPGA验证方法研究.docx

8位MCU功能测试及FPGA验证方法研究随着电子技术的不断发展,MCU芯片在各种应用场景中得到了广泛的应用。为了提高MCU芯片在不同应用场合下的可靠性和稳定性,需要对MCU芯片进行功能测试和验证。本文将探讨MCU芯片的功能测试及FPGA验证方法。一、MCU芯片功能测试的必要性MCU芯片是一种集成电路,它具有控制器、存储器、外设和时钟电路等基本部件,可用于控制各种电子设备。为了保证MCU芯片的质量和可靠性,需要对其进行功能测试。MCU芯片的功能测试是一个必要的过程,主要有以下几个方面的作用:1.保证MCU芯

代码验证系统和代码验证方法.pdf

本申请涉及一种代码验证系统和代码验证方法。系统包括:系统级芯片SOC模块、参考模块、对比模块、代理模块以及顶层模块,所述顶层模块包括:第一待测试模块和第二待测试模块,所述第一待测试模块采用第一语言代码生成,所述第二待测试模块采用第二语言代码生成,所述SOC模块通过所述代理模块分别与所述第一待测试模块和所述第二待测试模块连接,所述参考模块和所述对比模块连接,所述对比模块通过所述代理模块分别与所述第一待测试模块和所述第二待测试模块连接。实现了使用同一个验证系统,对两种不同的代码进行验证,解决了现有技术中维护两

8位MCU功能测试及FPGA验证方法研究的中期报告.docx

8位MCU功能测试及FPGA验证方法研究的中期报告中期报告一、项目内容和目标本项目的内容是研究8位MCU的功能测试及FPGA验证方法,目标是建立基于FPGA的8位MCU验证系统,对8位MCU进行功能测试和验证,为8位MCU的应用开发提供可靠的测试和验证手段。二、项目进展情况1.理论研究在项目启动后,团队成员进行了相关领域的理论研究和文献阅读,并对研究方向和方法进行了充分探讨和讨论。2.硬件设计在理论研究的基础上,团队成员开始进行硬件设计。首先,根据8位MCU的特性、指令集和外围接口,选定了一款常用的8位M

卷积神经网络的卷积加速研究及FPGA验证.docx

卷积神经网络的卷积加速研究及FPGA验证卷积神经网络(ConvolutionalNeuralNetworks,CNN)是一类深度学习模型,在计算机视觉和图像识别等领域取得了显著的突破。然而,随着CNN模型结构的不断复杂化和数据规模的增大,其计算量也呈指数级增长,给计算资源带来了巨大的压力。因此,研究如何加速卷积神经网络的计算过程成为了一个重要的课题。本文将探讨卷积神经网络的卷积加速方法,并结合FPGA进行验证。首先,我们将介绍卷积神经网络的基本原理和结构。卷积神经网络由多个卷积层、激活函数层和池化层等组成