显示面板的驱动电路、驱动方法和显示装置.pdf

纪阳****公主

亲,该文档总共22页,到这已经超出免费预览范围,如果喜欢就直接下载吧~

相关资料

显示面板的驱动电路、驱动方法和显示装置.pdf

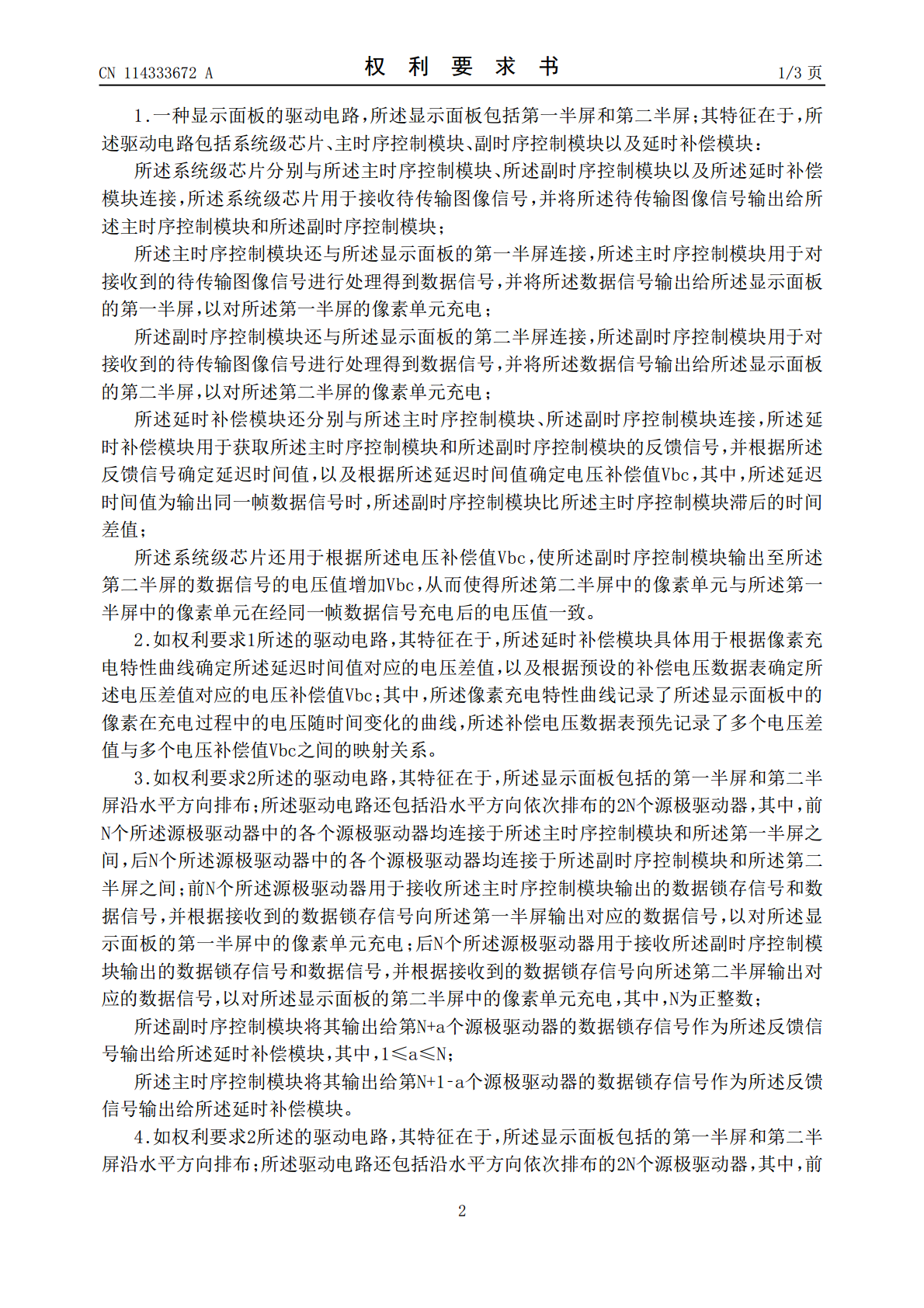

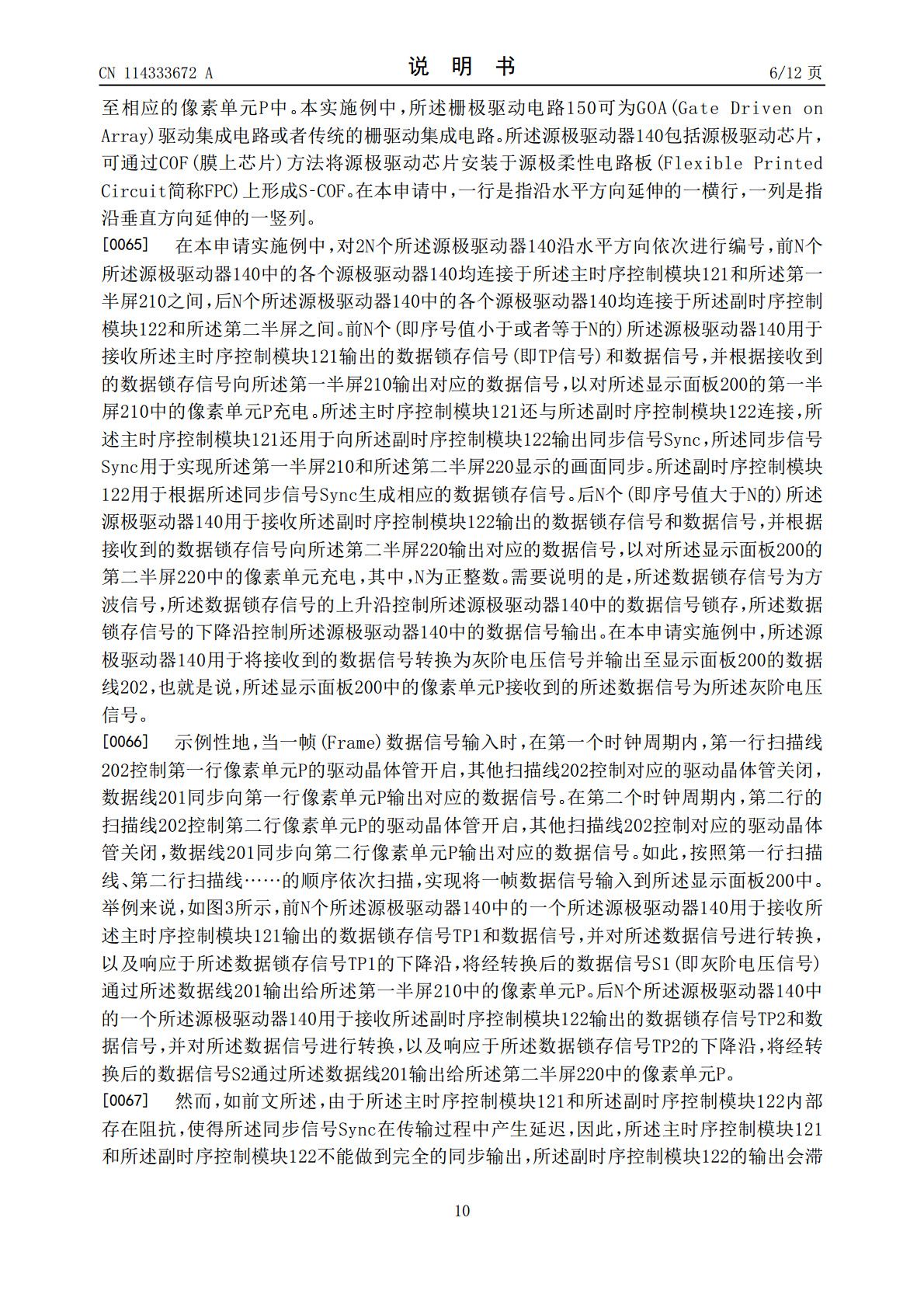

本申请提供一种显示面板的驱动电路、驱动方法和显示装置。显示面板包括第一半屏和第二半屏,驱动电路包括主时序控制模块、副时序控制模块、系统级芯片以及延时补偿模块,延时补偿模块根据主时序控制模块和副时序控制模块的反馈信号确定电压补偿值Vbc。系统级芯片根据电压补偿值Vbc,使副时序控制模块输出至第二半屏的数据信号的电压值增加Vbc,使得第二半屏中的像素单元与第一半屏中的像素单元在经同一帧数据信号充电后的电压值一致。本申请提供的驱动电路,通过检测延迟时间值,增加副时序控制模块输出的数据信号的电压值,使得第二半屏中

显示面板的驱动方法、驱动电路、显示面板及显示装置.pdf

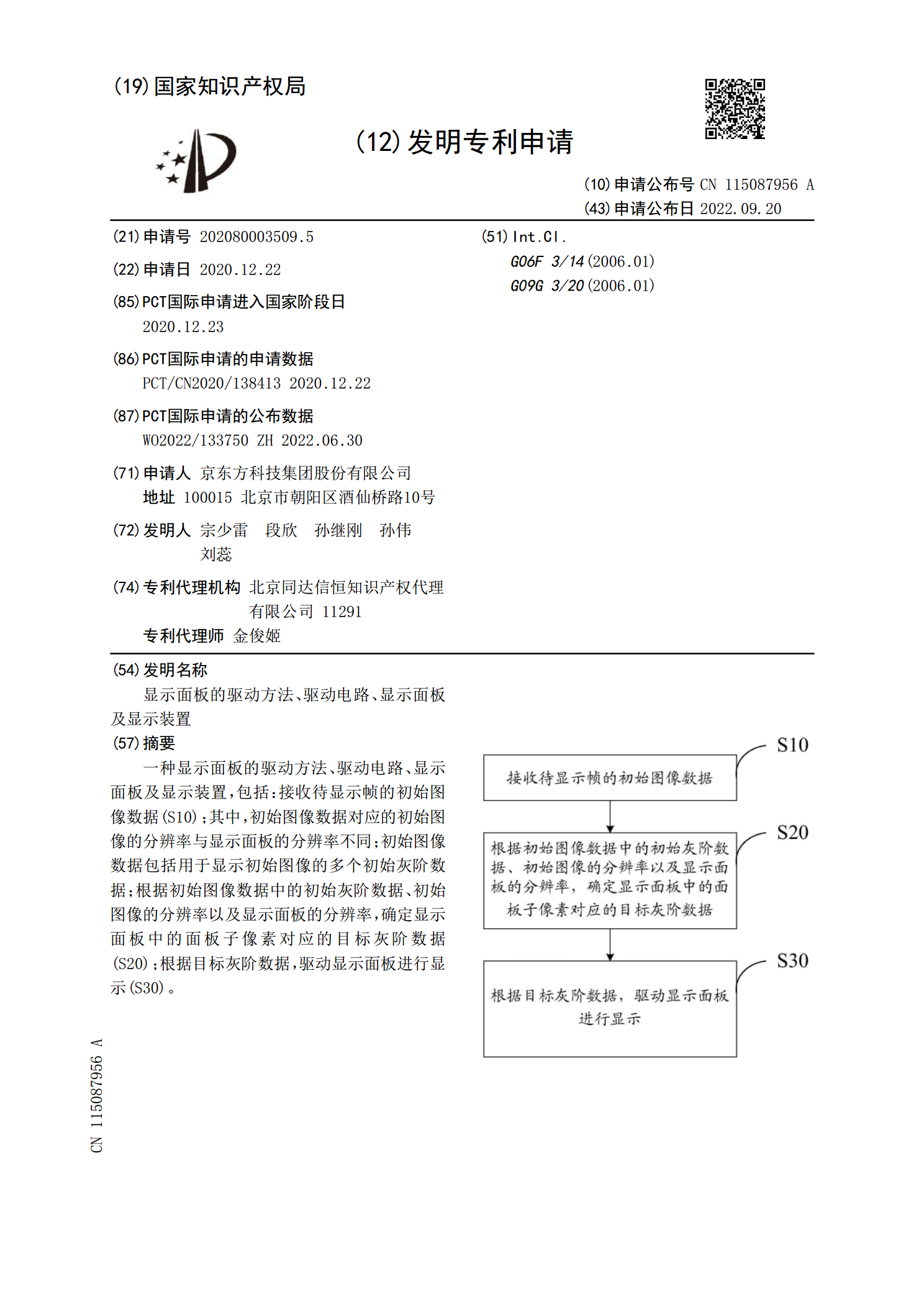

一种显示面板的驱动方法、驱动电路、显示面板及显示装置,包括:接收待显示帧的初始图像数据(S10);其中,初始图像数据对应的初始图像的分辨率与显示面板的分辨率不同;初始图像数据包括用于显示初始图像的多个初始灰阶数据;根据初始图像数据中的初始灰阶数据、初始图像的分辨率以及显示面板的分辨率,确定显示面板中的面板子像素对应的目标灰阶数据(S20);根据目标灰阶数据,驱动显示面板进行显示(S30)。

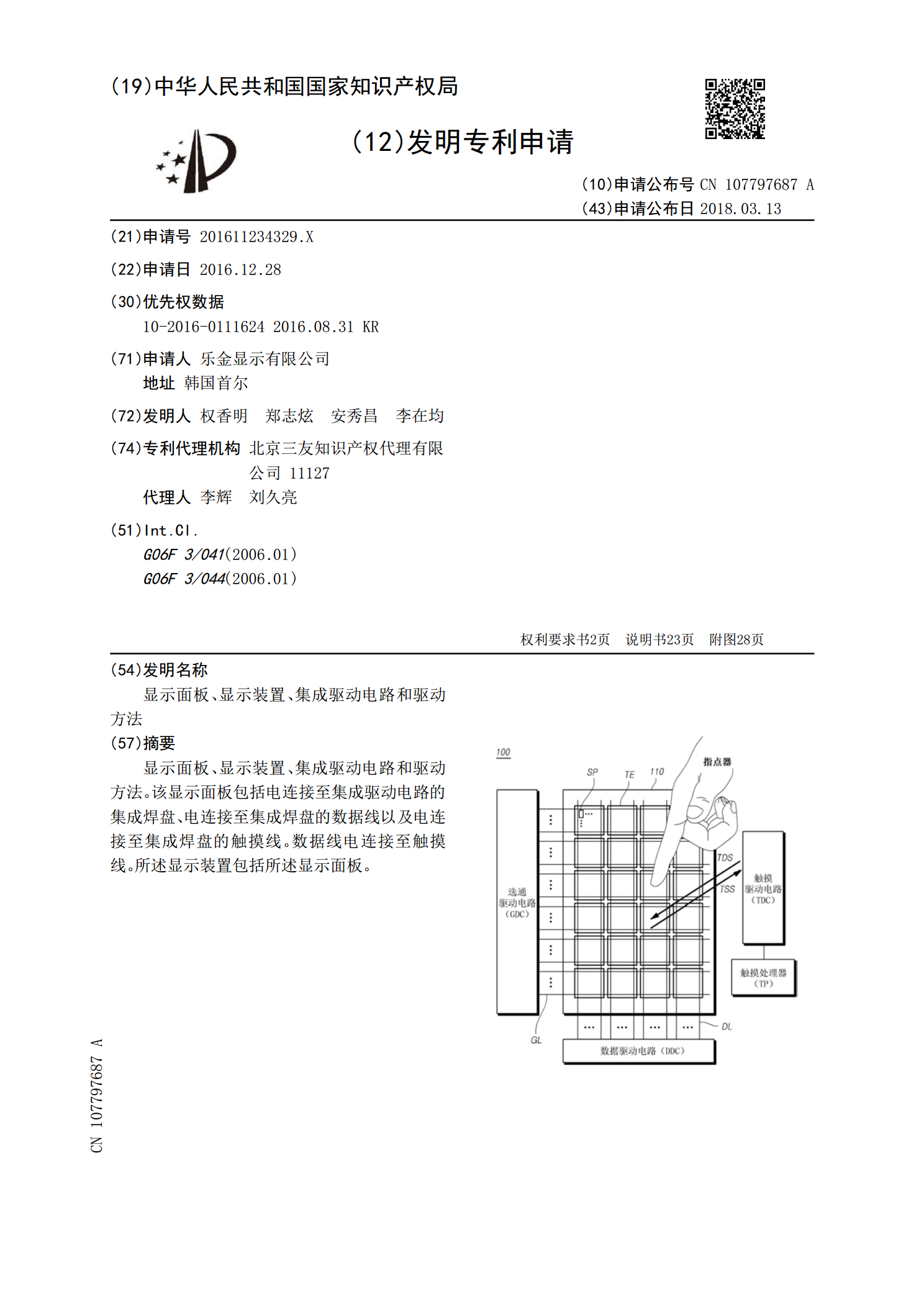

显示面板、显示装置、集成驱动电路和驱动方法.pdf

显示面板、显示装置、集成驱动电路和驱动方法。该显示面板包括电连接至集成驱动电路的集成焊盘、电连接至集成焊盘的数据线以及电连接至集成焊盘的触摸线。数据线电连接至触摸线。所述显示装置包括所述显示面板。

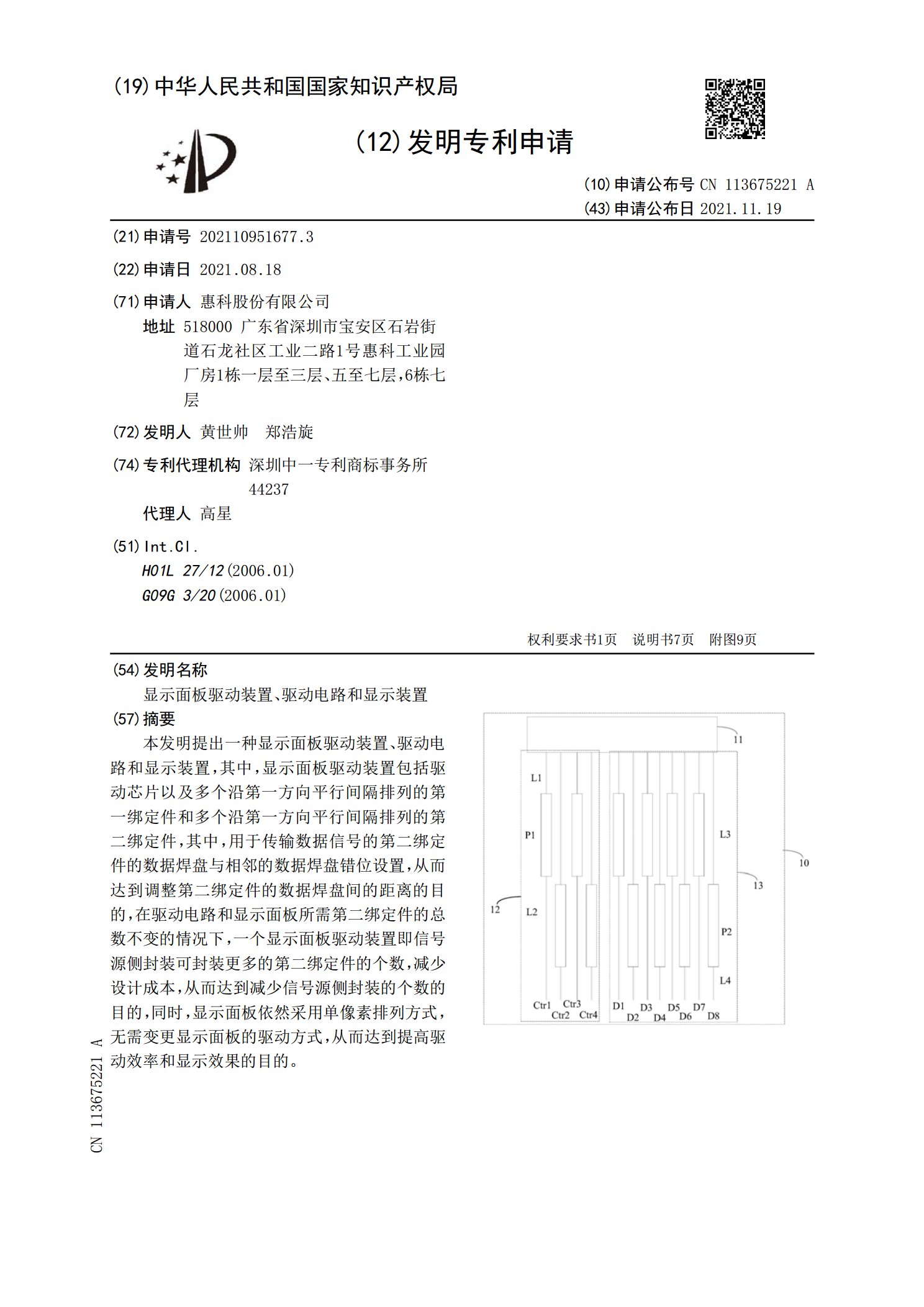

显示面板驱动装置、驱动电路和显示装置.pdf

本发明提出一种显示面板驱动装置、驱动电路和显示装置,其中,显示面板驱动装置包括驱动芯片以及多个沿第一方向平行间隔排列的第一绑定件和多个沿第一方向平行间隔排列的第二绑定件,其中,用于传输数据信号的第二绑定件的数据焊盘与相邻的数据焊盘错位设置,从而达到调整第二绑定件的数据焊盘间的距离的目的,在驱动电路和显示面板所需第二绑定件的总数不变的情况下,一个显示面板驱动装置即信号源侧封装可封装更多的第二绑定件的个数,减少设计成本,从而达到减少信号源侧封装的个数的目的,同时,显示面板依然采用单像素排列方式,无需变更显示面

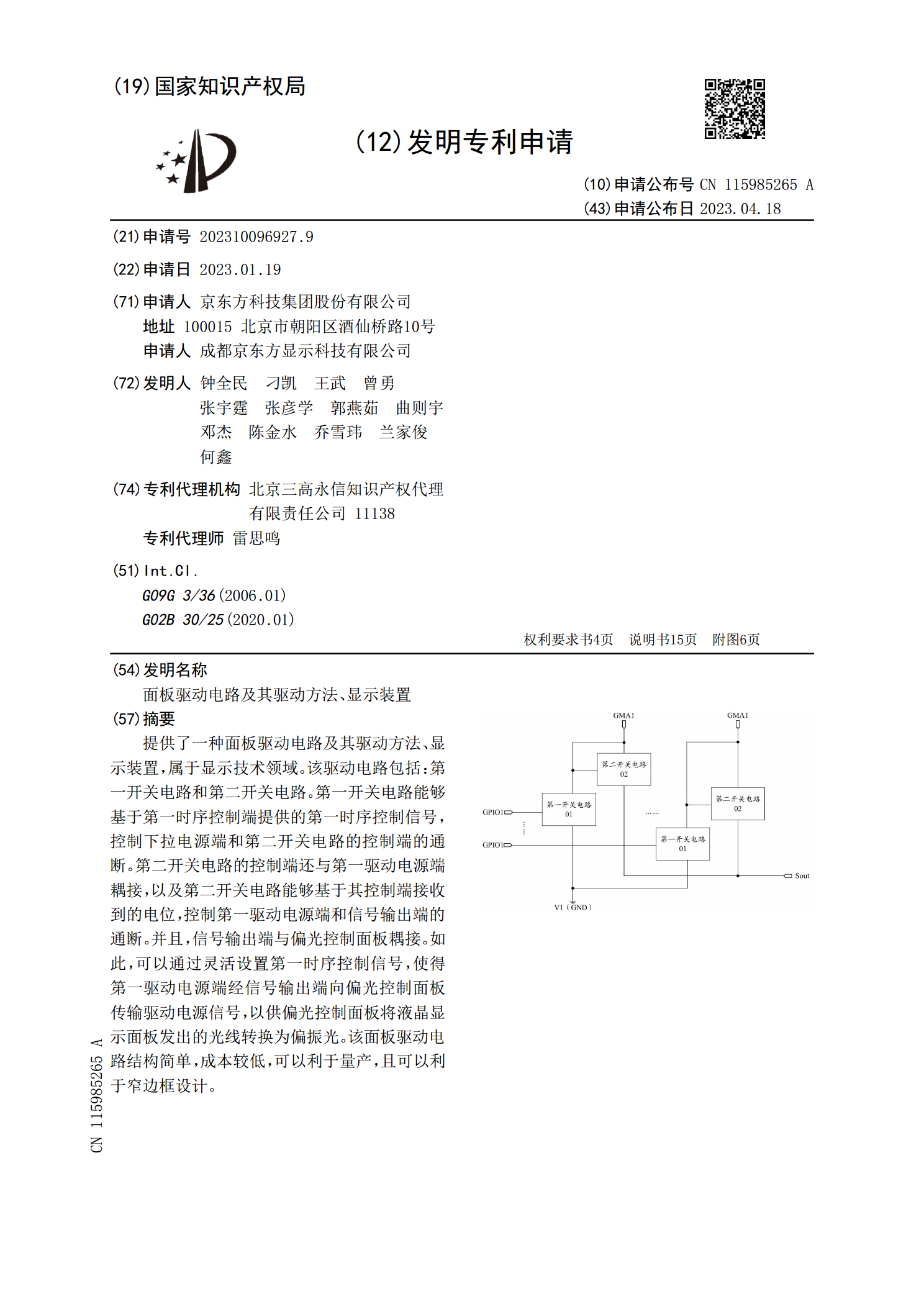

面板驱动电路及其驱动方法、显示装置.pdf

提供了一种面板驱动电路及其驱动方法、显示装置,属于显示技术领域。该驱动电路包括:第一开关电路和第二开关电路。第一开关电路能够基于第一时序控制端提供的第一时序控制信号,控制下拉电源端和第二开关电路的控制端的通断。第二开关电路的控制端还与第一驱动电源端耦接,以及第二开关电路能够基于其控制端接收到的电位,控制第一驱动电源端和信号输出端的通断。并且,信号输出端与偏光控制面板耦接。如此,可以通过灵活设置第一时序控制信号,使得第一驱动电源端经信号输出端向偏光控制面板传输驱动电源信号,以供偏光控制面板将液晶显示面板发出