微机接口第2章 8086与80x86系列微处理器.ppt

17****92

亲,该文档总共108页,到这已经超出免费预览范围,如果喜欢就直接下载吧~

相关资料

微机接口第2章 8086与80x86系列微处理器.ppt

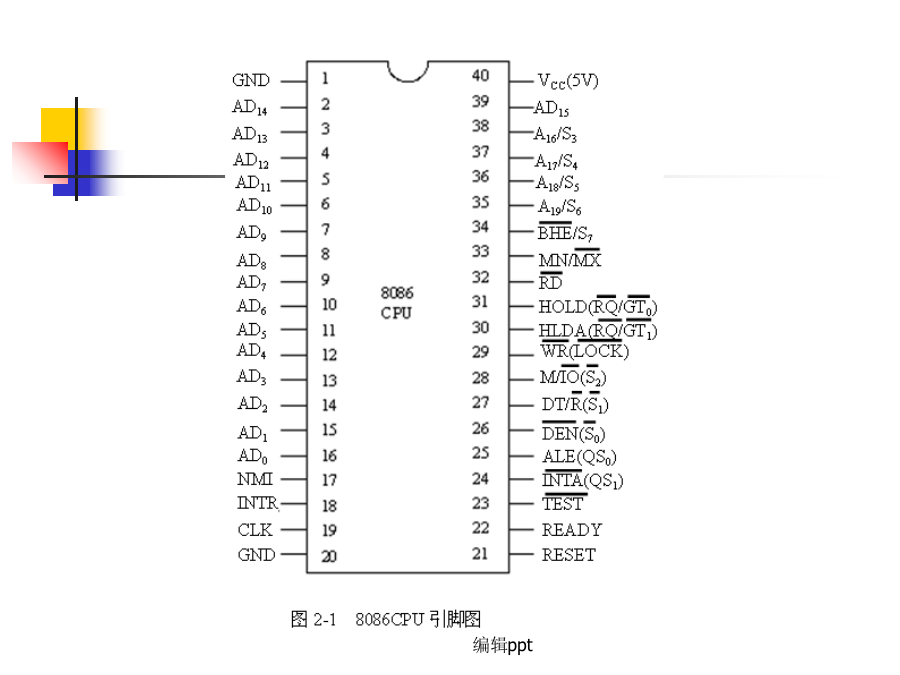

微机原理与接口技术第2章8086与80x86系列微处理器【本章内容提要】2.18086微处理器概览2.1.1引脚定义与功能编辑ppt通过将MN/MX接高电平或地,可使CPU工作在最小模式或最大模式下。最小模式是单机系统,系统中所需的控制信号全部由8086CPU本身直接产生;最大模式可以构成多处理机系统,系统所需的控制信号由总线控制器提供。在不同模式下,8086CPU的第24~31引脚的定义是不同的,下面会详细解释。1.地址/数据总线2.地址/状态总线S6:指示CPU当前是否连在总线上。S6=0表示CPU当

微机原理与接口 第3章2—8086微处理器总线周期及引脚.ppt

3.2.38086微处理器的总线时序1.总线时序⑴指令周期每条指令的执行由取指令、译码和执行等操作组成,执行一条指令所需要的时间称为指令周期(InstructionCycle),不同指令的指令周期是不等长的,一个指令周期由一个或若干个总线周期组成。⑵总线周期8086CPU与外部交换信息总是通过总线进行的。CPU的每一个这种信息输入、输出过程所需要的时间称为总线周期(BusCycle),一般一个总线周期由四个时钟周期组成。⑶时钟周期时钟脉冲的重复周期称为时钟周期(ClockCycle)。时钟周期是CPU的时

微机原理与接口 第3章1—8086微处理器内部及寄存器结构.ppt

第3章80X86微处理器及其体系结构3.180x86微处理器简介2.数据总线从8086的16位到80586的64位。数据总线是计算机中组成各部件间进行数据传送时的公共通道。其位数(宽度)表示CPU的字长,数据总线位数越多,数据交换的速度越快。3.地址总线从8086的20根到80586的32根。地址总线是在对存储器或I/O端口进行访问时,传送由CPU提供的要访问的存储单元或I/O端口的地址信息总线,其宽度决定了处理器能直接访问的主存容量大小。表3.180x86系列微处理器概况微型计算机是由具有不同功能的一些

微机原理与接口 第3章3—8086微处理器存储器和IO组织.ppt

3.38086/8088存储器和I/O组织3.3.18086/8088存储器组织1.存储器组织8086/8088微处理器有20条地址线,可以配置1MB的内存储器。存储空间都按8位(即字节)进行组织,每个存储单元存储一个字节数据,若存放“字”数据(16位),则存放在相邻两个存储单元中,高字节存放在高地址单元,低字节存放在低地址单元。每个存储单元都有一个20位的地址,这1M个存储单元对应的地址为00000HFFFFFH,如图3.10所示。78H高位(奇地址)库地址总线A19A1可同时对高、低位库的存储单元

微机原理第2章 80x86微处理器.ppt

第2章80x86微处理器教学内容2.1微处理器的发展2.28086微处理器2.2.18086CPU内部功能结构2.2.28086CPU内部流水线管理工作原理2.2.28086CPU的存储器组织2.2.28086CPU总线周期的概念2.2.28086CPU引脚信号及工作模式2.2.28086CPU的操作时序教学目标1了解80X86微处理器的发展历史。2理解8086微处理器内部结构、总线周期、操作时序。3掌握8086存储器组织、引脚及工作模式。4理解8086操作时序。重点内容18086微处理器内部结构。280