锁相式数字频率合成器实验报告..pdf

文库****品店

亲,该文档总共19页,到这已经超出免费预览范围,如果喜欢就直接下载吧~

相关资料

锁相式数字频率合成器实验报告..pdf

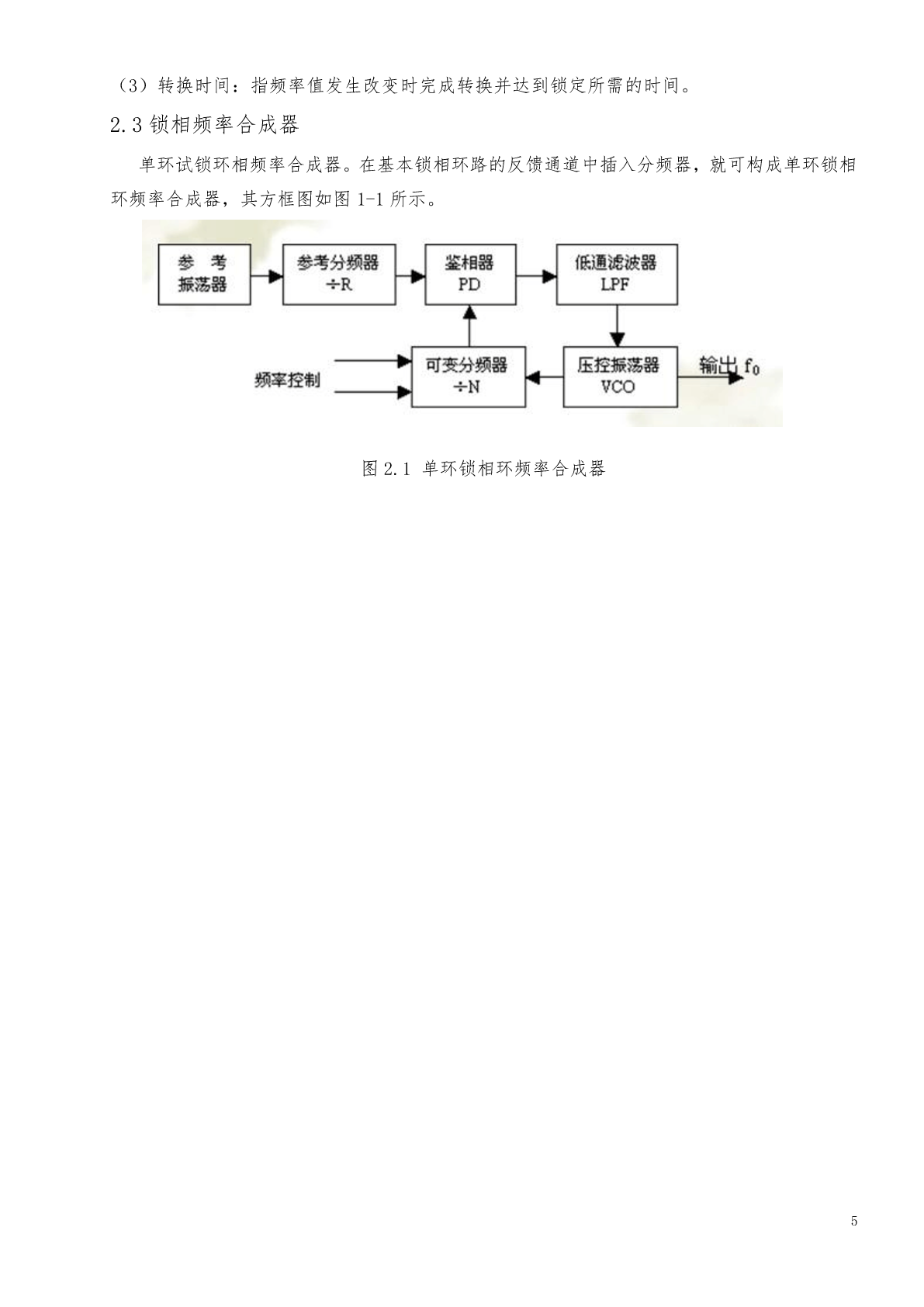

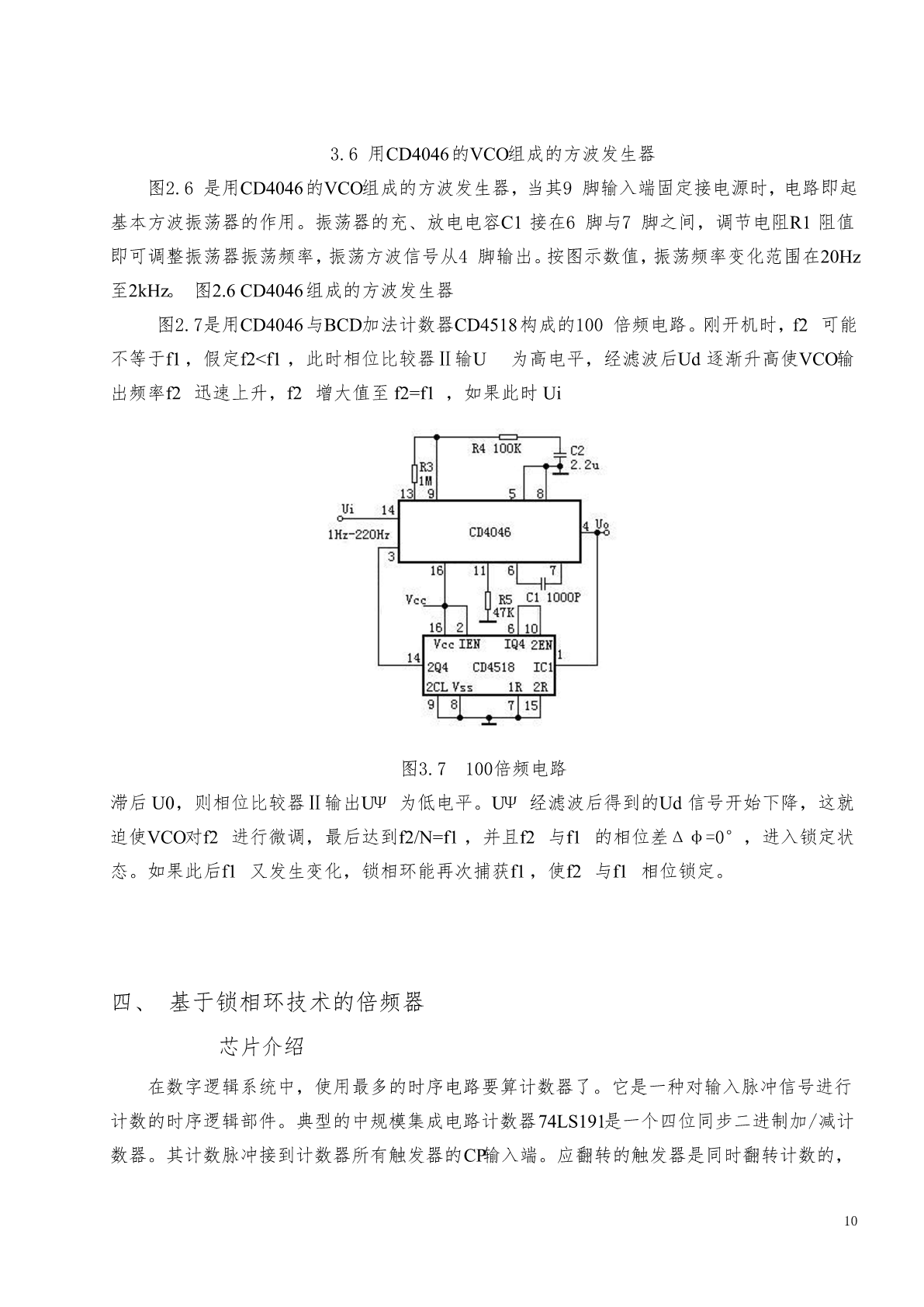

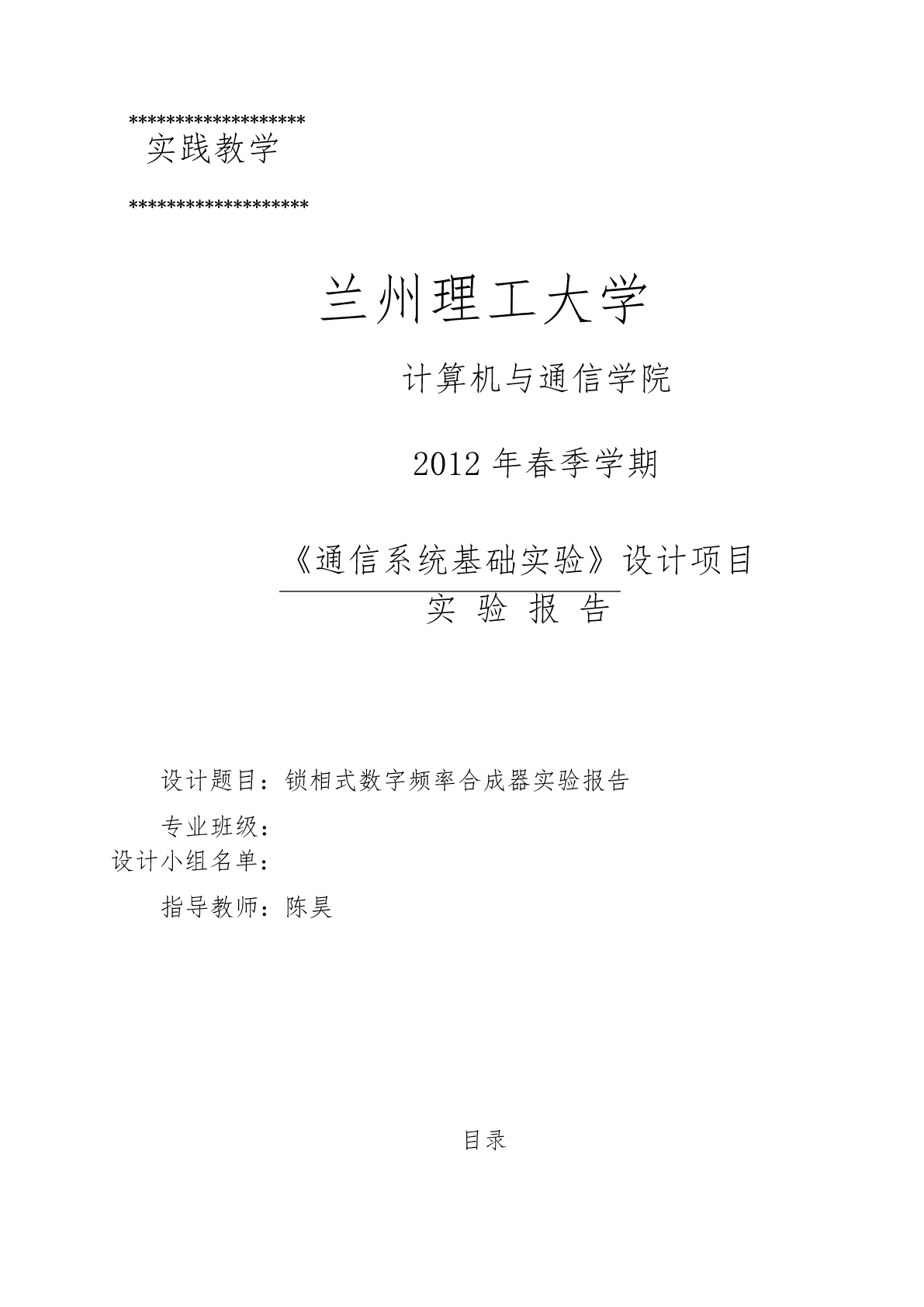

*******************实践教学*******************兰州理工大学计算机与通信学院2012年春季学期《通信系统基础实验》设计项目实验报告设计题目:锁相式数字频率合成器实验报告专业班级:设计小组名单:指导教师:陈昊目录一、设计实验目的...............................................................3二、频率合成基本原理..................................................

S波段数字锁相频率合成器设计的中期报告.docx

S波段数字锁相频率合成器设计的中期报告一、设计思路本设计采用S波段数字锁相频率合成器,主要采用了256个相位点的DDS方案,通过相位累加的方法实现频率输出。具体实现方法如下所述:1.生成参考时钟采用晶振产生一个10MHz的基准时钟,经过分频后得到参考时钟信号。2.产生相位步进信号在256个相位点的范围内,通过计算出步进值,产生相位步进信号。每经过一个相位点,就相当于合成的频率增加了一个微小的量,从而实现另一种频率的输出。3.相位累加器相位累加器用于对每个相位步进信号进行累加,随着累加数量的不同,可以产生不

宽带锁相式频率合成器快速锁定模式研究的开题报告.docx

宽带锁相式频率合成器快速锁定模式研究的开题报告一、研究背景随着通信技术的发展,频率合成器在通信系统中的作用越来越重要。频率合成器能够把低频信号(如晶体振荡器产生的信号)合成出高频信号。在现代通信系统中,频率合成器广泛应用于无线通信、卫星通信、数字电视、雷达等领域。宽带锁相式频率合成器是一种常用的频率合成器,它采用锁相环来实现高精度的频率合成。然而,在实际应用中,频率合成器在快速锁定模式下可能会出现锁定时间过长的问题,影响系统的性能和稳定性。因此,研究宽带锁相式频率合成器的快速锁定模式,对于提高通信系统的性

锁相频率合成器的电磁兼容设计.docx

锁相频率合成器的电磁兼容设计摘要为了提高锁相频率合成器抗电磁干扰的能力通过对锁相频率合成器电磁干扰三要素(电磁干扰源、传输途径和敏感设备)的分析从限制干扰源的电磁发射、控制电磁干扰的传播及增强敏感设备的抗干扰能力三条途径开展锁相频率合成器的电磁兼容设计研究并提出锁相频率合成器电磁兼容设计原则。【关键词】电磁兼容电磁干扰锁相频率合成器电磁兼容设计随着电子信息技术的飞速发展众多功能各异的电子设备被设计生产出来并投入使用。这些电子设备在给人们带

基于锁相环的频率合成器的设计与制作.doc

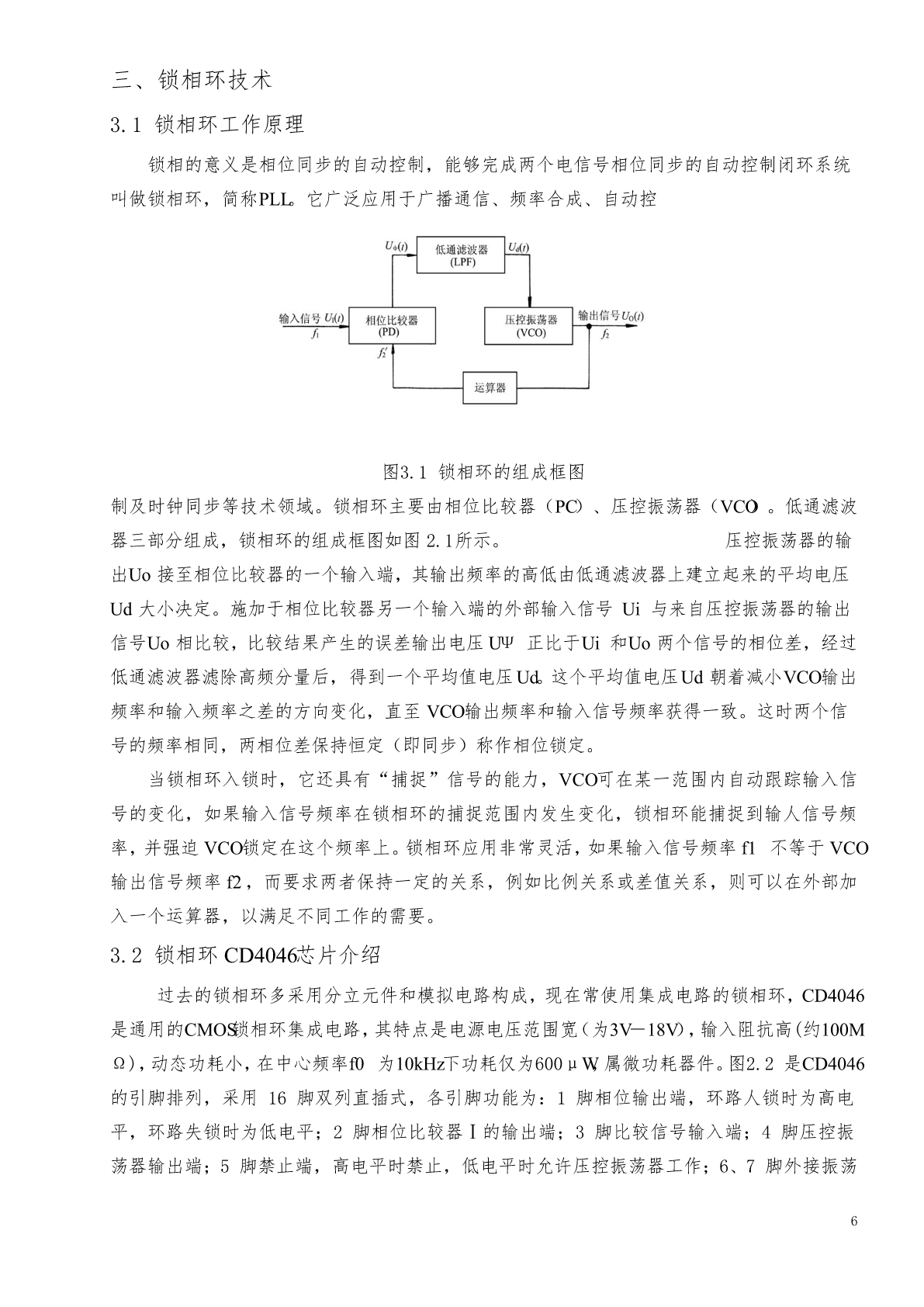

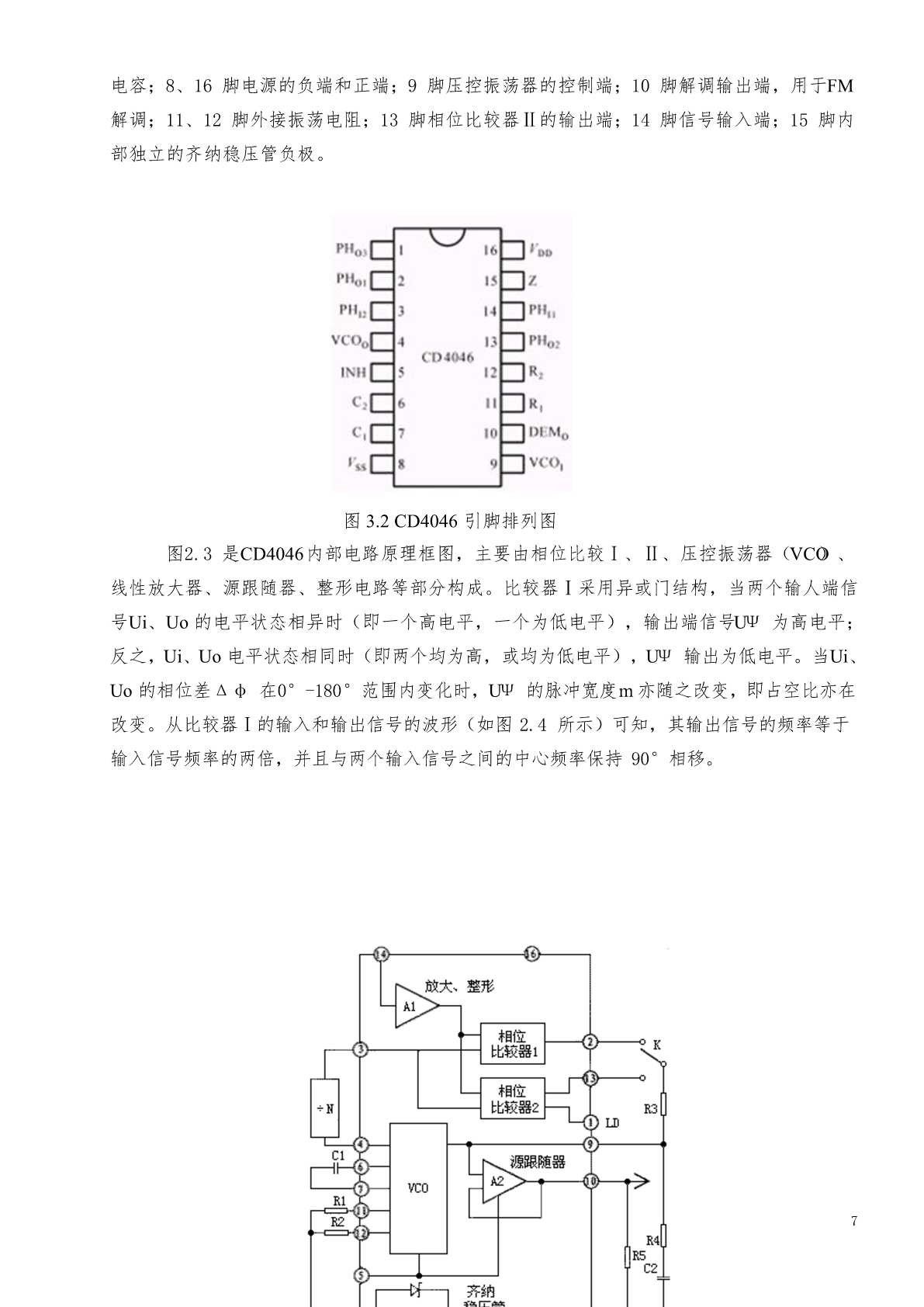

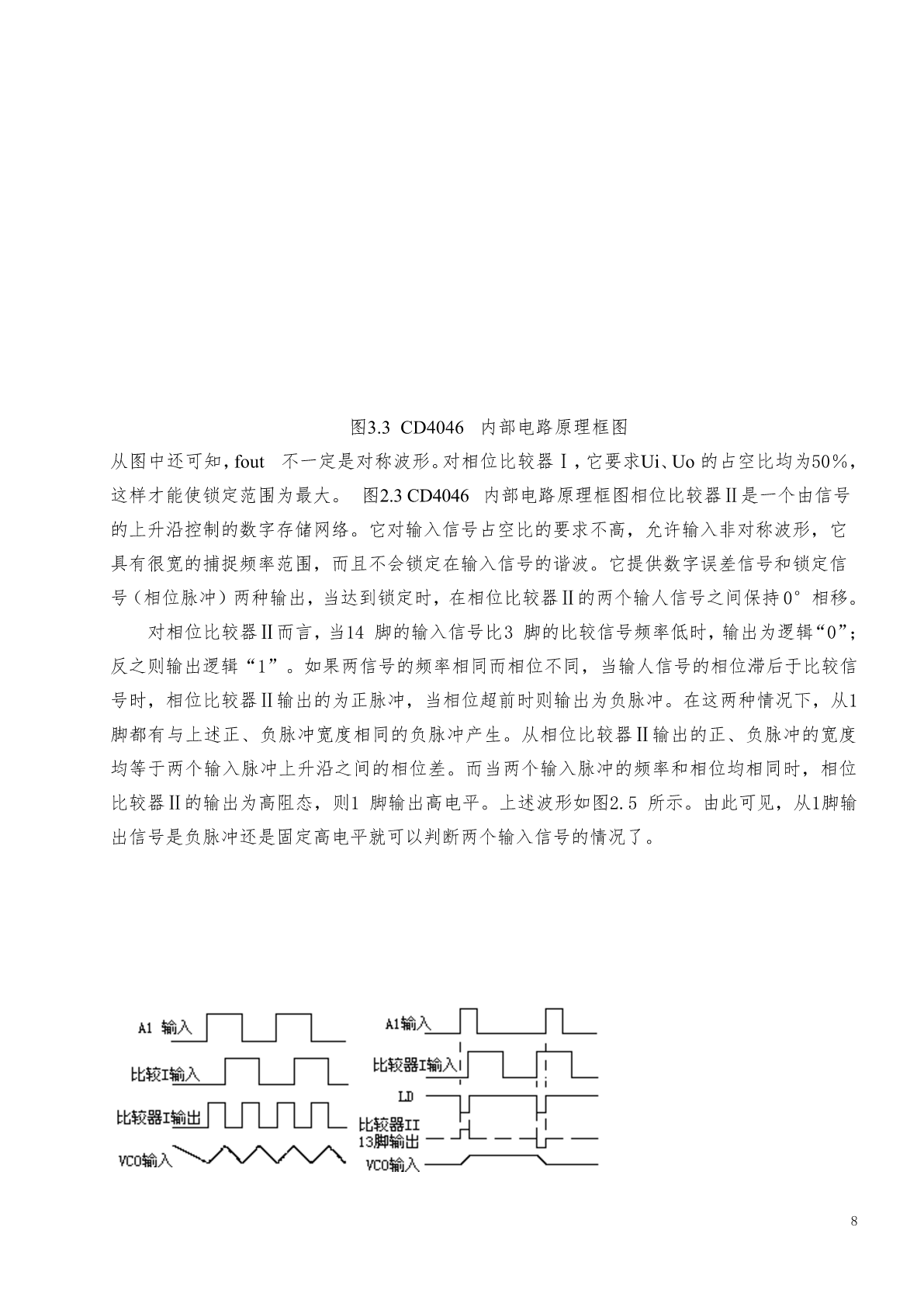

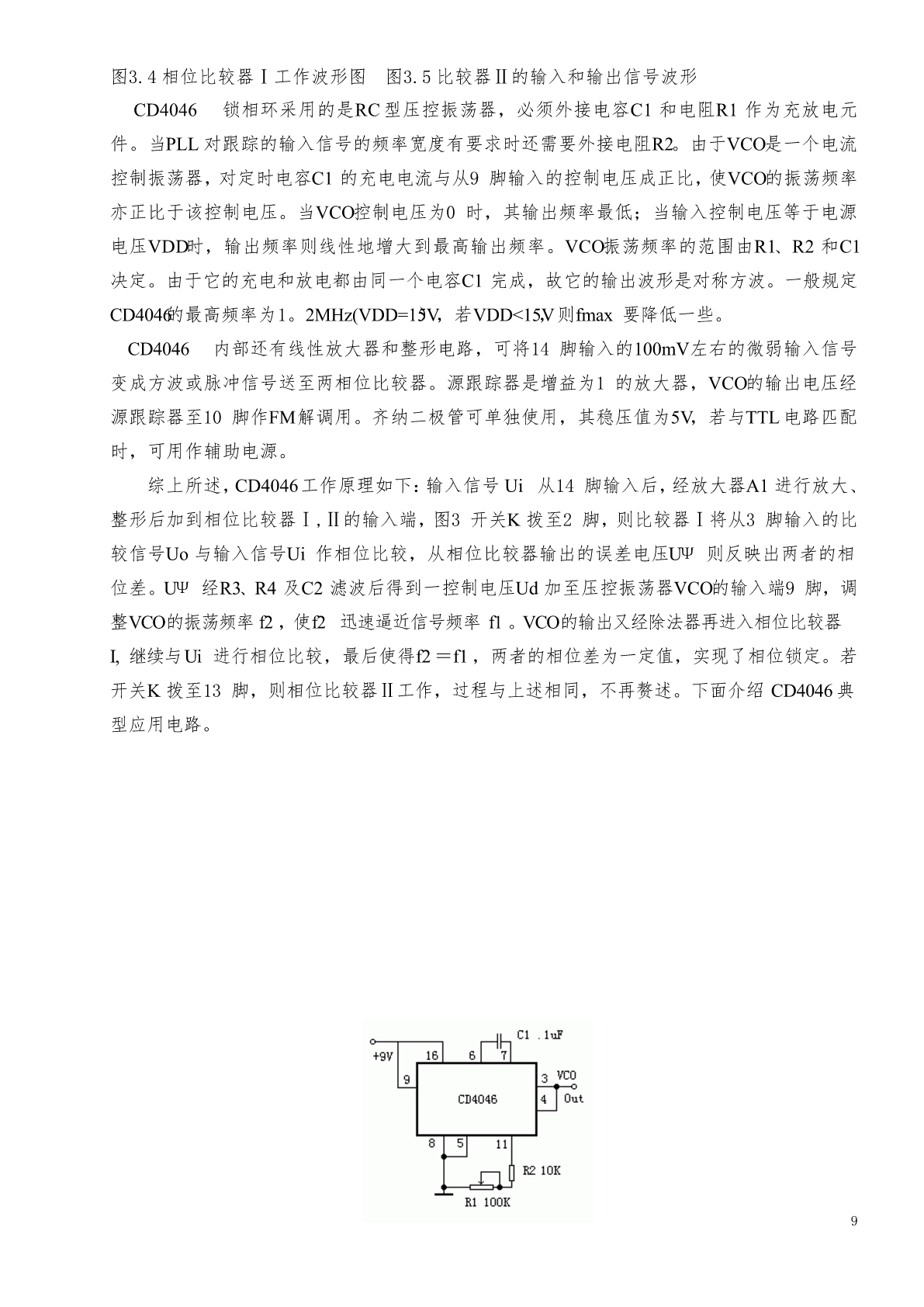

锁相环电路的应用设计与制作一、目的通过对锁相环电路应用设计,进一步加深对锁相环电路工作原理的理解,熟悉锁相环电路的基本形式,掌握集成锁相环电路的测试及应用方法;了解锁相环的相位捕捉的特性检测方法;熟悉单片锁相环集成电路和外围分频集成电路的基本电路应用形式;掌握电路的调整及测量方法;掌握锁相环电路的主要指标参数,为今后的实际工程应用,奠定坚实的基础。二、要求锁相环(PLL)电路是一种反馈控制电路。图1-1所示是基本锁相环电路的框图。图1-1基本锁相环电路框图当相位比较器的两个输入的相位差(θi-θo)不变时