一种基于测试信号的TIADC时间误差的半盲校正方法.pdf

睿德****找我

在线预览结束,喜欢就下载吧,查找使用更方便

相关资料

一种基于测试信号的TIADC时间误差的半盲校正方法.pdf

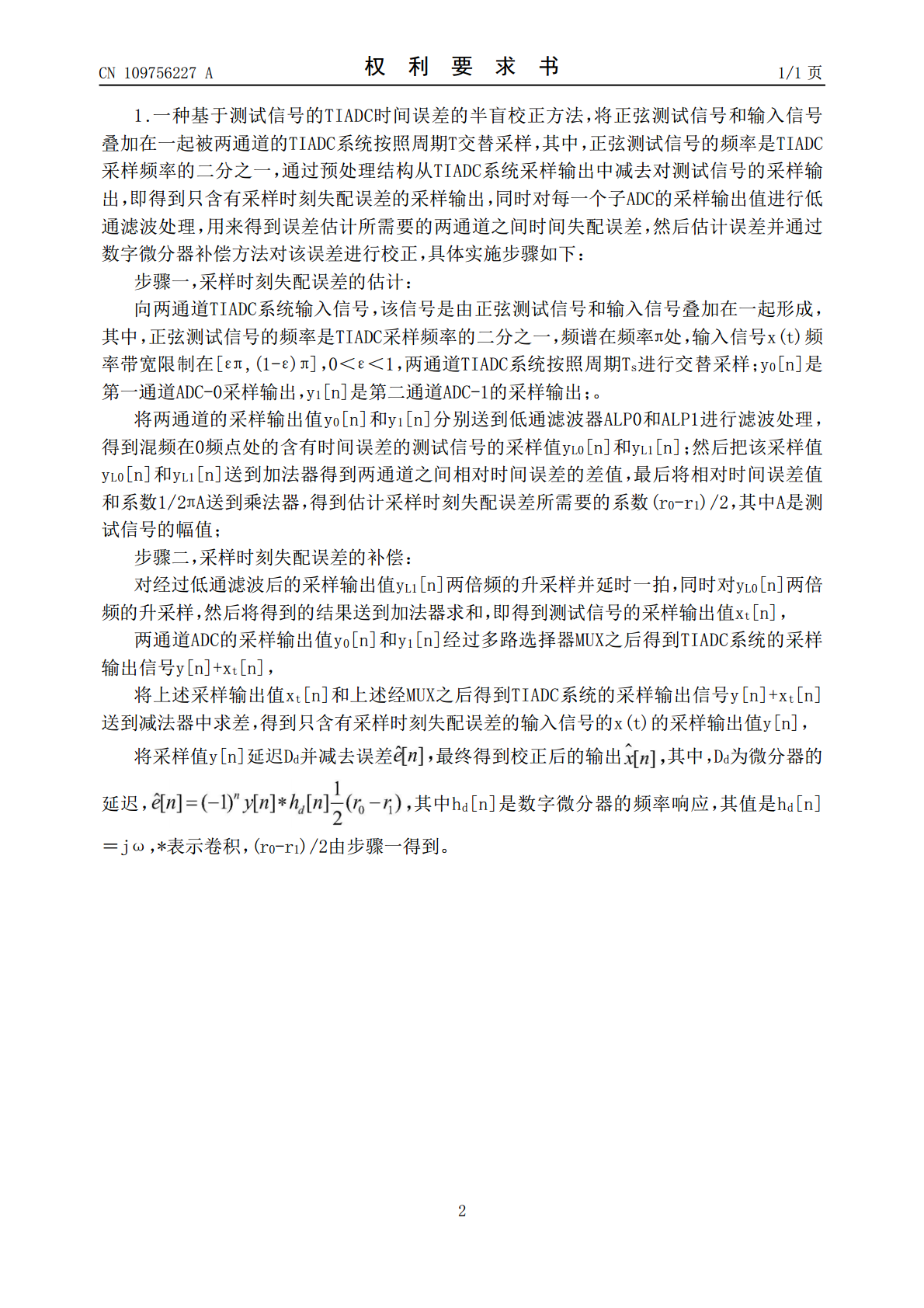

本发明涉及一种基于测试信号的TIADC时间误差的半盲校正方法,该方法引入一个频率为二分之一的TIADC系统采样频率的正弦测试信号,将该测试信号和输入信号叠加在一起被两通道的TIADC系统采样,通过低通滤波器得到混叠在0频点处的测试信号和通道之间相对采样时刻的失配误差,计算出误差估计所需要的系数,然后将测试信号从TIADC的采样输出结果中去除掉,最后通过误差补偿结构得到采样时刻失配误差实时校正后的输出。本方法采用了两个低通滤波器对测试信号进行预处理,避免了对TIADC的校正后输出再进行滤波处理的要求,降低了

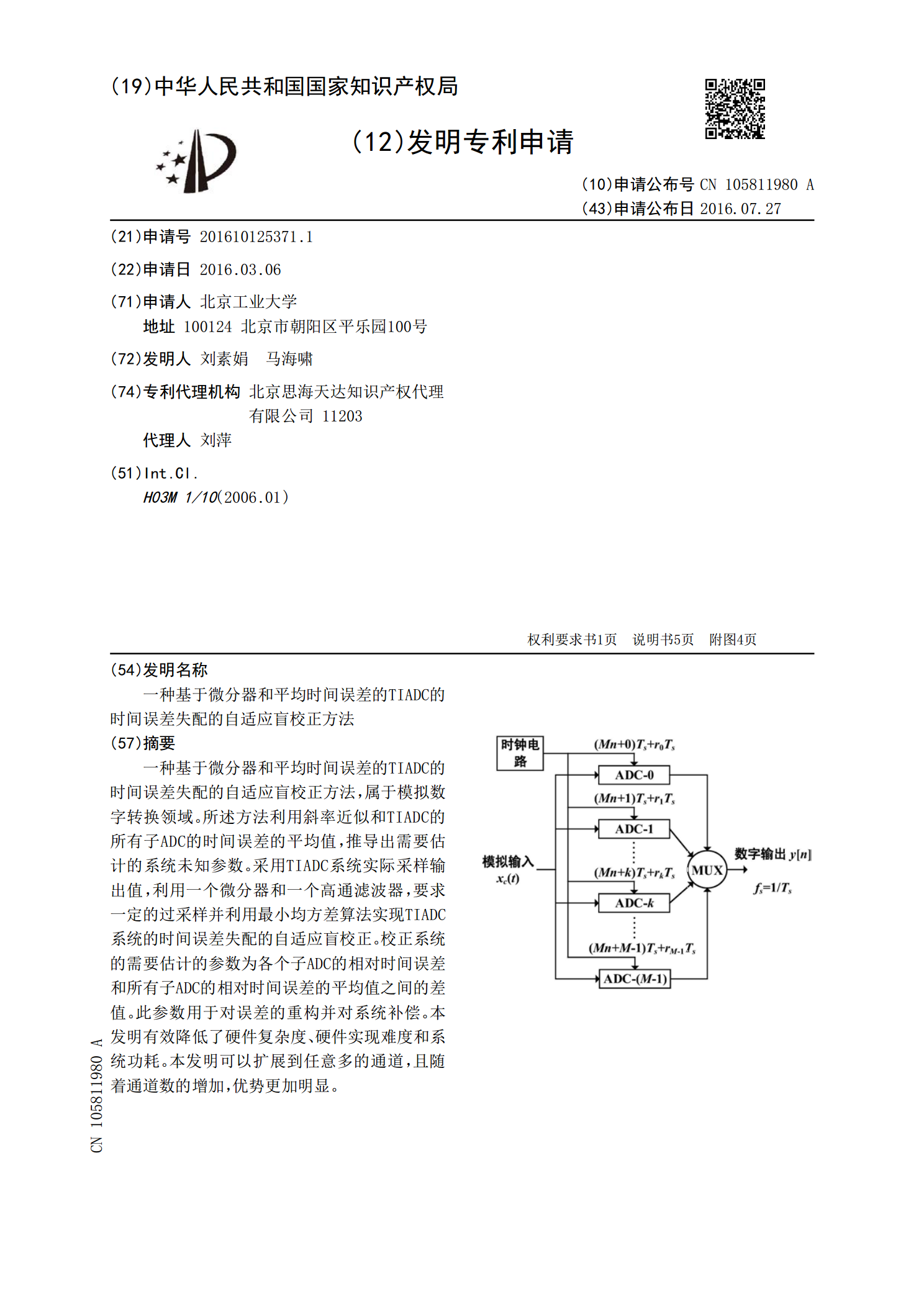

一种基于微分器和平均时间误差的TIADC的时间误差失配的自适应盲校正方法.pdf

一种基于微分器和平均时间误差的TIADC的时间误差失配的自适应盲校正方法,属于模拟数字转换领域。所述方法利用斜率近似和TIADC的所有子ADC的时间误差的平均值,推导出需要估计的系统未知参数。采用TIADC系统实际采样输出值,利用一个微分器和一个高通滤波器,要求一定的过采样并利用最小均方差算法实现TIADC系统的时间误差失配的自适应盲校正。校正系统的需要估计的参数为各个子ADC的相对时间误差和所有子ADC的相对时间误差的平均值之间的差值。此参数用于对误差的重构并对系统补偿。本发明有效降低了硬件复杂度、硬件

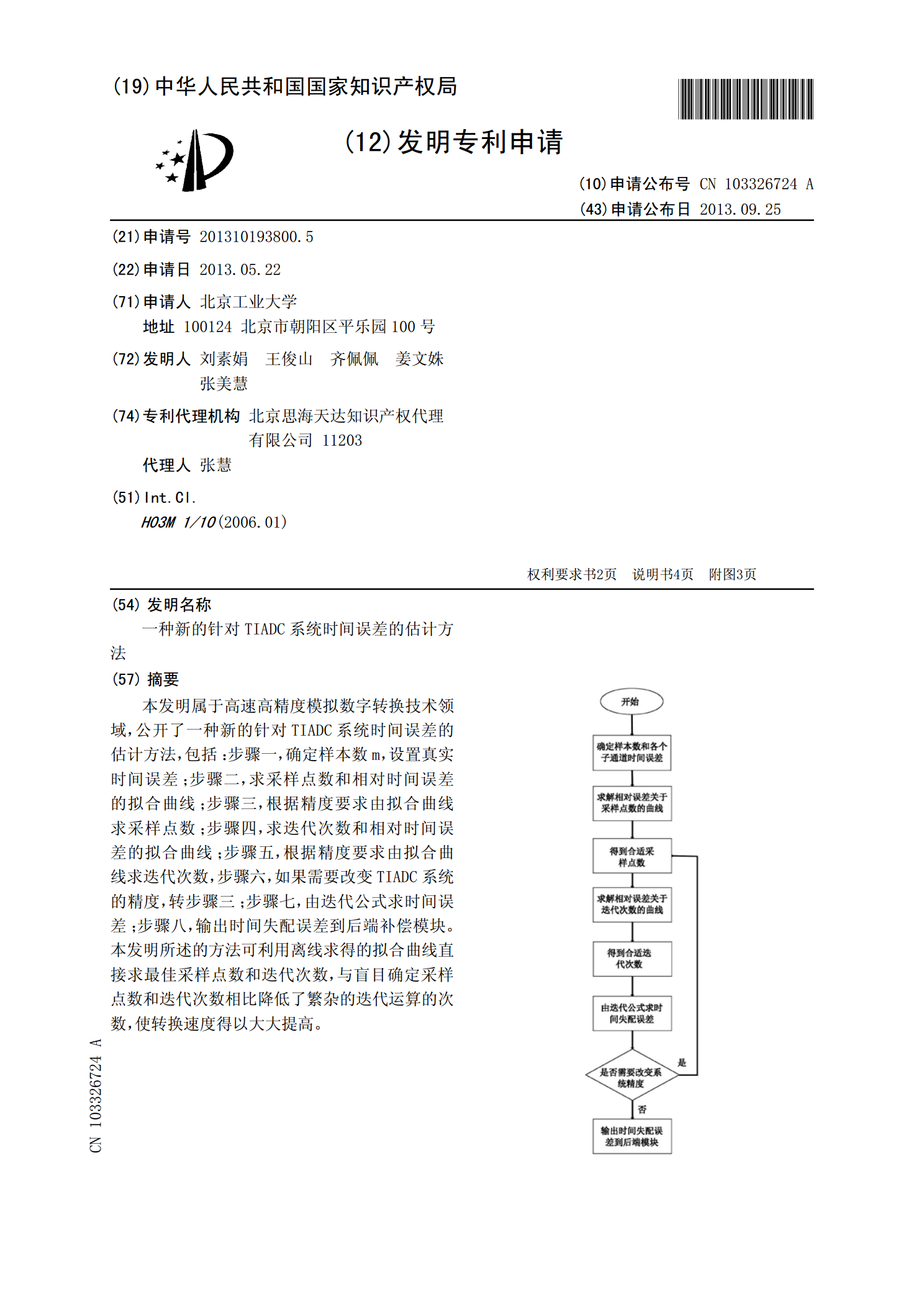

一种新的针对TIADC系统时间误差的估计方法.pdf

本发明属于高速高精度模拟数字转换技术领域,公开了一种新的针对TIADC系统时间误差的估计方法,包括:步骤一,确定样本数m,设置真实时间误差;步骤二,求采样点数和相对时间误差的拟合曲线;步骤三,根据精度要求由拟合曲线求采样点数;步骤四,求迭代次数和相对时间误差的拟合曲线;步骤五,根据精度要求由拟合曲线求迭代次数,步骤六,如果需要改变TIADC系统的精度,转步骤三;步骤七,由迭代公式求时间误差;步骤八,输出时间失配误差到后端补偿模块。本发明所述的方法可利用离线求得的拟合曲线直接求最佳采样点数和迭代次数,与盲目

一种TIADC时间失配快速盲校正方法.docx

一种TIADC时间失配快速盲校正方法一种TIADC时间失配快速盲校正方法摘要:时间间隔数字转换器(TIADC)是一种多通道高速数据采集系统,在很多领域中都被广泛应用。然而,由于系统硬件或其他原因,TIADC系统中各通道的时间失配问题成为影响系统性能的重要因素。本文提出了一种快速盲校正方法来解决时间失配问题。该方法使用自适应滤波技术,通过分析接收到的信号的时间差异,自动调整各通道的时间偏移,从而实现快速而准确的时间校正。1.引言时间间隔数字转换器(TIADC)是一种用于同时采集多通道高速数据的系统,具有广泛

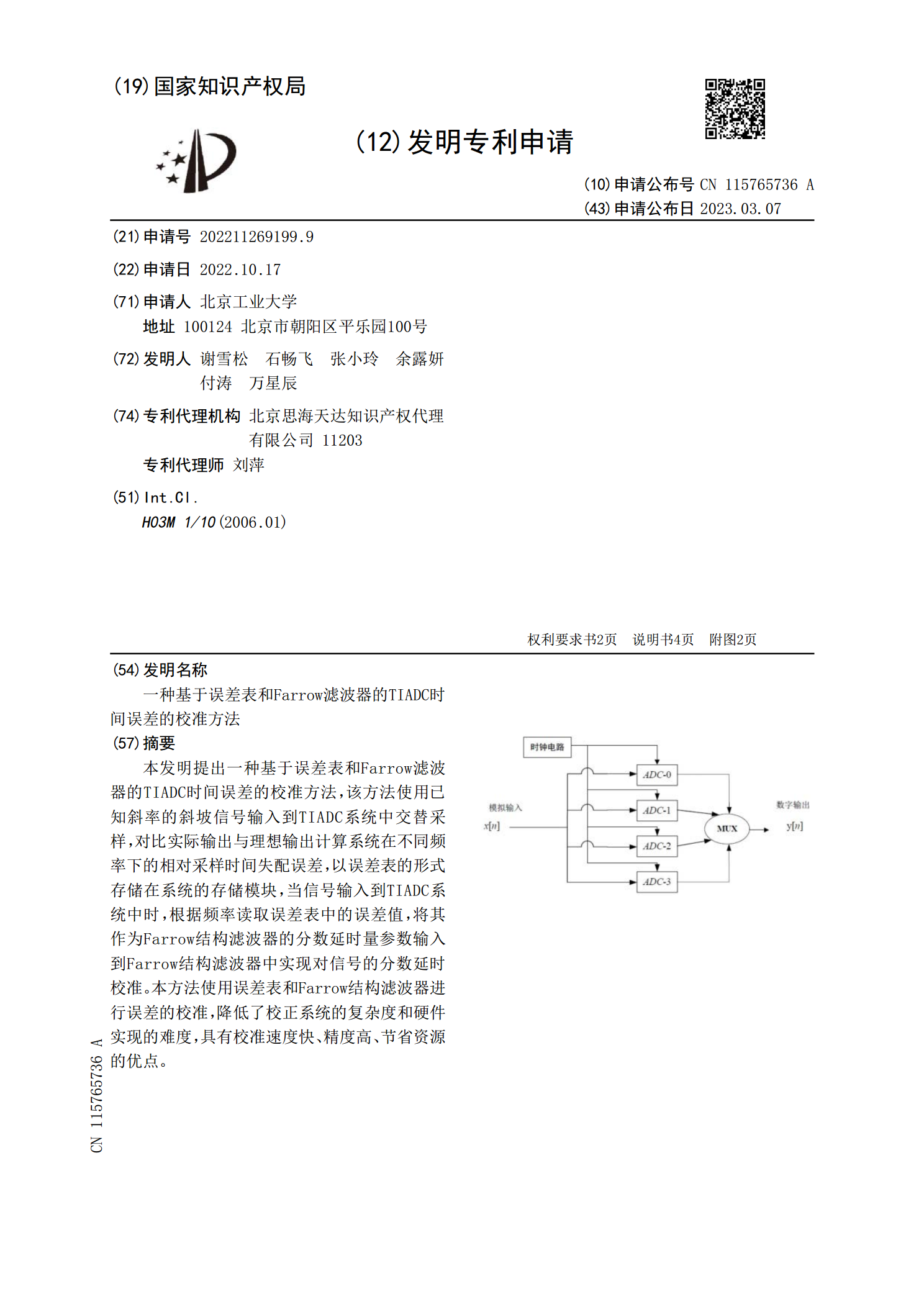

一种基于误差表和Farrow滤波器的TIADC时间误差的校准方法.pdf

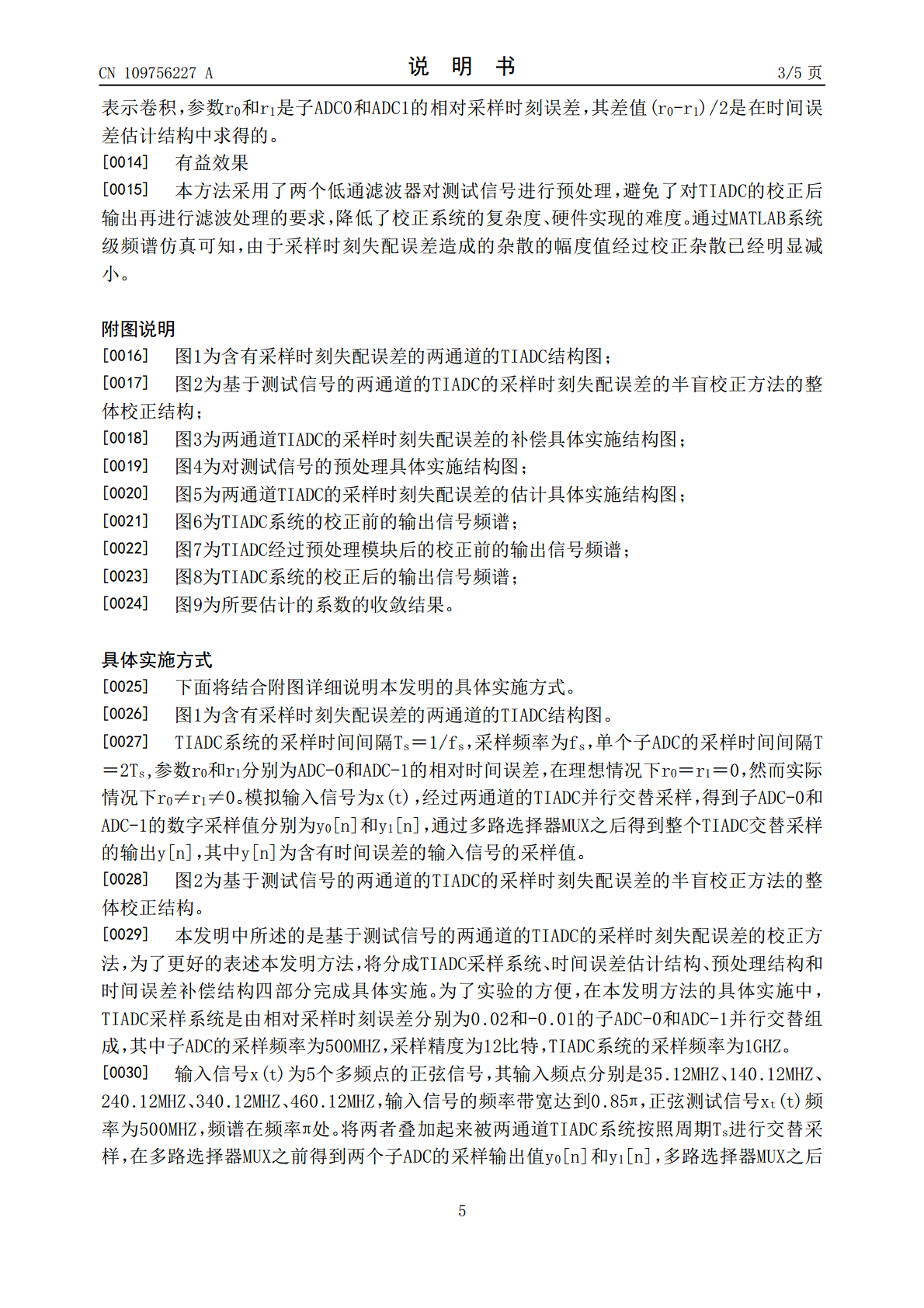

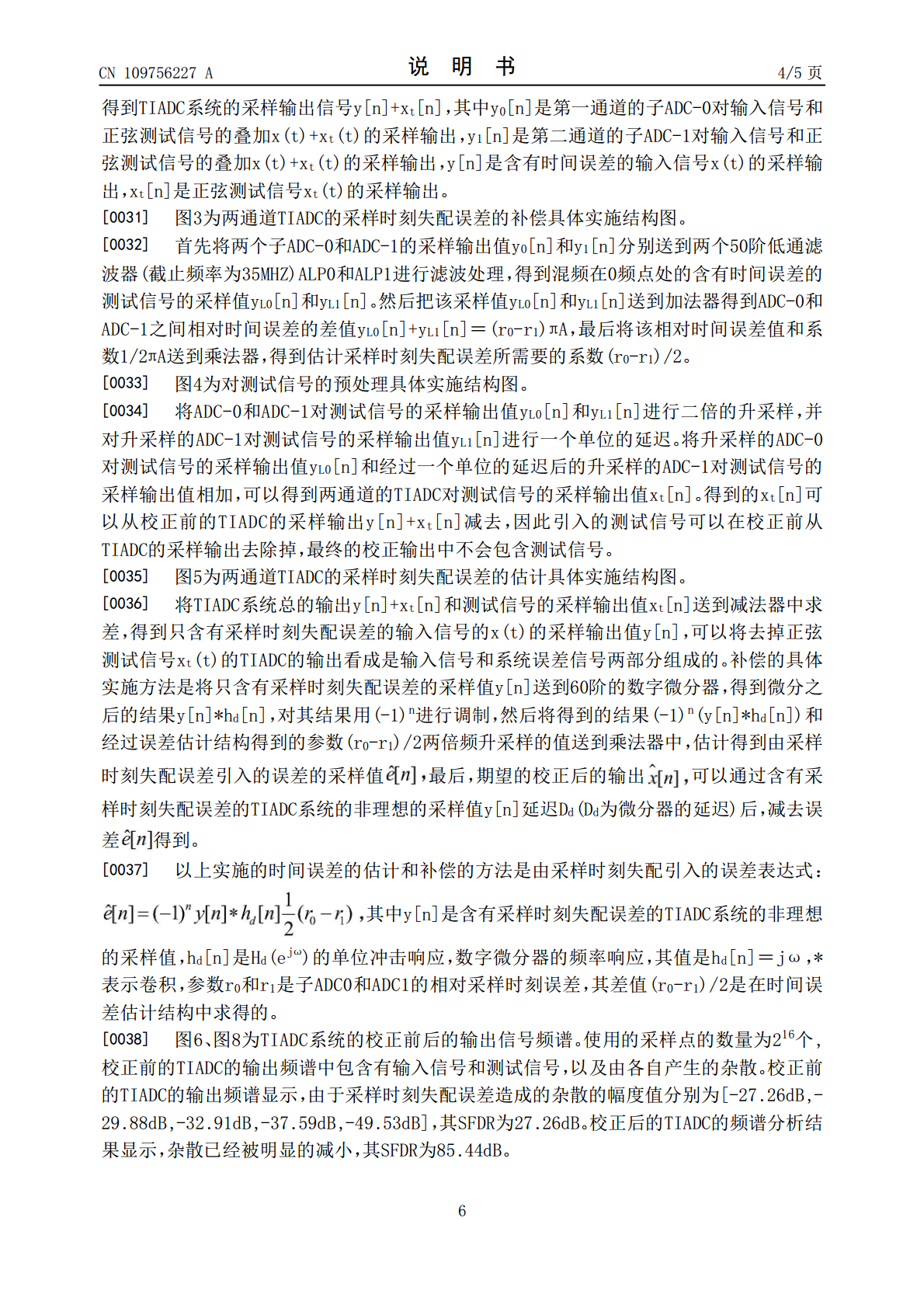

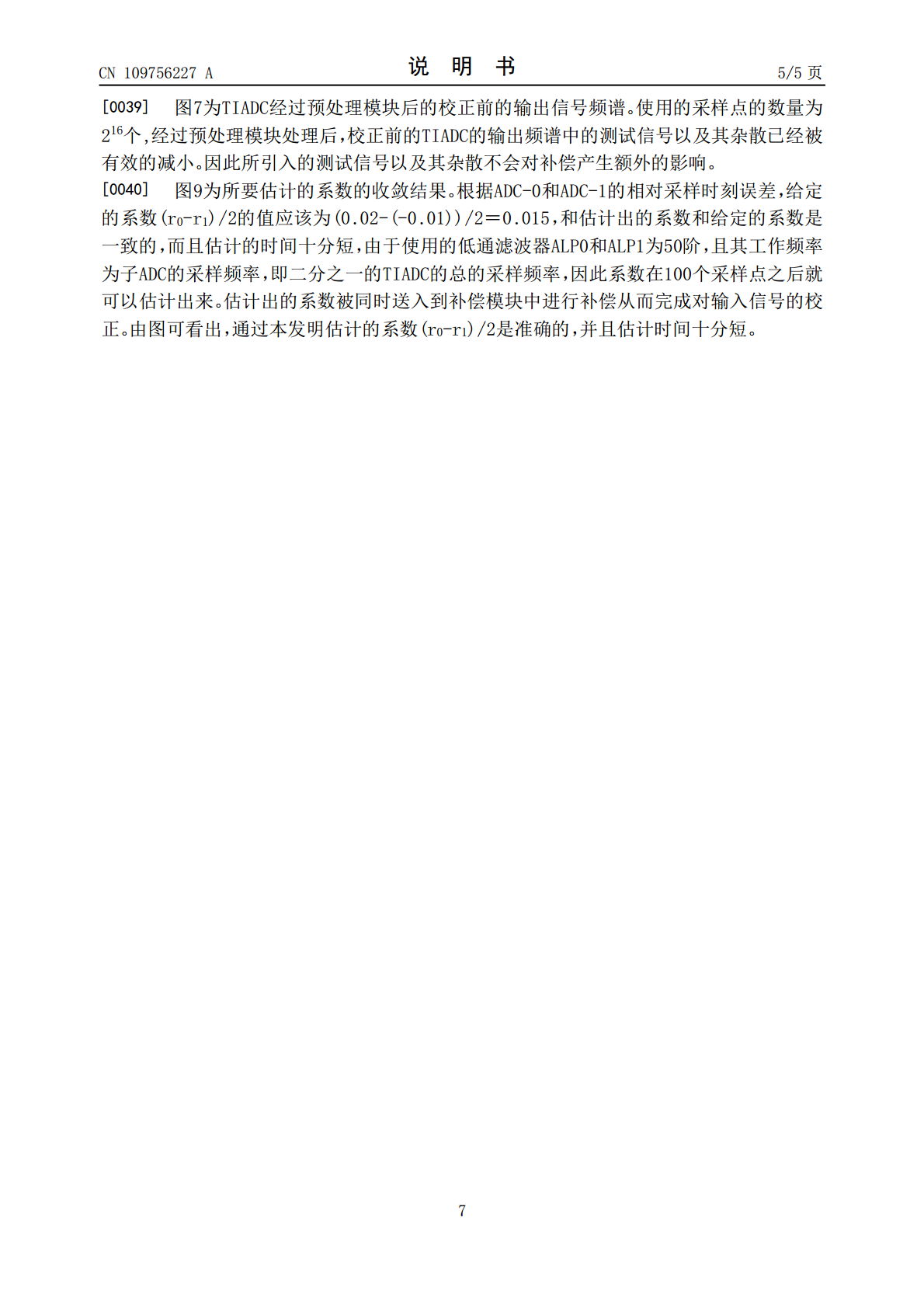

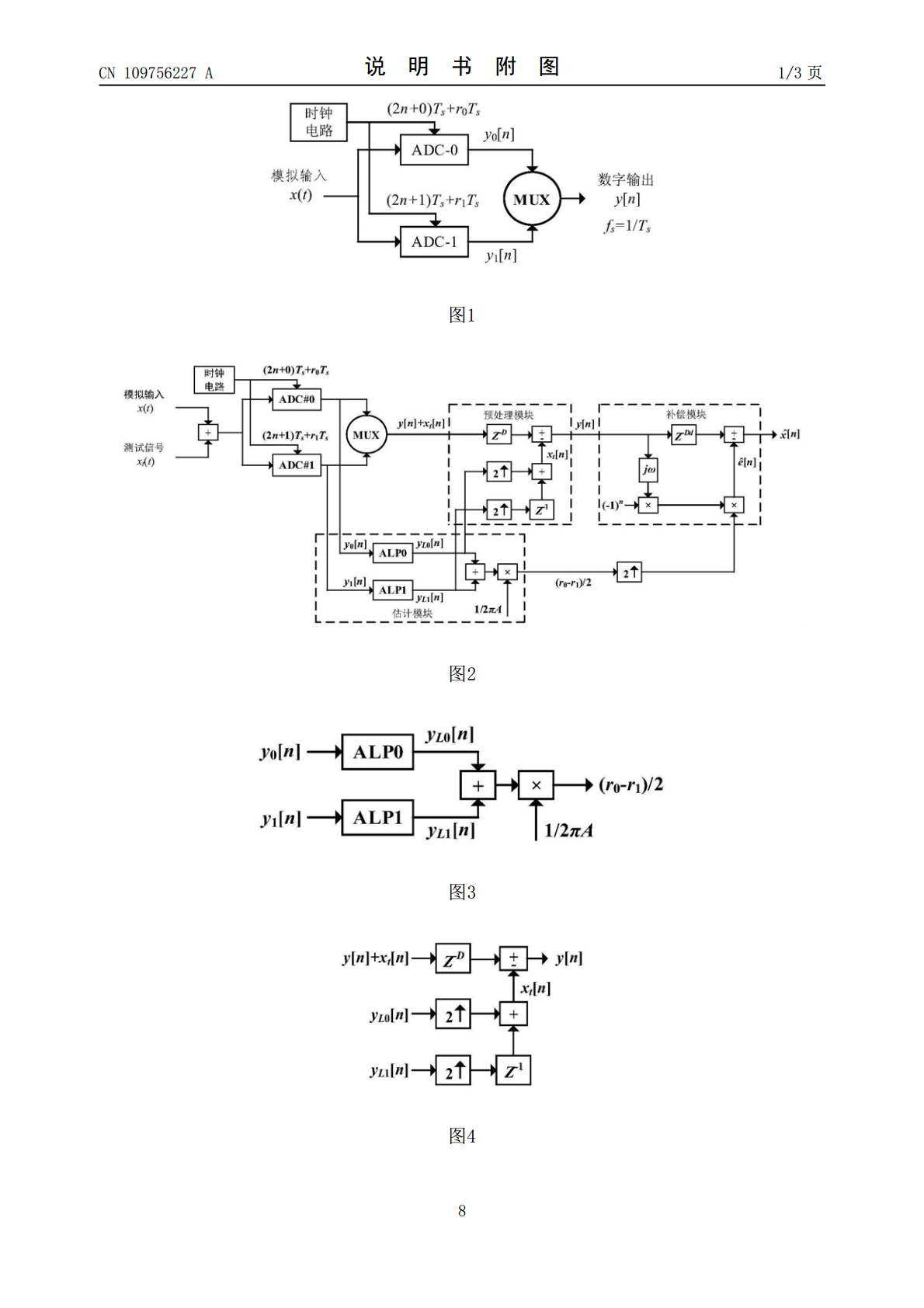

本发明提出一种基于误差表和Farrow滤波器的TIADC时间误差的校准方法,该方法使用已知斜率的斜坡信号输入到TIADC系统中交替采样,对比实际输出与理想输出计算系统在不同频率下的相对采样时间失配误差,以误差表的形式存储在系统的存储模块,当信号输入到TIADC系统中时,根据频率读取误差表中的误差值,将其作为Farrow结构滤波器的分数延时量参数输入到Farrow结构滤波器中实现对信号的分数延时校准。本方法使用误差表和Farrow结构滤波器进行误差的校准,降低了校正系统的复杂度和硬件实现的难度,具有校准速度