基于DSP和CPLD的高速数据采集系统设计.pdf

山柳****魔王

亲,该文档总共63页,到这已经超出免费预览范围,如果喜欢就直接下载吧~

相关资料

基于DSP和CPLD的高速数据采集系统设计.docx

基于DSP和CPLD的高速数据采集系统设计基于DSP和CPLD的高速数据采集系统设计摘要随着科技的不断进步,数据采集系统在各个领域的应用越来越广泛。本文提出了一种基于数字信号处理器(DSP)和可编程逻辑器件(CPLD)的高速数据采集系统设计。该系统具有高速数据采集、实时处理和灵活扩展等特点,在信号处理和数据采集领域具有重要的应用价值。关键词:DSP、CPLD、高速数据采集、信号处理、实时处理1.引言高速数据采集系统在科学研究、工业控制和医学诊断等领域有着广泛的应用。随着数字信号处理器(DSP)和可编程逻辑

基于DSP和CPLD的高速数据采集系统设计.pdf

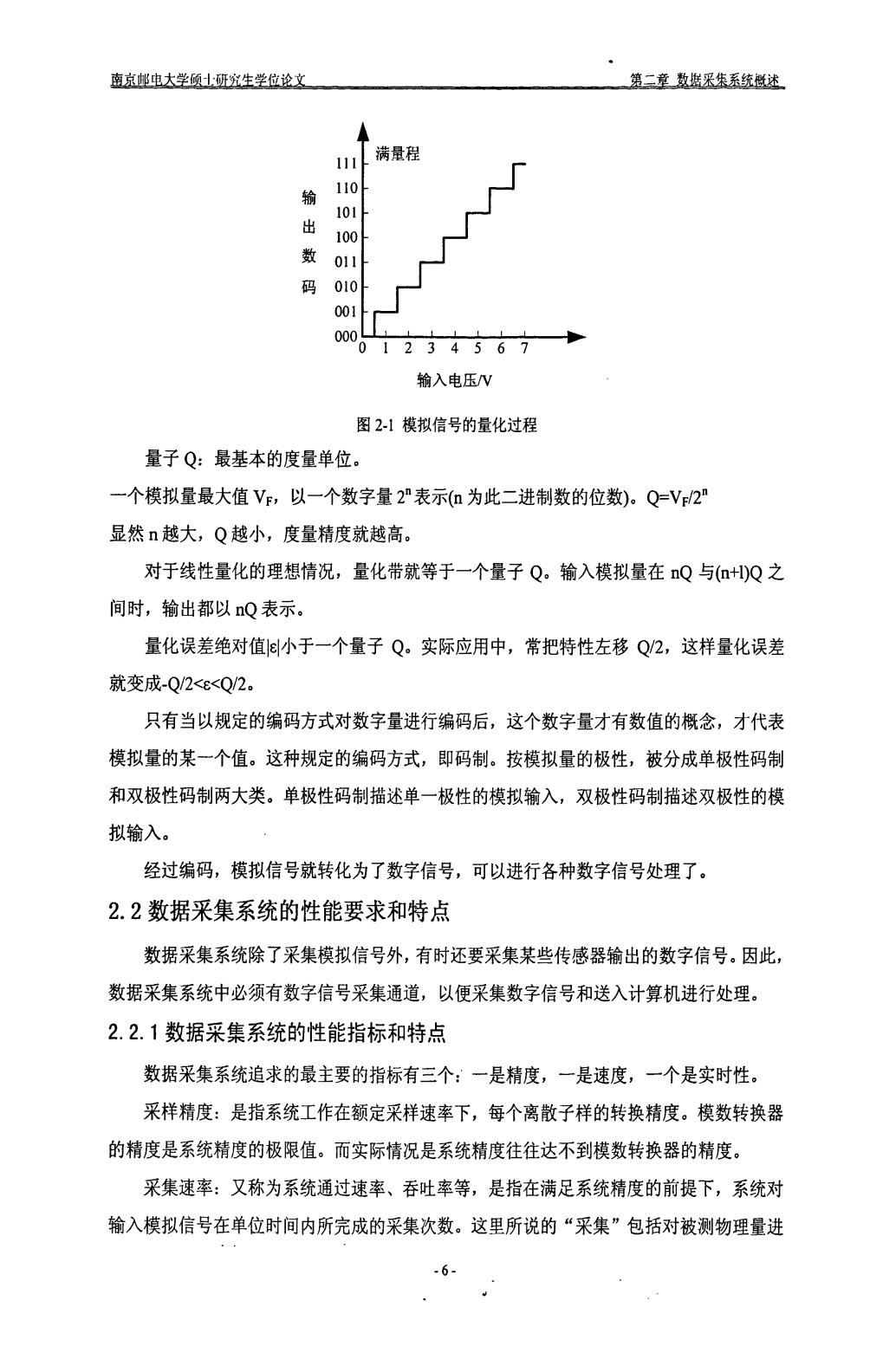

南京邮电大学硕士学位论文基于DSP和CPLD的高速数据采集系统设计姓名:储明聚申请学位级别:硕士专业:控制理论与控制工程指导教师:周西峰20100301摘要数据采集系统是信号与信息处理的重要组成部分随着工业化的不断发展数据采集系统需要采集的物理量越来越多对系统的速度和精度要求越来越高也不仅仅满足于对数据的采集还应当有对数据的处理。墓惴河τ梦@孟执中藕糯砑际醺

基于DSP和CPLD的高速数据采集系统设计.pdf

南京邮电大学硕士学位论文基于DSP和CPLD的高速数据采集系统设计姓名:储明聚申请学位级别:硕士专业:控制理论与控制工程指导教师:周西峰20100301摘要数据采集系统是信号与信息处理的重要组成部分随着工业化的不断发展数据采集系统需要采集的物理量越来越多对系统的速度和精度要求越来越高也不仅仅满足于对数据的采集还应当有对数据的处理。墓惴河τ梦@孟执中藕糯砑际醺

基于DSP与CPLD的多通道数据采集系统的设计.docx

基于DSP与CPLD的多通道数据采集系统的设计2009-05-27嵌入式在线用于实时控制系统的嵌入式系统经常需要对模拟量进行测量,通常的方法是以MCU为主产生采集控制时序控制模数转换器,并通过中断或查询的方式读取转换后的结果。由MCU产生采集控制时序将占用较多的系统软硬件资源。而在一般复杂的多路信号测控系统中,MCU需要进行数据存储,通讯,数据处理等多项工作,如果再需要其频繁地产生模数转换控制器的控制时序,将会影响系统的性能,严重时将会成为系统的瓶颈。本文采用CPLD产生A/D转换器的控制时序,使得CPL

基于FPGA和DSP的高速数据采集系统的设计.pdf

电子技术孙德玮等:基于FPGA和DSP的高速数据采集系统的设计基于FPGA和DSP的高速数据采集系统的设计孙德玮,李石亮(电子工程学院安徽合肥230001)摘要:数据采集与处理系统的设计是现代信号处理系统的基础,被广泛应用于雷达、通信、图像处理、遥感遥测等领域。在对WCDMA数字基带接收机的设计中,提出了一种基于FPGA和DSP的高速数据采集方案。该方案将A/D采样的数据送往FPGA,经过FPGA预处理后送到DSP,最终通过CPCI接口送到主控台。详细介绍了设计思想、具体的硬件连接以及FPGA设计的