VDMOS集成ESD结构的制备方法.pdf

霞英****娘子

亲,该文档总共14页,到这已经超出免费预览范围,如果喜欢就直接下载吧~

相关资料

VDMOS集成ESD结构的制备方法.pdf

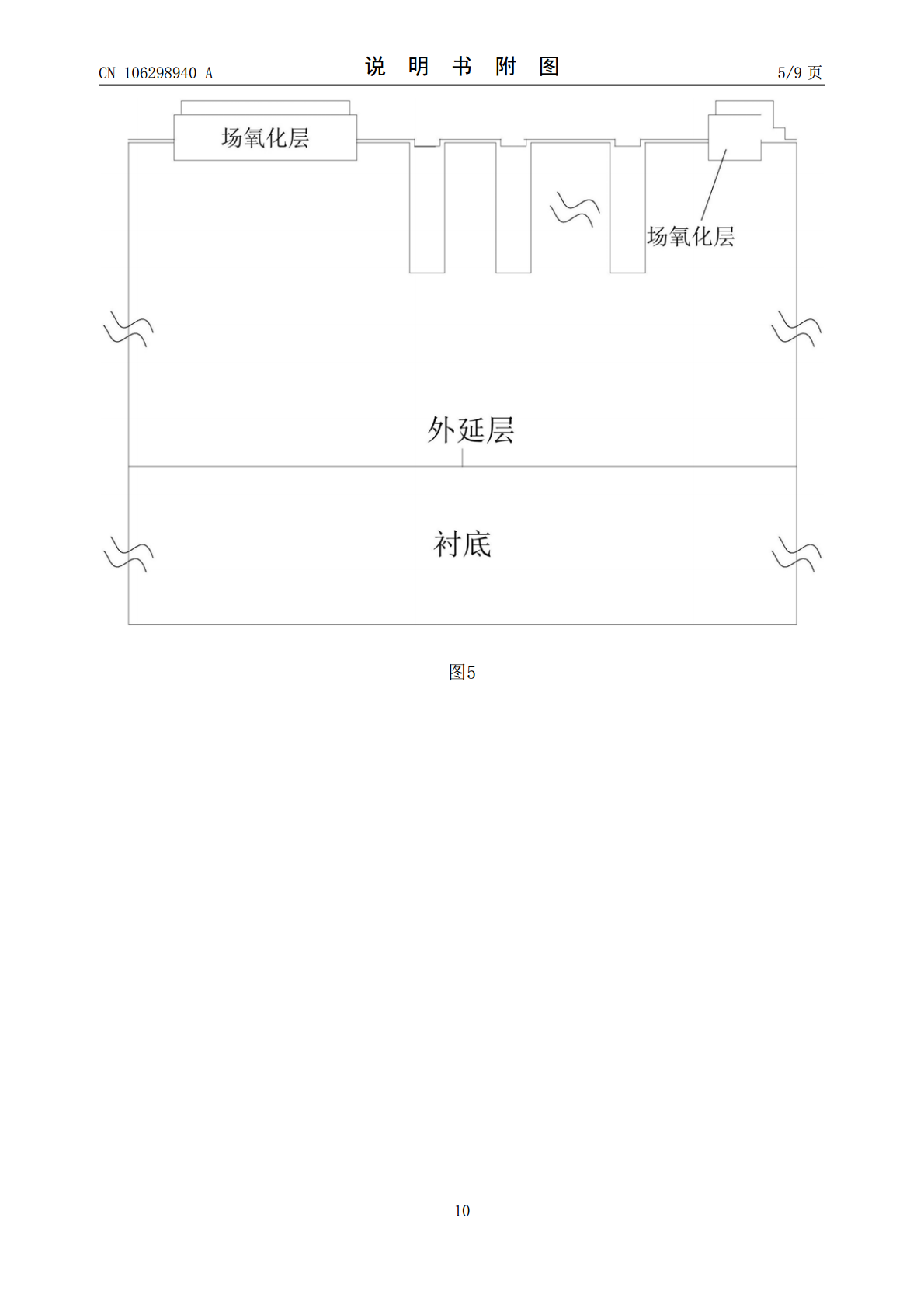

本发明公开了一种VDMOS集成ESD结构的制备方法,在衬底上形成外延层;在外延层表面淀积氮化硅层,之后通过光刻工艺和干法刻蚀工艺将栅极区域或者终端预定做ESD的区域刻蚀掉,部分区域露出外延层,剩余区域仍然有氮化硅覆盖;通过过炉管工艺在露出外延层的区域生长场氧化层;湿法腐蚀去掉氮化硅层,留下场氧化层图形;在有源区形成沟槽;形成MOSFET器件栅氧;淀积多晶硅;完成器件栅极以及ESDPN结的多晶硅图形;形成P阱;形成器件源极的同时,在ESD多晶硅图形上面完成PN结的结注入,形成ESD;介质淀积;形成引线孔;

集成ESD防护的Trench VDMOS器件及制造方法.pdf

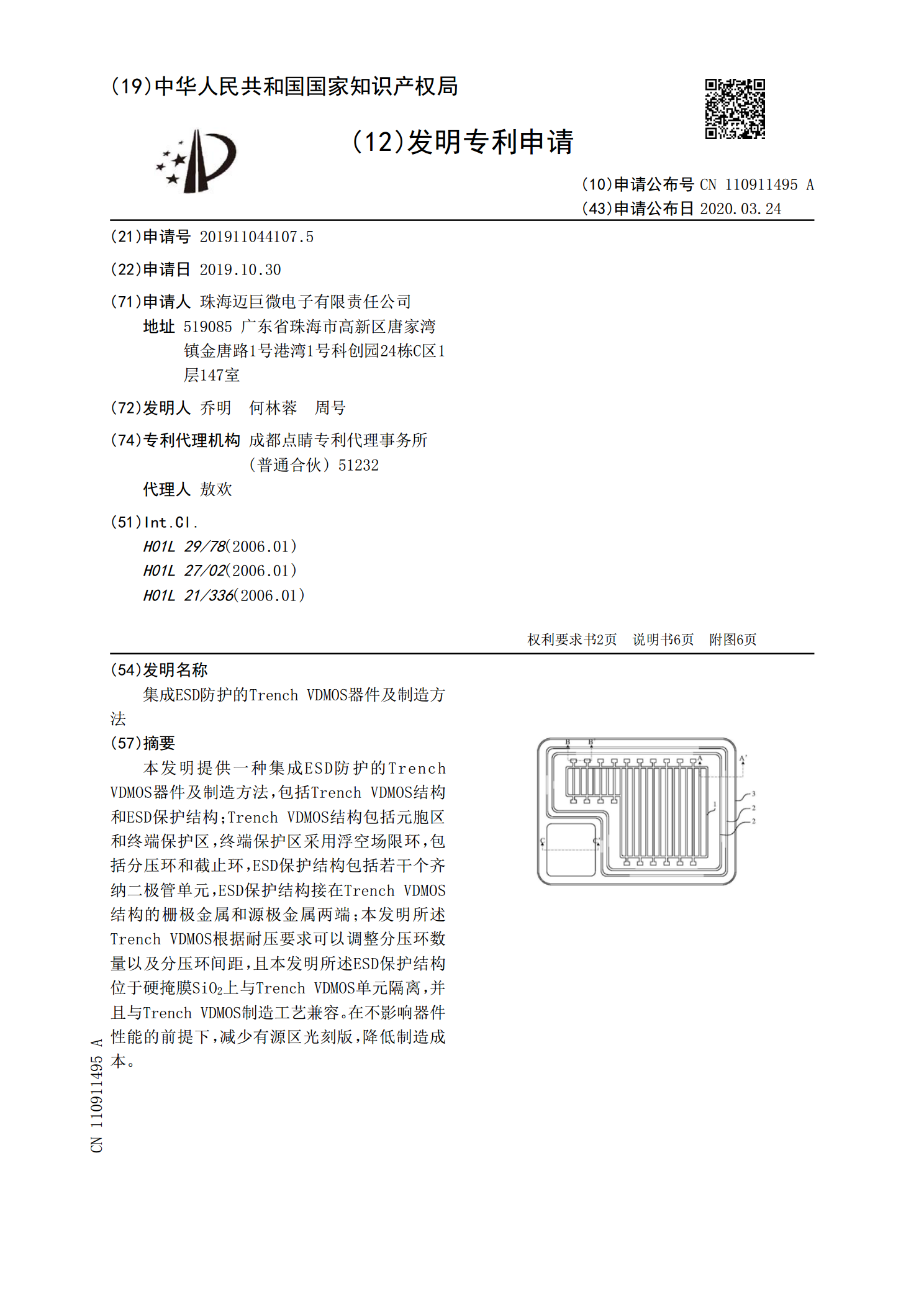

本发明提供一种集成ESD防护的TrenchVDMOS器件及制造方法,包括TrenchVDMOS结构和ESD保护结构;TrenchVDMOS结构包括元胞区和终端保护区,终端保护区采用浮空场限环,包括分压环和截止环,ESD保护结构包括若干个齐纳二极管单元,ESD保护结构接在TrenchVDMOS结构的栅极金属和源极金属两端;本发明所述TrenchVDMOS根据耐压要求可以调整分压环数量以及分压环间距,且本发明所述ESD保护结构位于硬掩膜SiO

集成ESD防护的Trench VDMOS器件及制造方法.pdf

本发明提供一种集成ESD防护的TrenchVDMOS器件及制造方法,包括TrenchVDMOS结构和ESD保护结构;TrenchVDMOS结构包括元胞区和终端保护区,所述终端保护区采用沟槽结构,包括一个截止环和至少一个分压环,ESD保护结构包括若干个齐纳二极管单元,所述ESD保护结构接在栅极金属和源极金属两端,本发明所述TrenchVDMOS通过减小元胞节距、增加源极金属与第一导电类型源极接触的接触面积,减小TrenchVDMOS比导通电阻,且本发明ESD保护结构位于硬掩膜SiO

VDMOS器件ESD保护结构及其制作工艺.pdf

本发明涉及半导体制作技术领域,具体涉及一种VDMOS器件ESD保护结构及其制作工艺。其中制作工艺包括提供第一导电类型外延片,在所述第一导电类型外延片上制作多晶硅;在所述多晶硅上涂覆光刻胶;在所述多晶硅的边缘,靠近其他有源区位置处,形成ESD保护区;进行光刻工艺,保留所述ESD保护区位置处的光刻胶;轻掺杂注入第一导电类型离子;去除所述光刻胶;刻蚀所述多晶硅,形成栅极结构;重掺杂注入第一导电类型离子,在所述ESD保护区位置处形成多个相间隔的阴极区域;重掺杂第二导电类型离子,在所述ESD保护区位置处形成多个相间

低压MOSFET集成ESD保护结构的设计方法.docx

低压MOSFET集成ESD保护结构的设计方法摘要本文介绍了低压MOSFET集成ESD保护结构的设计方法。详细介绍ESD保护结构的作用、设计要求、电路结构和参数选择等内容,并结合实际案例分析了ESD保护结构的设计流程和方法。最后,探讨了低压MOSFET集成ESD保护结构的未来发展方向和应用前景。1.引言随着半导体工艺的不断发展和应用广泛,芯片的ESD(静电放电)问题已经成为芯片设计中不可忽略的问题。在芯片设计中必须加入ESD保护结构,以防止芯片在运行过程中因静电放电而受到破坏。因此,ESD保护结构的设计也成