浅沟槽隔离结构的制造方法.pdf

玄静****写意

在线预览结束,喜欢就下载吧,查找使用更方便

相关资料

浅沟槽隔离结构的制造方法.pdf

本发明公开了一种浅沟槽隔离结构的制造方法,包括步骤:步骤一、在半导体衬底上形成浅沟槽;步骤二、涂布聚氮硅烷层;步骤三、进行氧氮置换工艺将聚氮硅烷层转换为二氧化硅层并形成浅沟槽隔离结构;氧氮置换工艺包括两次以上的炉管水汽工艺,两次炉管水汽工艺之间包括一次热退火工艺和一次减薄工艺。本发明能采用PSZ实现对浅沟槽的良好填充,并能提高对PSZ的氧氮置换效果以及提高转换后的二氧化硅的致密性从而能提高二氧化硅的膜质,同时能减少有源区的热过程。

浅沟槽隔离结构的制备方法及浅沟槽隔离结构.pdf

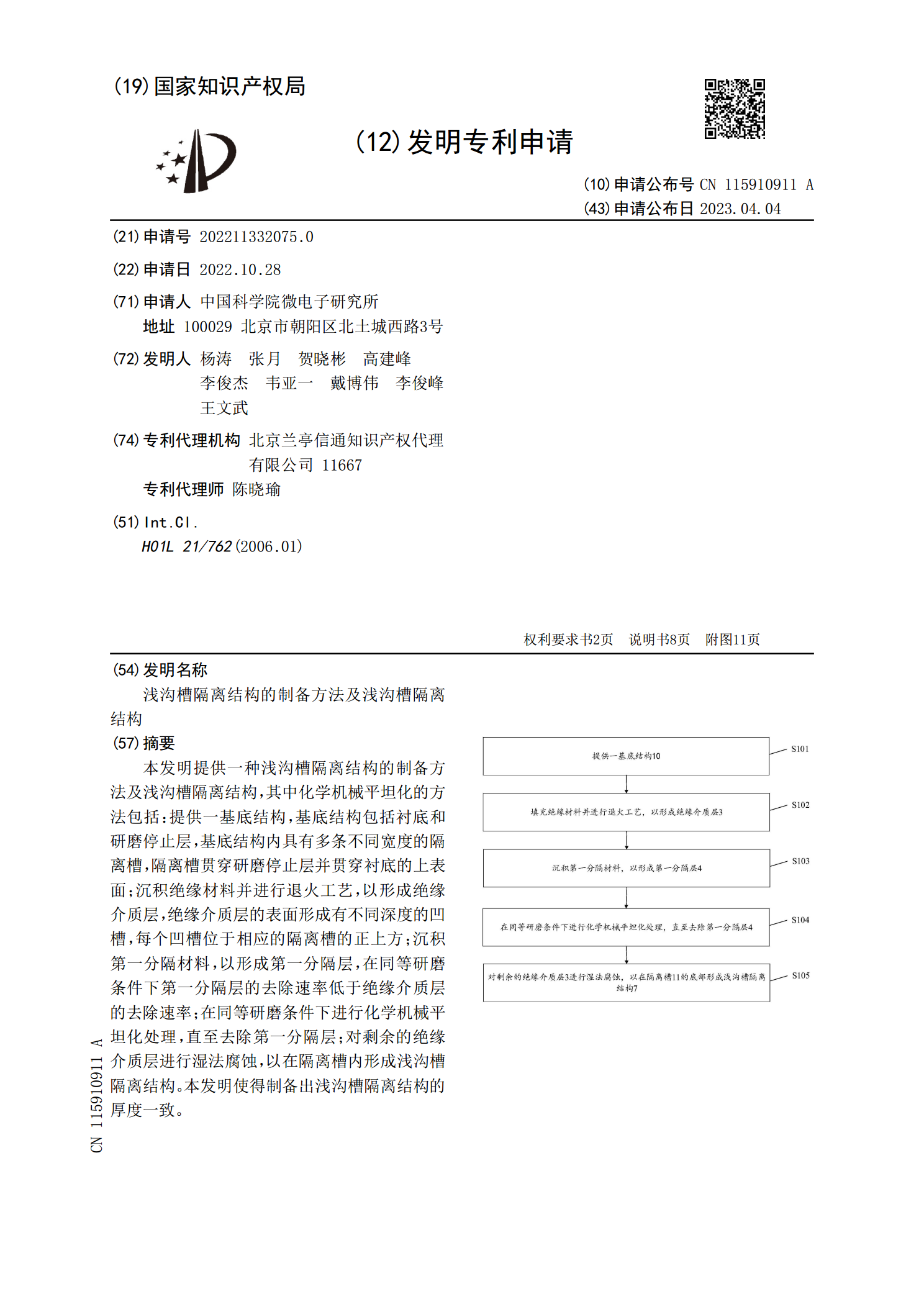

本发明提供一种浅沟槽隔离结构的制备方法及浅沟槽隔离结构,其中化学机械平坦化的方法包括:提供一基底结构,基底结构包括衬底和研磨停止层,基底结构内具有多条不同宽度的隔离槽,隔离槽贯穿研磨停止层并贯穿衬底的上表面;沉积绝缘材料并进行退火工艺,以形成绝缘介质层,绝缘介质层的表面形成有不同深度的凹槽,每个凹槽位于相应的隔离槽的正上方;沉积第一分隔材料,以形成第一分隔层,在同等研磨条件下第一分隔层的去除速率低于绝缘介质层的去除速率;在同等研磨条件下进行化学机械平坦化处理,直至去除第一分隔层;对剩余的绝缘介质层进行湿法

浅沟槽隔离结构的制备方法及浅沟槽隔离结构.pdf

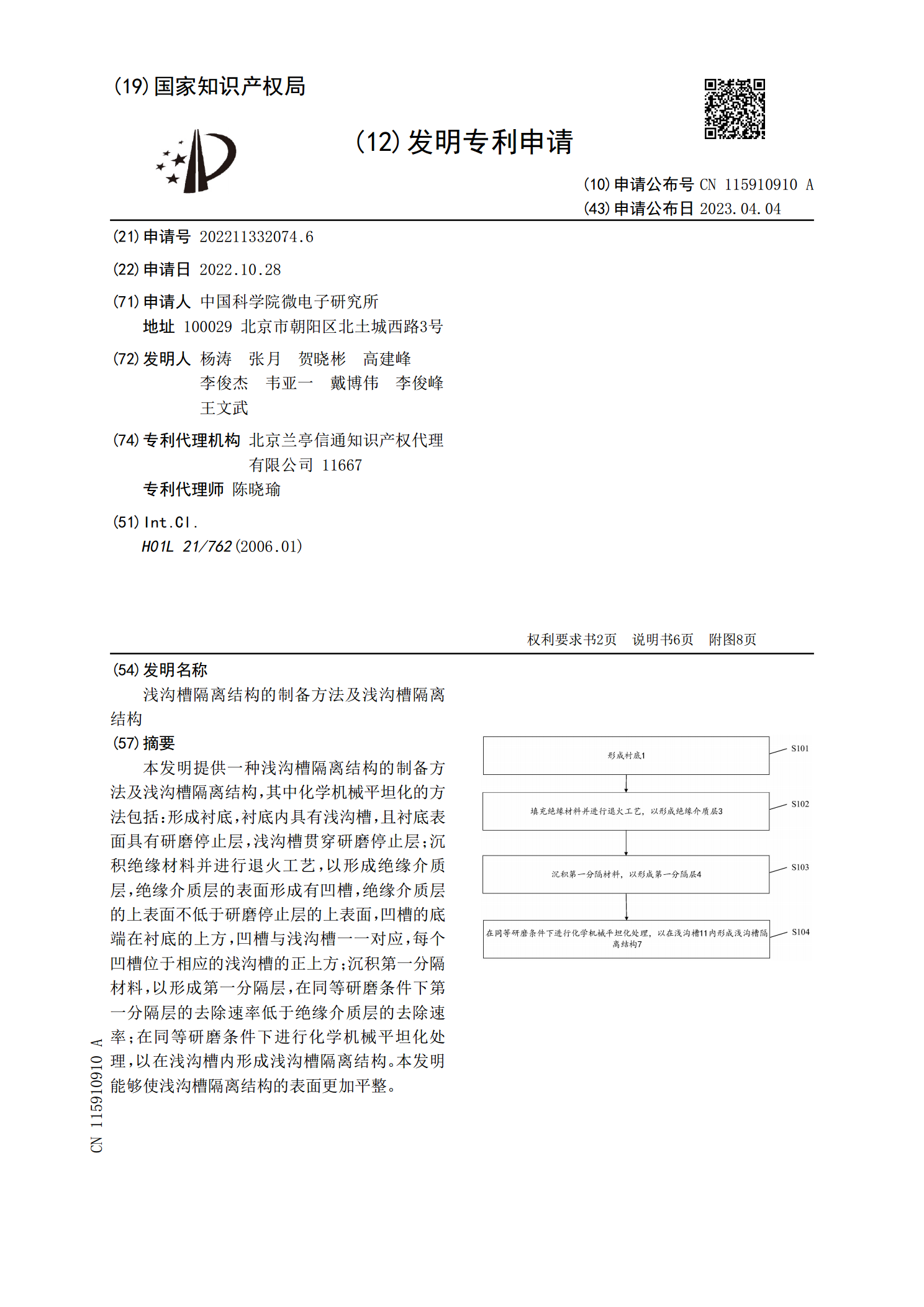

本发明提供一种浅沟槽隔离结构的制备方法及浅沟槽隔离结构,其中化学机械平坦化的方法包括:形成衬底,衬底内具有浅沟槽,且衬底表面具有研磨停止层,浅沟槽贯穿研磨停止层;沉积绝缘材料并进行退火工艺,以形成绝缘介质层,绝缘介质层的表面形成有凹槽,绝缘介质层的上表面不低于研磨停止层的上表面,凹槽的底端在衬底的上方,凹槽与浅沟槽一一对应,每个凹槽位于相应的浅沟槽的正上方;沉积第一分隔材料,以形成第一分隔层,在同等研磨条件下第一分隔层的去除速率低于绝缘介质层的去除速率;在同等研磨条件下进行化学机械平坦化处理,以在浅沟槽内

浅沟槽隔离结构的形成方法及浅沟槽隔离结构.pdf

本发明提供了一种浅沟槽隔离结构的形成方法及浅沟槽隔离结构。所述浅沟槽隔离结构的形成方法,包括如下步骤:形成衬底,所述衬底内具有浅沟槽、且所述衬底表面具有研磨停止层;沉积绝缘材料,形成绝缘介质层,所述绝缘介质层填充于所述浅沟槽内、并覆盖于所述研磨停止层与所述衬底表面;平坦化所述绝缘介质层至预设厚度;研磨具有所述预设厚度的所述绝缘介质层,去除位于所述研磨停止层表面的所述绝缘介质层,且在研磨过程中所述绝缘介质层的研磨速率大于所述研磨停止层的研磨速率;去除所述研磨停止层,形成浅沟槽隔离结构。本发明避免了所述研磨停

浅沟槽隔离的制造方法.pdf

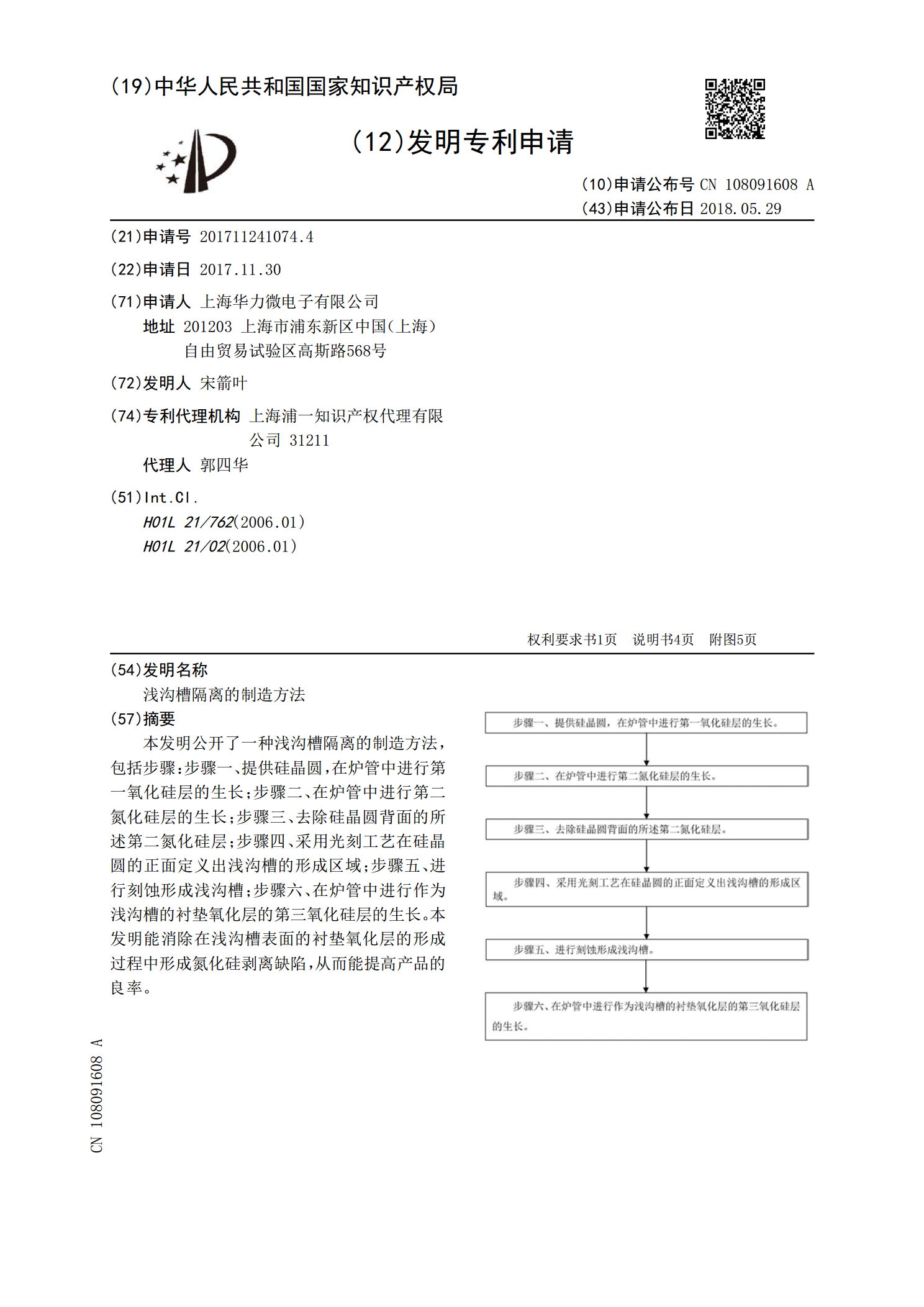

本发明公开了一种浅沟槽隔离的制造方法,包括步骤:步骤一、提供硅晶圆,在炉管中进行第一氧化硅层的生长;步骤二、在炉管中进行第二氮化硅层的生长;步骤三、去除硅晶圆背面的所述第二氮化硅层;步骤四、采用光刻工艺在硅晶圆的正面定义出浅沟槽的形成区域;步骤五、进行刻蚀形成浅沟槽;步骤六、在炉管中进行作为浅沟槽的衬垫氧化层的第三氧化硅层的生长。本发明能消除在浅沟槽表面的衬垫氧化层的形成过程中形成氮化硅剥离缺陷,从而能提高产品的良率。