原子层沉积法形成氮化物膜的方法.pdf

睿达****的的

亲,该文档总共12页,到这已经超出免费预览范围,如果喜欢就直接下载吧~

相关资料

原子层沉积法形成氮化物膜的方法.pdf

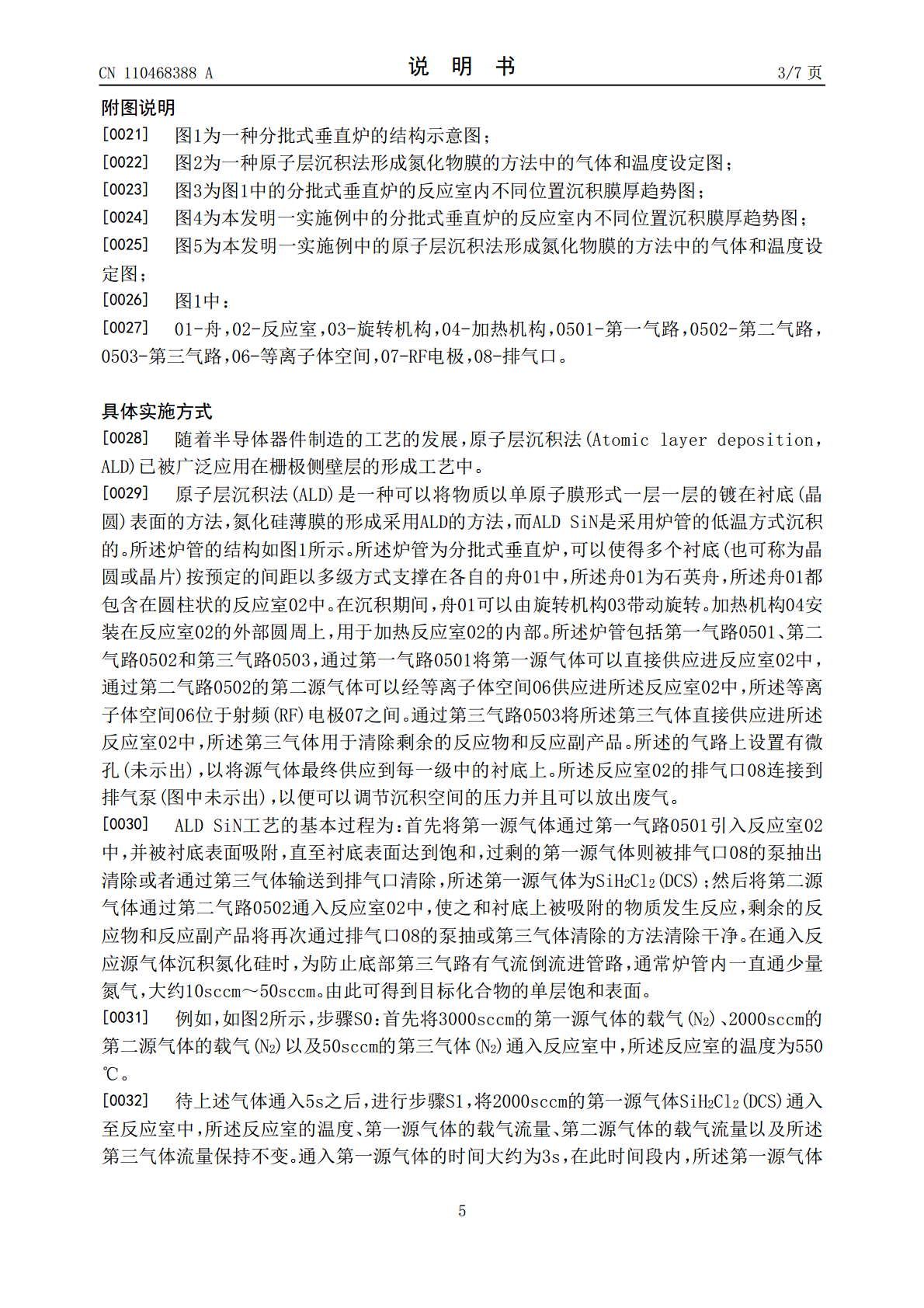

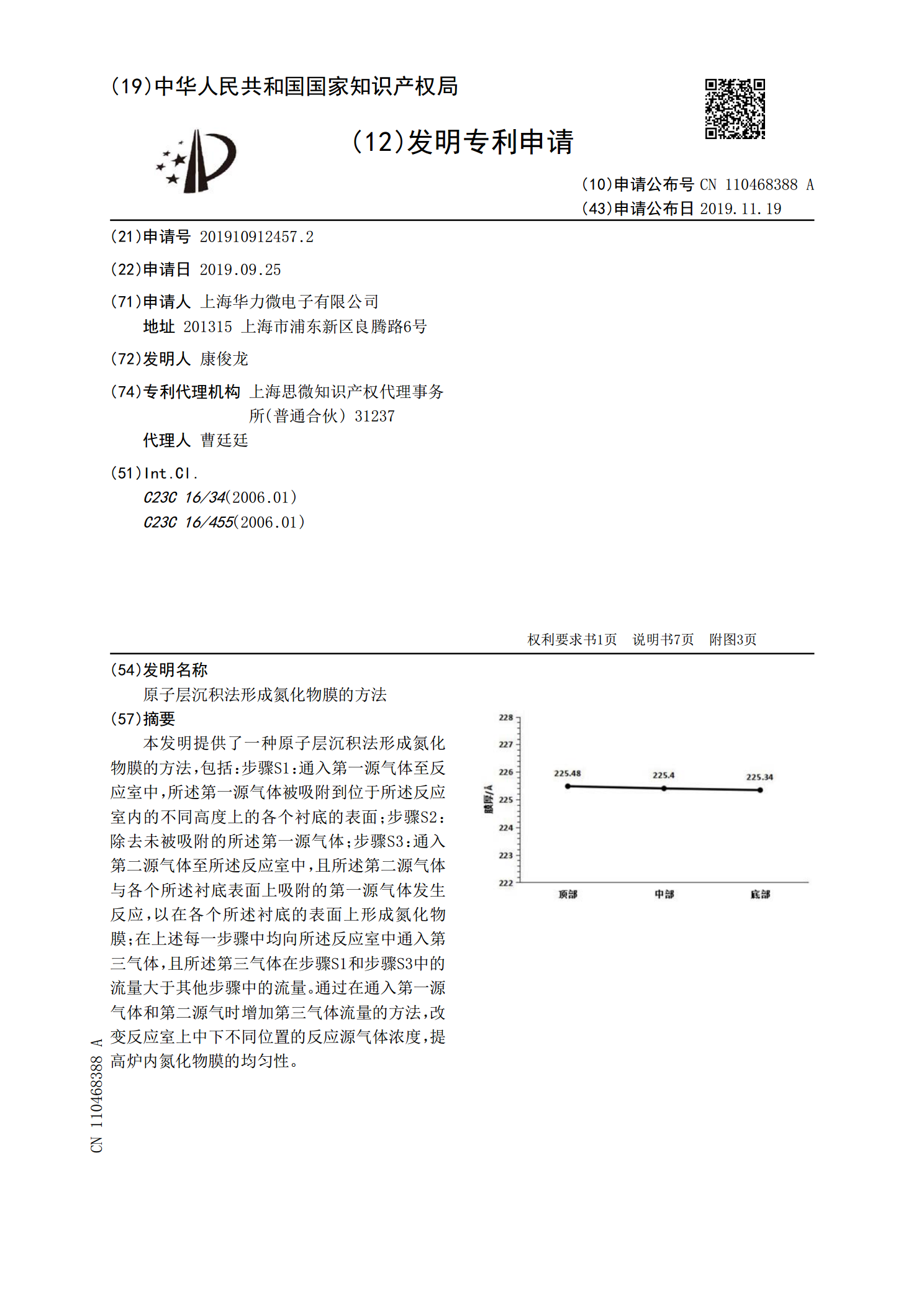

本发明提供了一种原子层沉积法形成氮化物膜的方法,包括:步骤S1:通入第一源气体至反应室中,所述第一源气体被吸附到位于所述反应室内的不同高度上的各个衬底的表面;步骤S2:除去未被吸附的所述第一源气体;步骤S3:通入第二源气体至所述反应室中,且所述第二源气体与各个所述衬底表面上吸附的第一源气体发生反应,以在各个所述衬底的表面上形成氮化物膜;在上述每一步骤中均向所述反应室中通入第三气体,且所述第三气体在步骤S1和步骤S3中的流量大于其他步骤中的流量。通过在通入第一源气体和第二源气时增加第三气体流量的方法,改变反

膜层沉积装置及膜层沉积方法.pdf

本发明涉及半导体制造技术领域,尤其涉及一种膜层沉积装置及膜层沉积方法。所述膜层沉积装置包括:承载部,用于承载晶圆;喷头,设置于所述承载部上方,用于向所述位于所述承载部的表面的所述晶圆喷射反应气体,所述反应气体用于在所述晶圆表面形成膜层;遮蔽结构,用于遮蔽所述喷头的边缘区域,以降低所述晶圆的边缘区域的所述反应气体浓度。本发明一方面,提高了膜层厚度的均匀性;另一方面,使得在后续刻蚀过程中,边缘区域的膜层能够充分被刻蚀,避免了膜层残留,改善了刻蚀质量。

原子层沉积装置及方法.pdf

本申请公开了一种原子层沉积装置及方法,原子层沉积装置采用了额外添加吹扫管路的设计,通过将吹扫管路并联在原有的前驱体传输管路中,从而将吹扫气体的流量从前驱体的设定流量中解放出来,可以显著加大吹扫气体的流量,由于吹扫气流的增强,其吹扫工序所消耗的时间可以进一步减小,从而间接提高了整个装置的生产效率,同时还可以更彻底的对反应腔室中喷淋头及喷淋头边缘焊接处进行吹扫,避免了前驱体的残留,提高了生产薄膜的均匀性及薄膜质量。

原子层沉积对膜材料改性的研究进展.docx

原子层沉积对膜材料改性的研究进展原子层沉积(AtomicLayerDeposition,ALD)是一种将物质以原子层的方式沉积在基底表面的薄膜制备技术。由于其在薄膜厚度控制、复杂结构制备和均匀性方面具有独特的优势,ALD技术在膜材料改性方面得到了广泛的研究和应用。本文将对ALD在膜材料改性方面的研究进展进行综述。首先,ALD技术可以用于制备具有特定功能的薄膜。例如,ALD可以在基底表面沉积功能性氧化物薄膜,如二氧化硅(SiO2)膜、氧化铝(Al2O3)膜等。这些薄膜可以用于保护基底、改善界面特性,或者作为

原子层沉积法的原理和应用.ppt

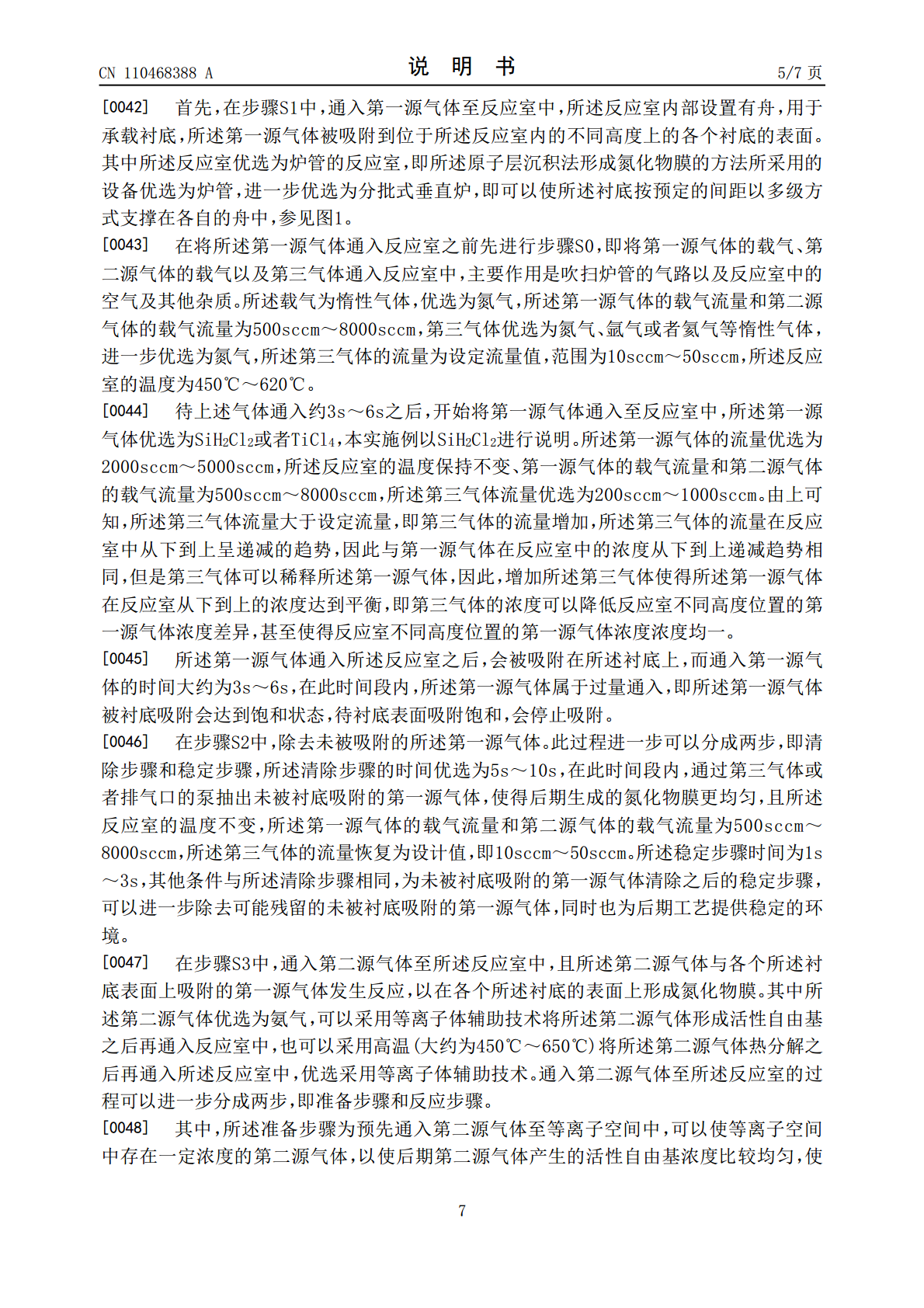

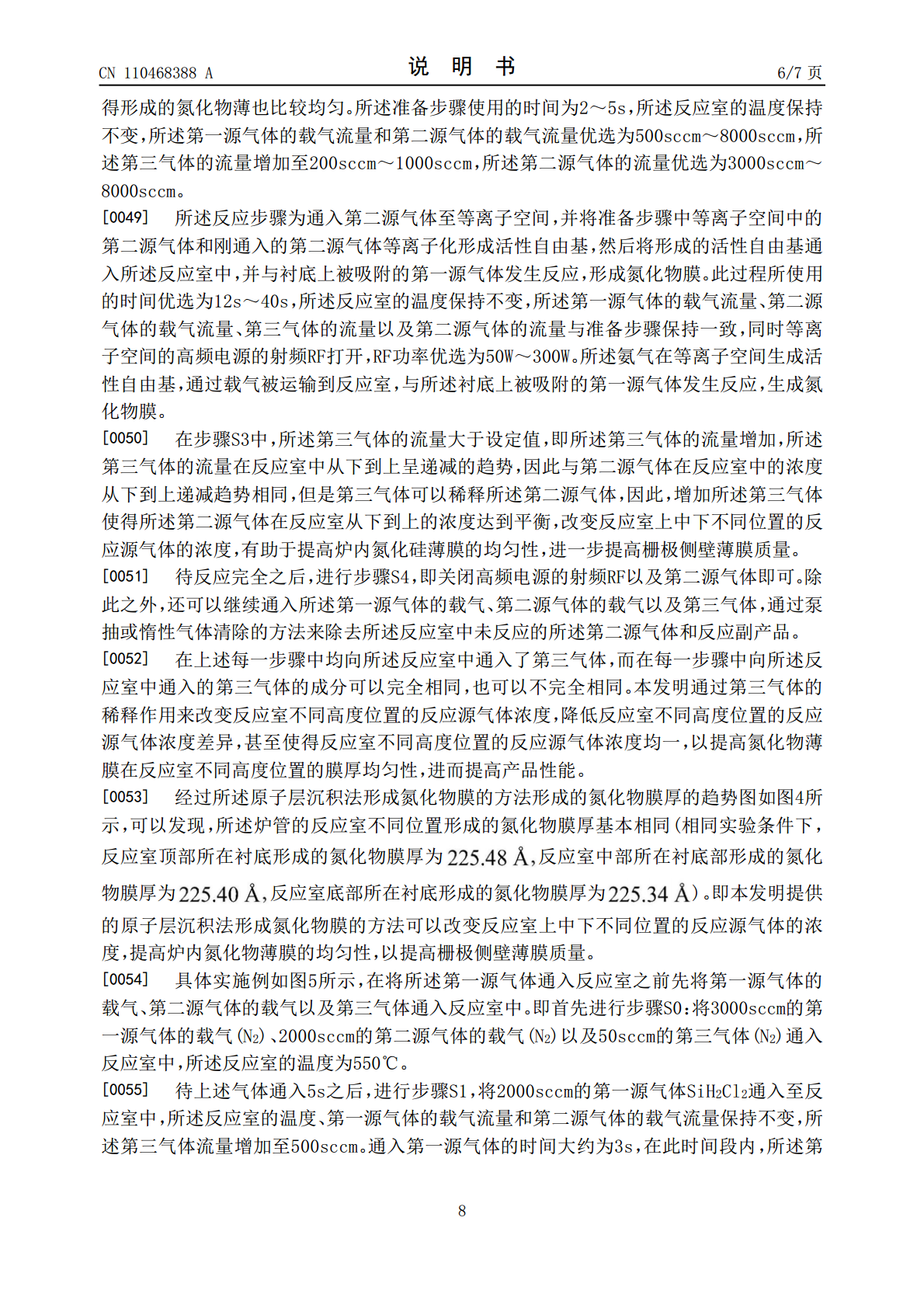

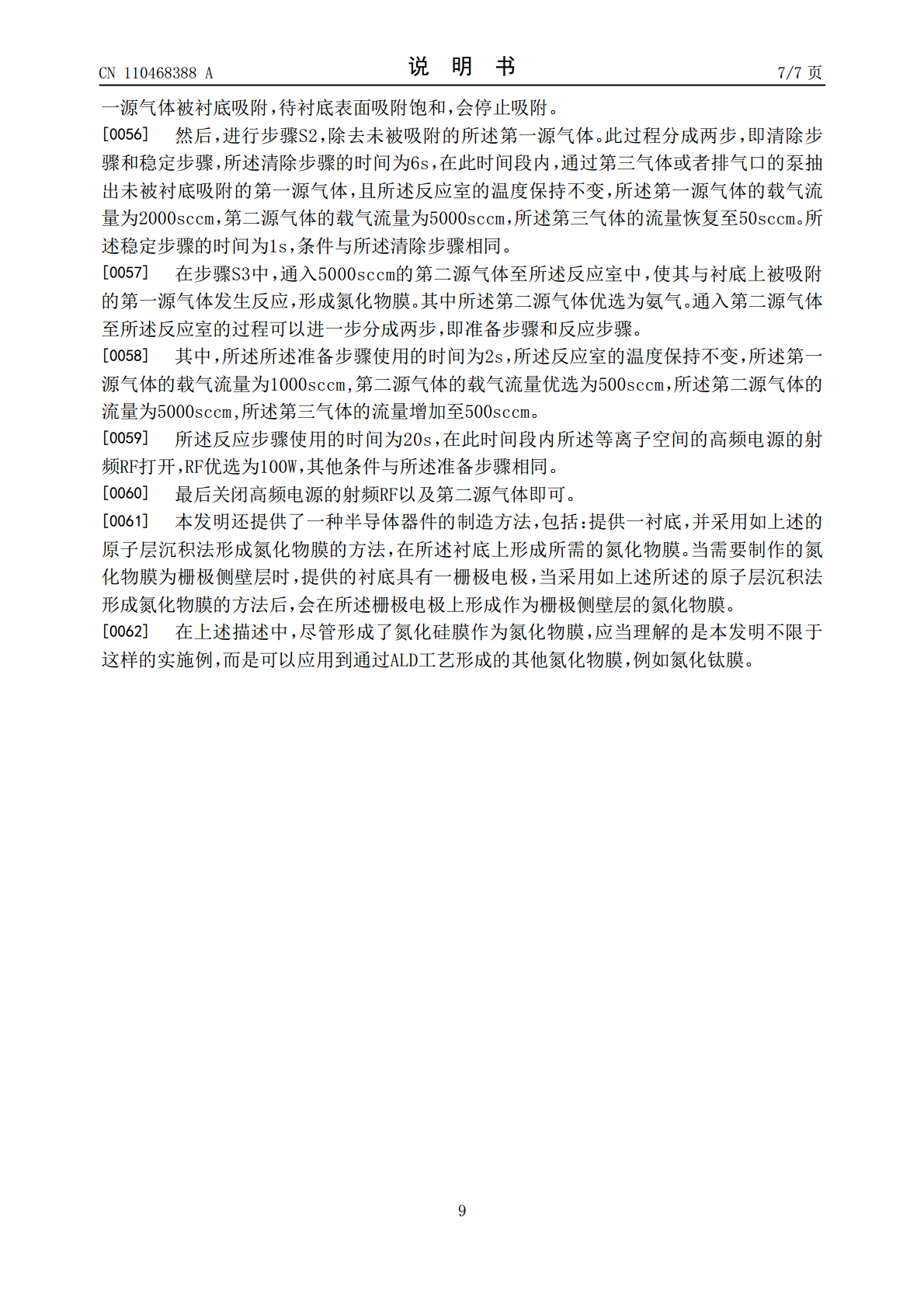

2.Classicalmodels:ALDofAl2O33.ComparisonofALDandCVD3.ComparisonofALDandCVD14.2Coatingsonnanoparticles4.2Coatingsonnanoparticles4.3CombinationofCNTandsuper-blackcoatingsSchematicillustrationoftheALDandCVDprocessforthesynthesisofCNTarraysStevenM.George,Chem