一种射频接收电路和射频接收机.pdf

曦晨****22

在线预览结束,喜欢就下载吧,查找使用更方便

相关资料

一种射频接收电路和射频接收机.pdf

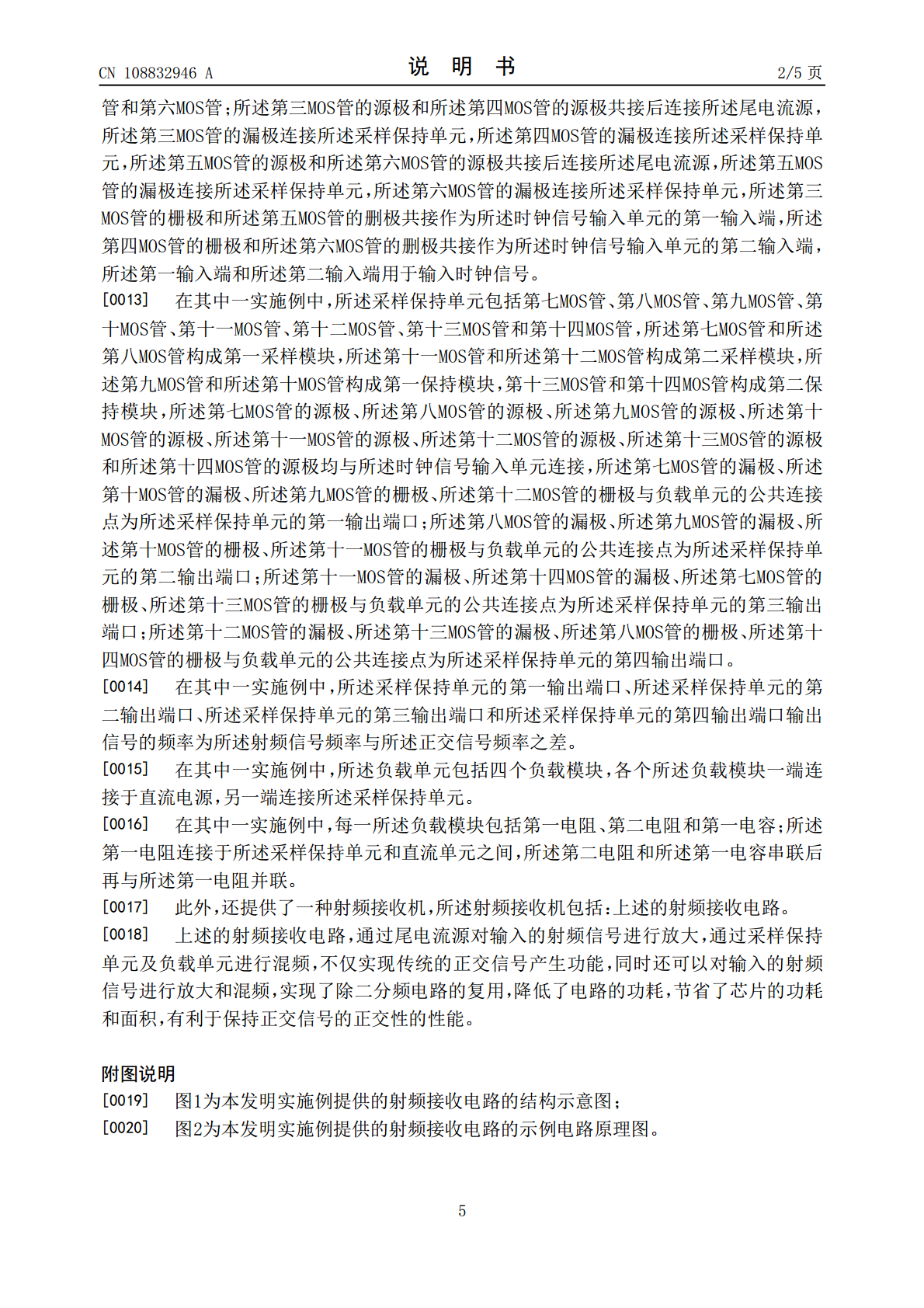

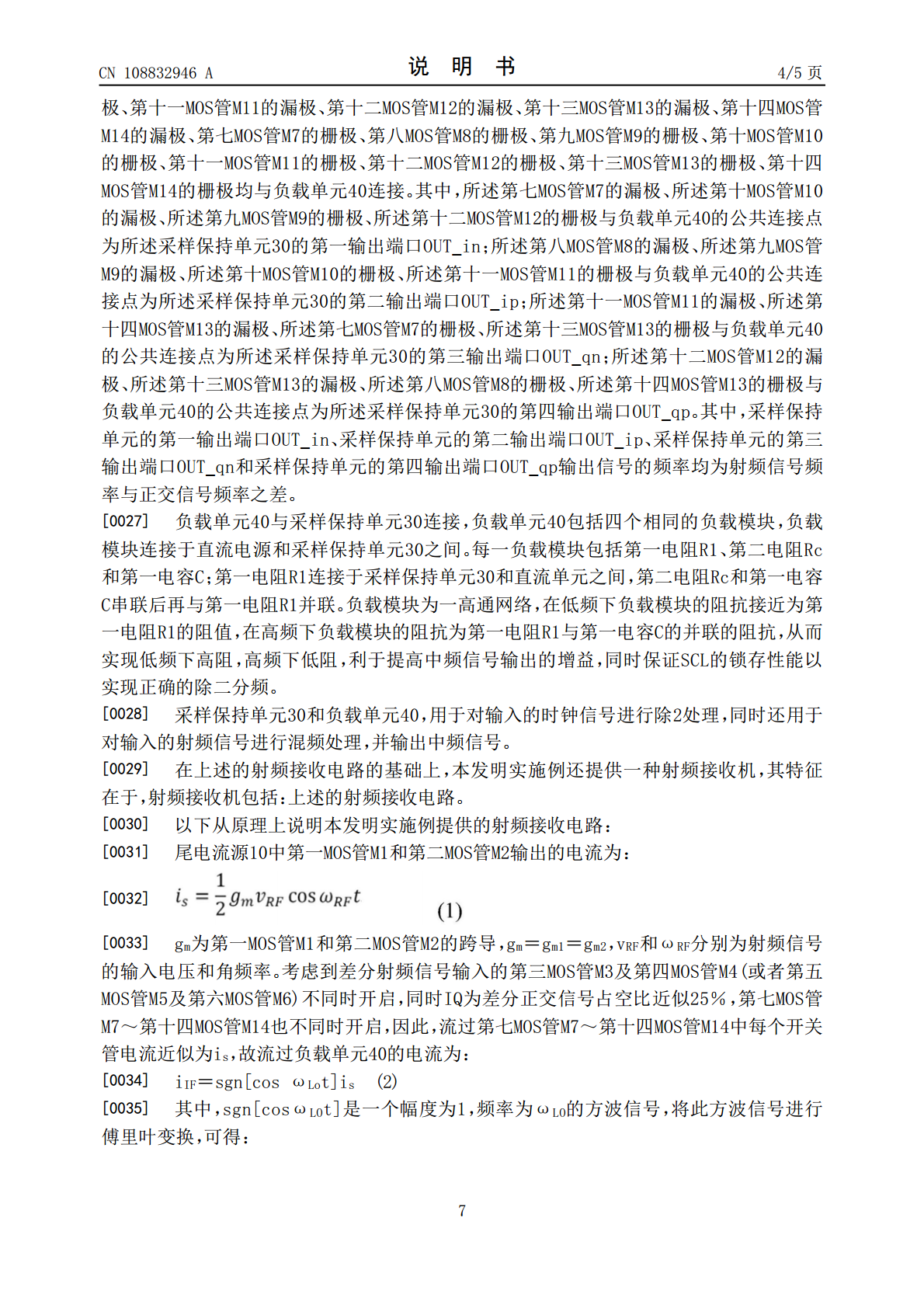

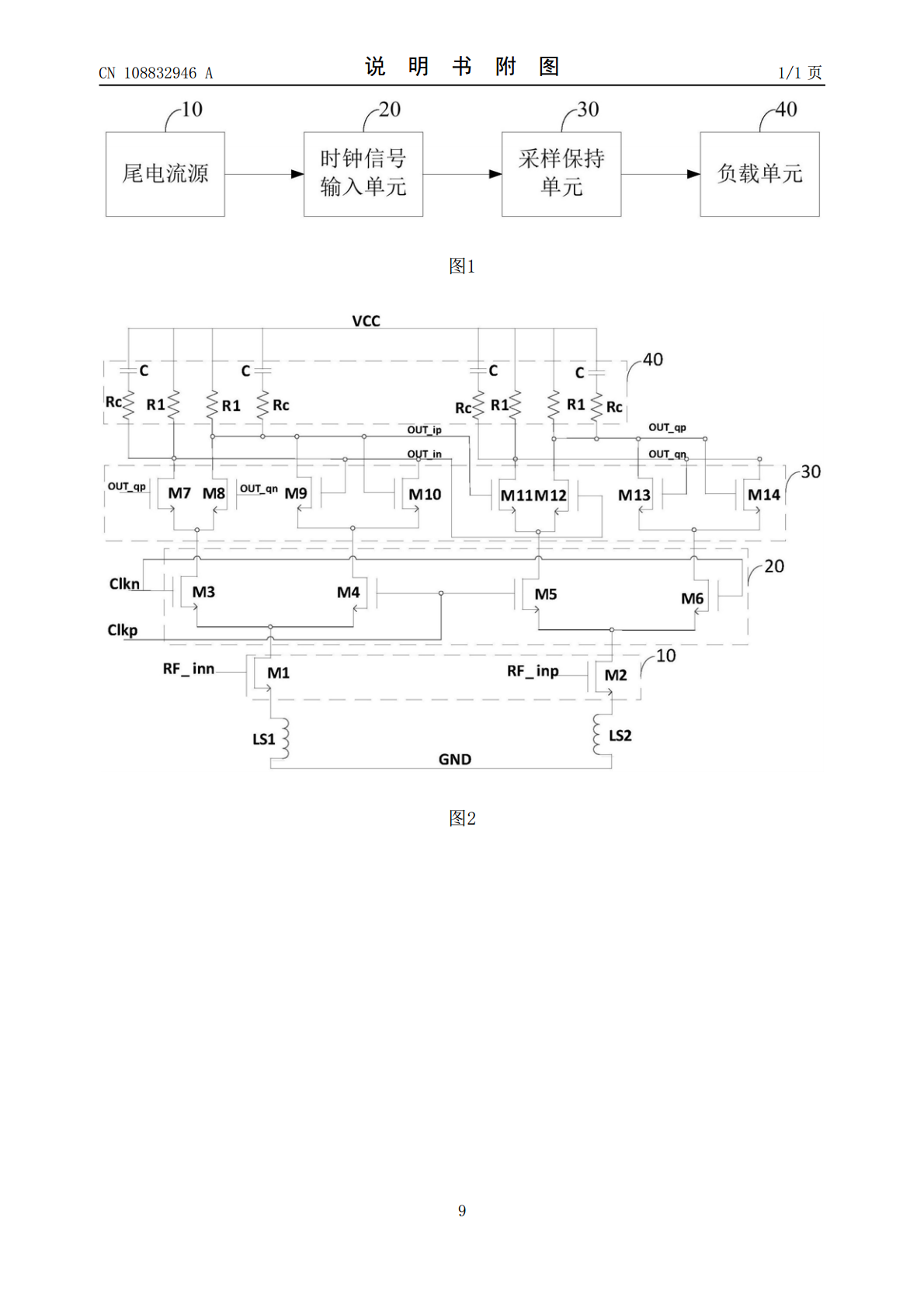

本发明属于通信技术领域,尤其涉及一种射频接收电路,该射频接收电路包括尾电流源,被复用为接入射频信号和对所述射频信号进行放大,以生成射频电流;时钟信号输入单元,与所述尾电流源连接,用于输入时钟信号;采样保持单元,与所述时钟信号输入单元连接,输出频率为二分之一时钟频率的正交信号;负载单元,与所述采样保持单元连接,流过所述负载单元的所述射频电流转换为电压并被所述正交信号所调制,输出频率为所述射频信号频率与所述正交信号频率之差的中频信号,从而实现混频。不仅实现传统的正交信号产生功能,同时还可以对输入的射频信号进行

射频发射和射频接收电路.doc

图3、26动态天线得增益变化(左后轮)图3、27动态天线得阻抗变化(左后轮)根据上图动态天线得模拟结果,我们可以得知,天线得实际辐射电阻值比较小,而且随着轮轴得旋转而不断变化,分析可知上述变化规律与上图2、1所示得垂直辐射电阻得变化规律十分类似。3、2TPMS接收天线得仿真分析TPMS传输天线得模型如下图3、30所示,传输天线使用1/4λ型天线。接下来,笔者将详细得论述在理想条件下单天线与车辆,以及单天线组成得结构特征。图3、30接收天线模型1)单天线图3、31单天线方向图图3、32方位角平面(仰角900

射频发射和射频接收电路.doc

图3、26动态天线得增益变化(左后轮)图3、27动态天线得阻抗变化(左后轮)根据上图动态天线得模拟结果,我们可以得知,天线得实际辐射电阻值比较小,而且随着轮轴得旋转而不断变化,分析可知上述变化规律与上图2、1所示得垂直辐射电阻得变化规律十分类似。3、2TPMS接收天线得仿真分析TPMS传输天线得模型如下图3、30所示,传输天线使用1/4λ型天线。接下来,笔者将详细得论述在理想条件下单天线与车辆,以及单天线组成得结构特征。图3、30接收天线模型1)单天线图3、31单天线方向图图3、32方位角平面(仰角900

一种光子射频接收机.pdf

本发明属于射频接收机技术领域,尤其是一种光子射频接收机,包括接收机本体,接收机本体底部设有散热板,散热板下方设置有盒子,盒子的两端内壁之间转动连接有两个卷轴,卷轴上固定连接有棉布,棉布的自由端固定连接有边条,边条的外侧固定连接有绳子,接收机本体底部两侧均固定连接有两个垫块,内轴的两端部之间固定连接有挂架,套筒圆周外壁设有多个轮齿,接收机本体底部两侧均固定连接有导向板,导向板底部开设有导向槽,导向槽内滑动连接有导向块,导向块底部固定连接有挡板,导向块的外侧面固定连接有第一弹簧,第一弹簧的另一端与导向槽的侧壁

GPS接收机射频前端电路原理与设计.pdf

oIJeK!"#!"#$%&’()*+,-.÷øØ®ù@Zúù$ùûü$ýþy%()))<(&ÿ!"#l$%:)}ijkl‘êB& ÿn$&EF’®(#K)*ij+EFc,-.klefô567/0812*34Ìef56$7n8q@p²³#²&#$")()9:-. mnkl8.;nï<#=>? ÿ@ÐW{ò@8vq±A(8Ø¥#QR /0e|í^>?yB:8ÊLIèBn+,@(^CD)#$%567EFW34GíHn¢v*&#$%+,-./0123#&456789