音频功放电路.pdf

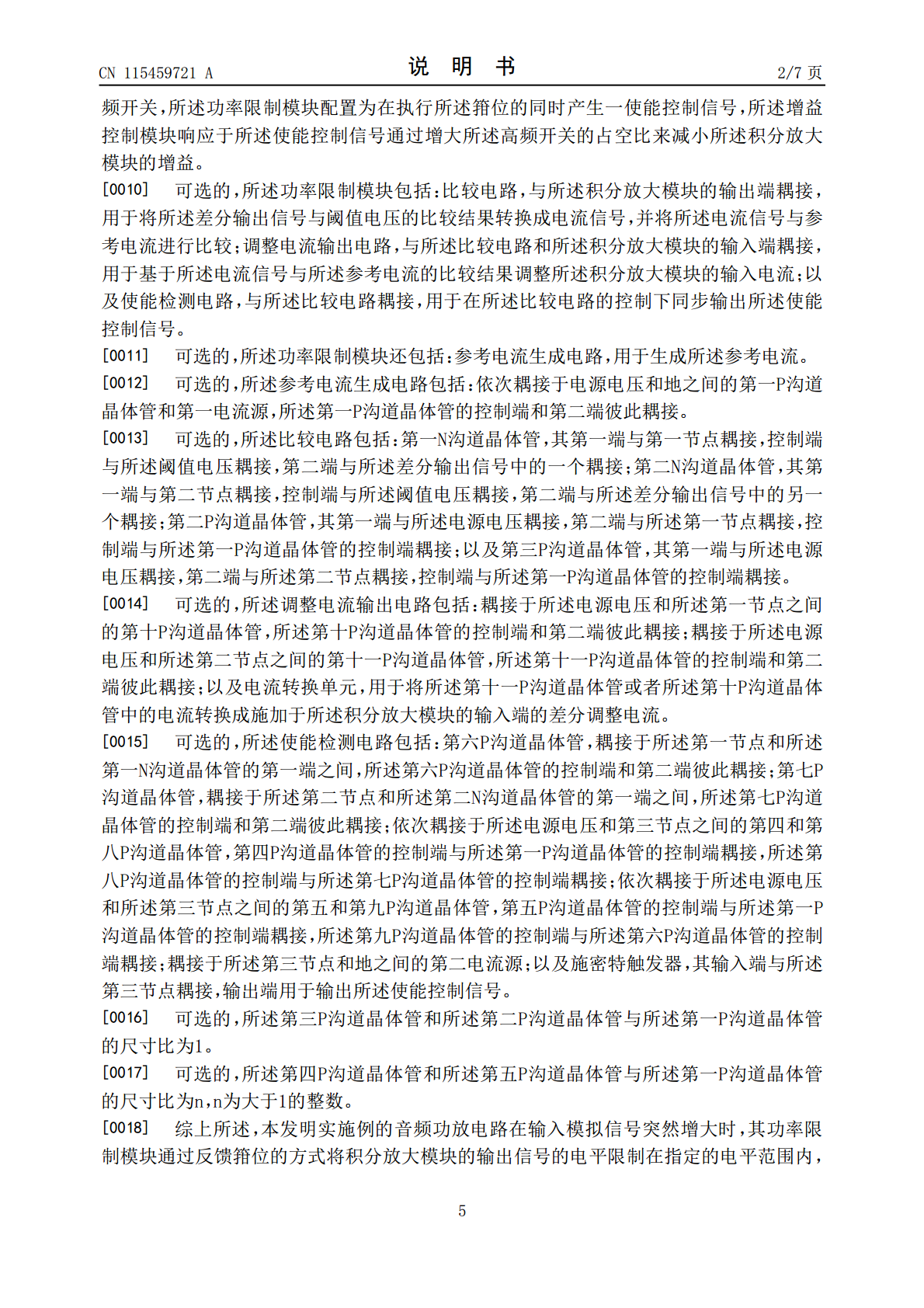

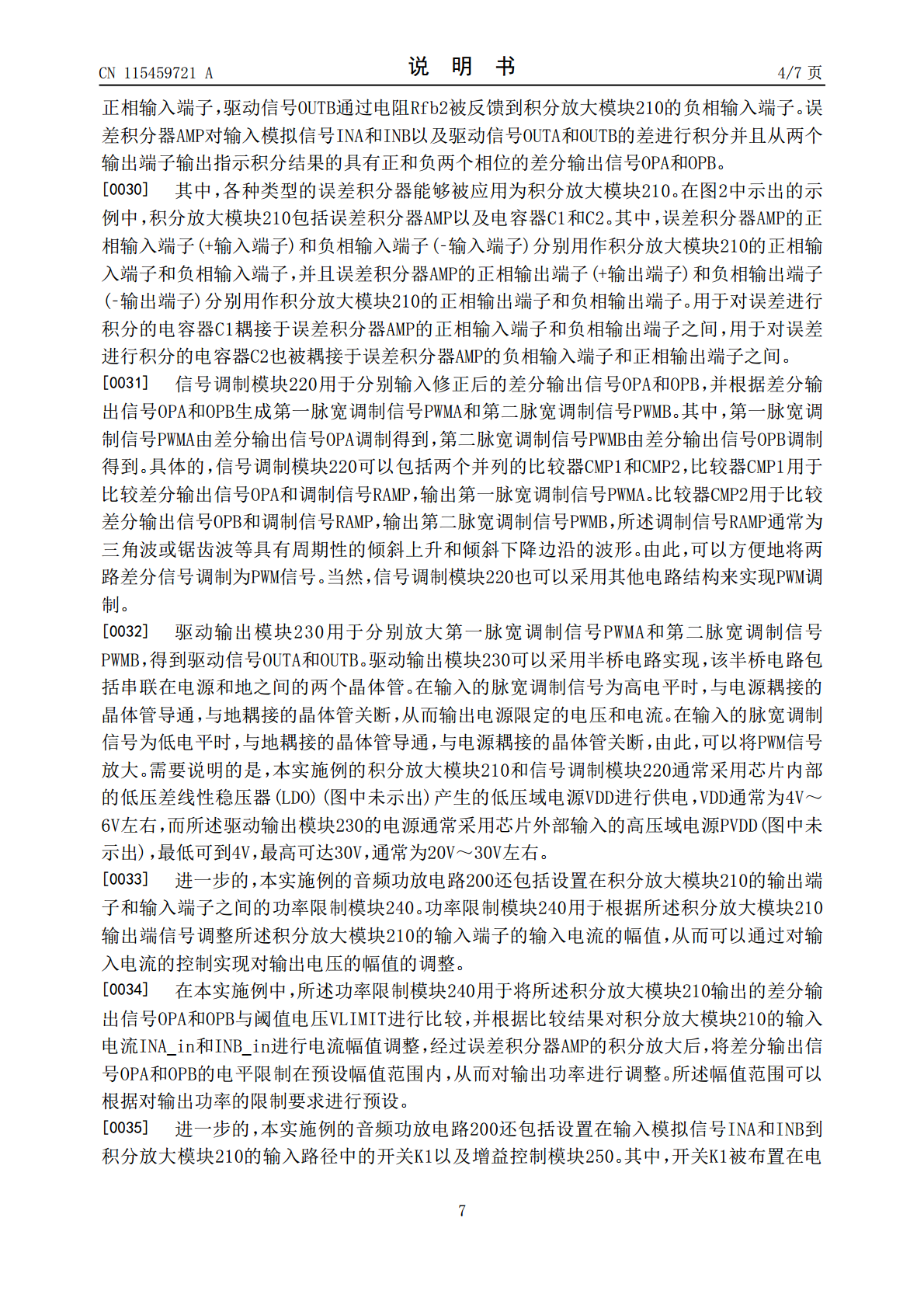

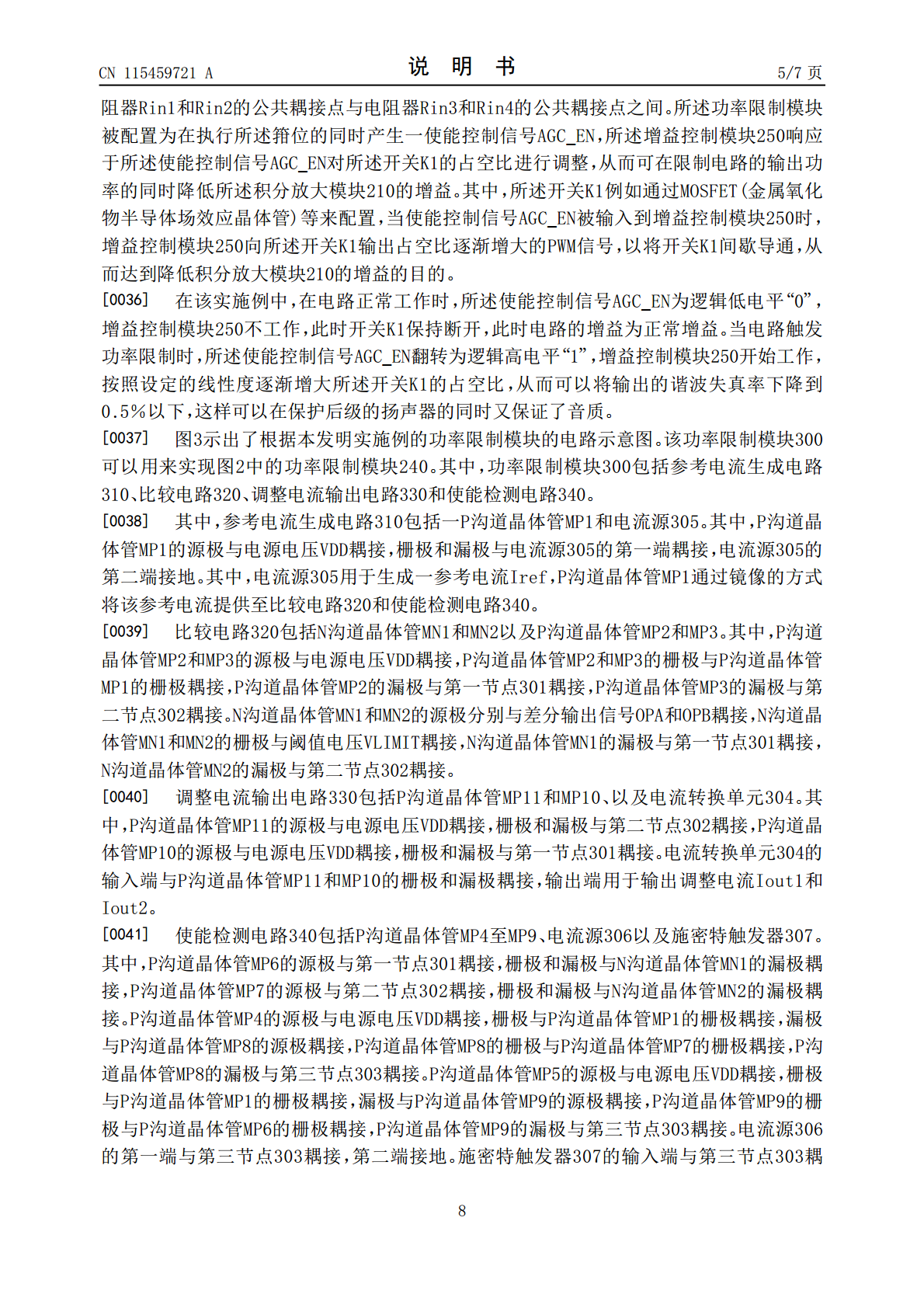

慧红****ad

亲,该文档总共14页,到这已经超出免费预览范围,如果喜欢就直接下载吧~

相关资料

音频功放电路.pdf

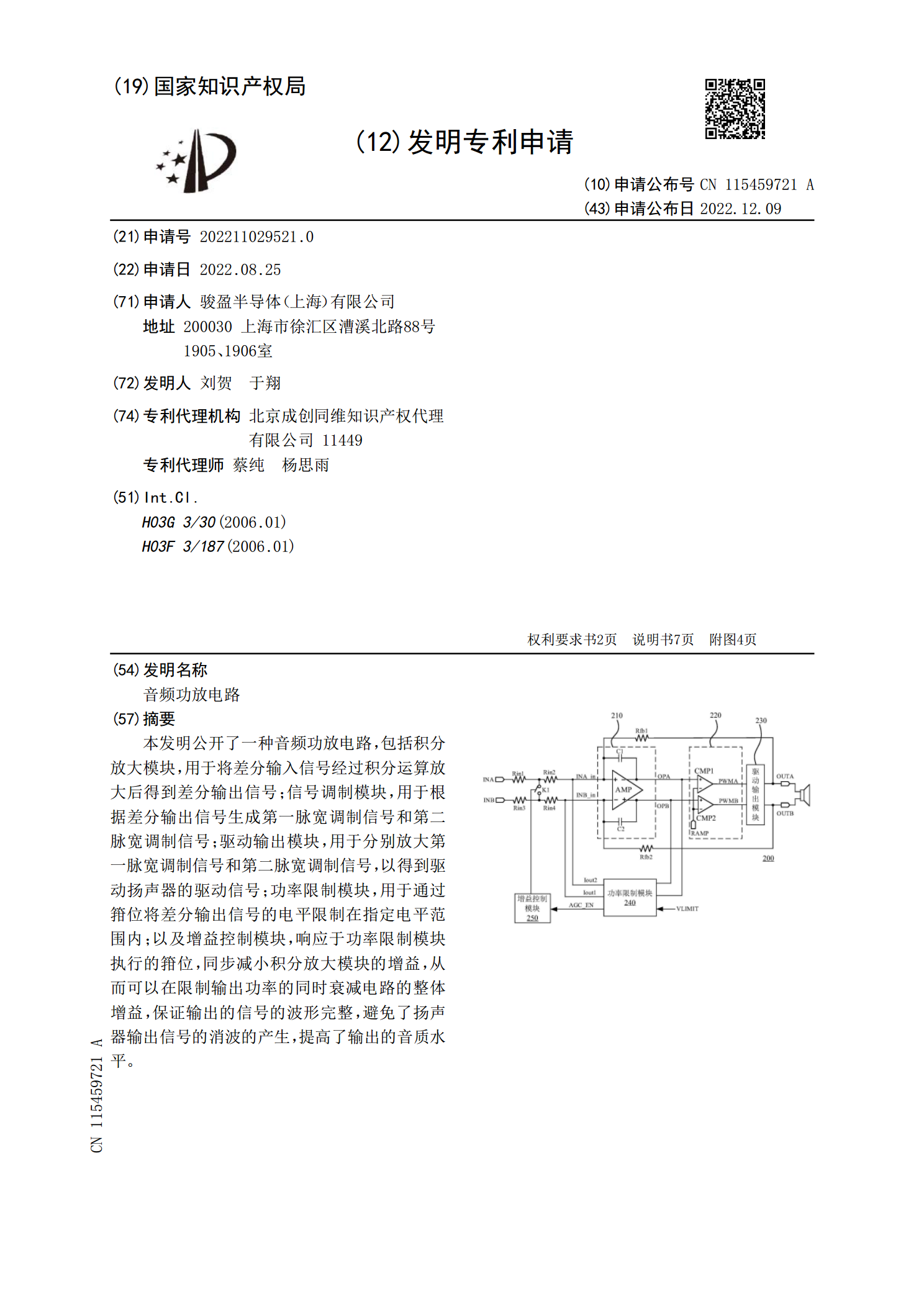

本发明公开了一种音频功放电路,包括积分放大模块,用于将差分输入信号经过积分运算放大后得到差分输出信号;信号调制模块,用于根据差分输出信号生成第一脉宽调制信号和第二脉宽调制信号;驱动输出模块,用于分别放大第一脉宽调制信号和第二脉宽调制信号,以得到驱动扬声器的驱动信号;功率限制模块,用于通过箝位将差分输出信号的电平限制在指定电平范围内;以及增益控制模块,响应于功率限制模块执行的箝位,同步减小积分放大模块的增益,从而可以在限制输出功率的同时衰减电路的整体增益,保证输出的信号的波形完整,避免了扬声器输出信号的消波

音频功放电路.pdf

本发明公开了一种音频功放电路,在该音频功放电路中,由于音频放大电路与DC‑DC变换器复用开关电路,只保留了DC‑DC变换器的开关功能,通过音频放大电路将接收到的音频信号放大,并将放大的音频信号发送到DC‑DC变换器,对DC‑DC变换器生成的开关驱动信号进行调制,得到加载有音频信号的开关驱动信号,该加载有音频信号的开关驱动信号经低通滤波后还原成用于驱动扬声器的音频信号。由于音频放大电路与DC‑DC变换器复用开关电路,将功率放大与直流变换两者合二为一,简化了电路结构,提高了功率转换效率,同时,还缩小了产品体积

音频功放电路及其滤波电路.pdf

本发明公开了一种音频功放电路及其滤波电路,所述滤波电路包括:依次连接于积分放大模块的正输入端和驱动模块的正输出端之间的第一电阻和第二电阻;依次连接于所述积分放大模块的负输入端与所述驱动模块的负输出端之间的第三电阻和第四电阻;以及滤波电容,第一端连接于所述第一电阻和第二电阻相连的第一节点,第二端连接于所述第三电阻和第四电阻相连的第二节点,其中,所述第一电阻和第二电阻的阻值不等,所述第三电阻和第四电阻的阻值不等,从而降低了所述第一节点与所述第二节点之间的最高电压差,使所述最高电压差小于所述滤波电容的耐压值。

音频功放电路及其线性过温保护电路.pdf

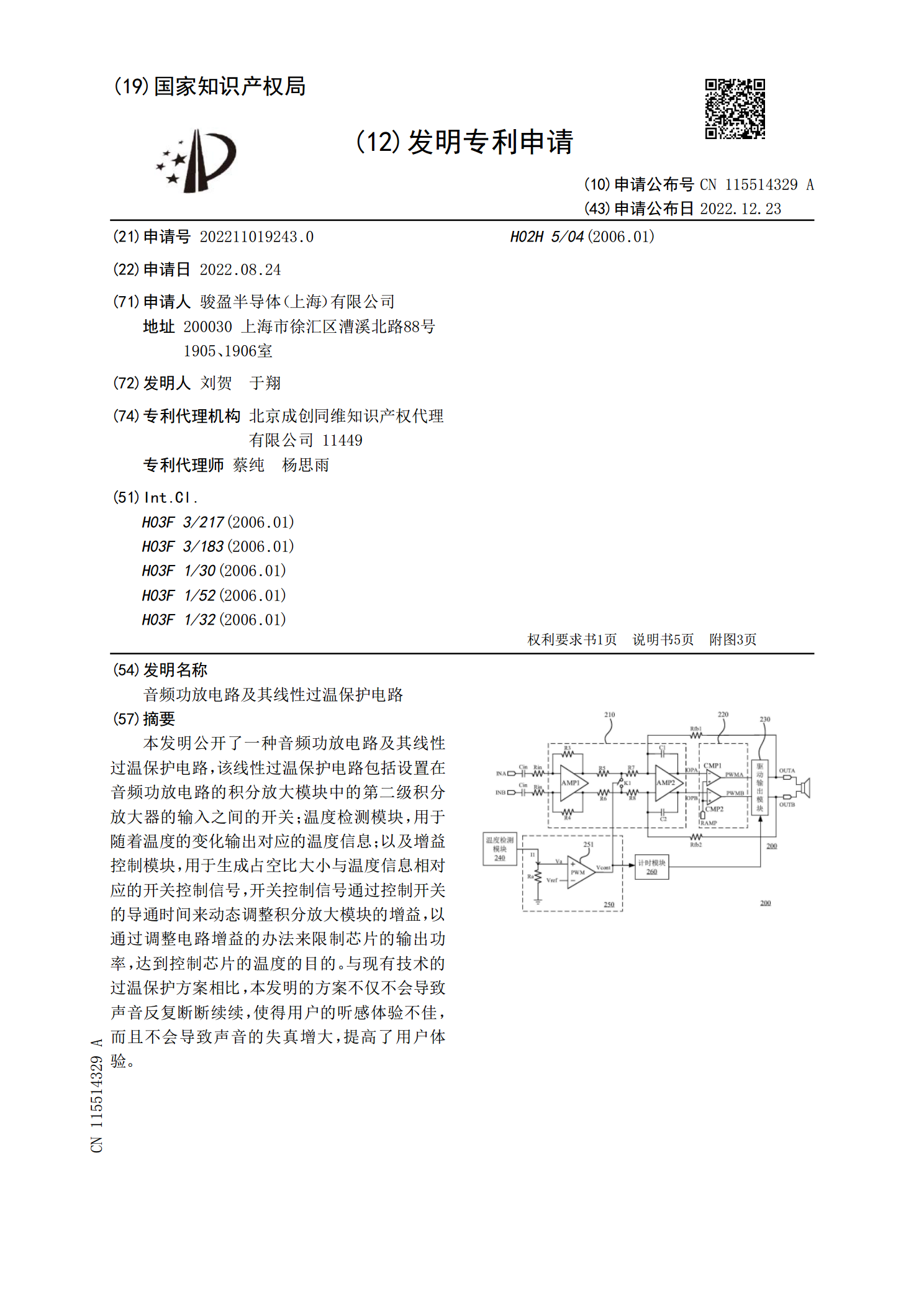

本发明公开了一种音频功放电路及其线性过温保护电路,该线性过温保护电路包括设置在音频功放电路的积分放大模块中的第二级积分放大器的输入之间的开关;温度检测模块,用于随着温度的变化输出对应的温度信息;以及增益控制模块,用于生成占空比大小与温度信息相对应的开关控制信号,开关控制信号通过控制开关的导通时间来动态调整积分放大模块的增益,以通过调整电路增益的办法来限制芯片的输出功率,达到控制芯片的温度的目的。与现有技术的过温保护方案相比,本发明的方案不仅不会导致声音反复断断续续,使得用户的听感体验不佳,而且不会导致声音

音频功放电路及其占空比调制电路和噪音抑制电路.pdf

本发明公开了一种音频功放电路及其占空比调制电路和噪音抑制电路,该音频功放电路包括积分放大模块以及设置在积分放大模块中的第二级积分放大器的输入电阻之间的高频开关,该占空比调制电路用于通过控制高频开关的占空比以调整音频功放电路的增益,其中,占空比调制电路包括:第一计数模块,用于对一占空比调制信号的脉冲进行计数,以获得第一计数值;第二计数模块,用于对时钟信号的脉冲进行计数,以获得第二计数值;以及逻辑输出模块,用于根据第一计数值、第二计数值以及时钟信号进行逻辑运算,以获得控制高频开关的开关调制信号,通过控制音频功