硅基纳米阵列图形化衬底及硅基外延层的制备方法.pdf

是来****文章

在线预览结束,喜欢就下载吧,查找使用更方便

相关资料

硅基纳米阵列图形化衬底及硅基外延层的制备方法.pdf

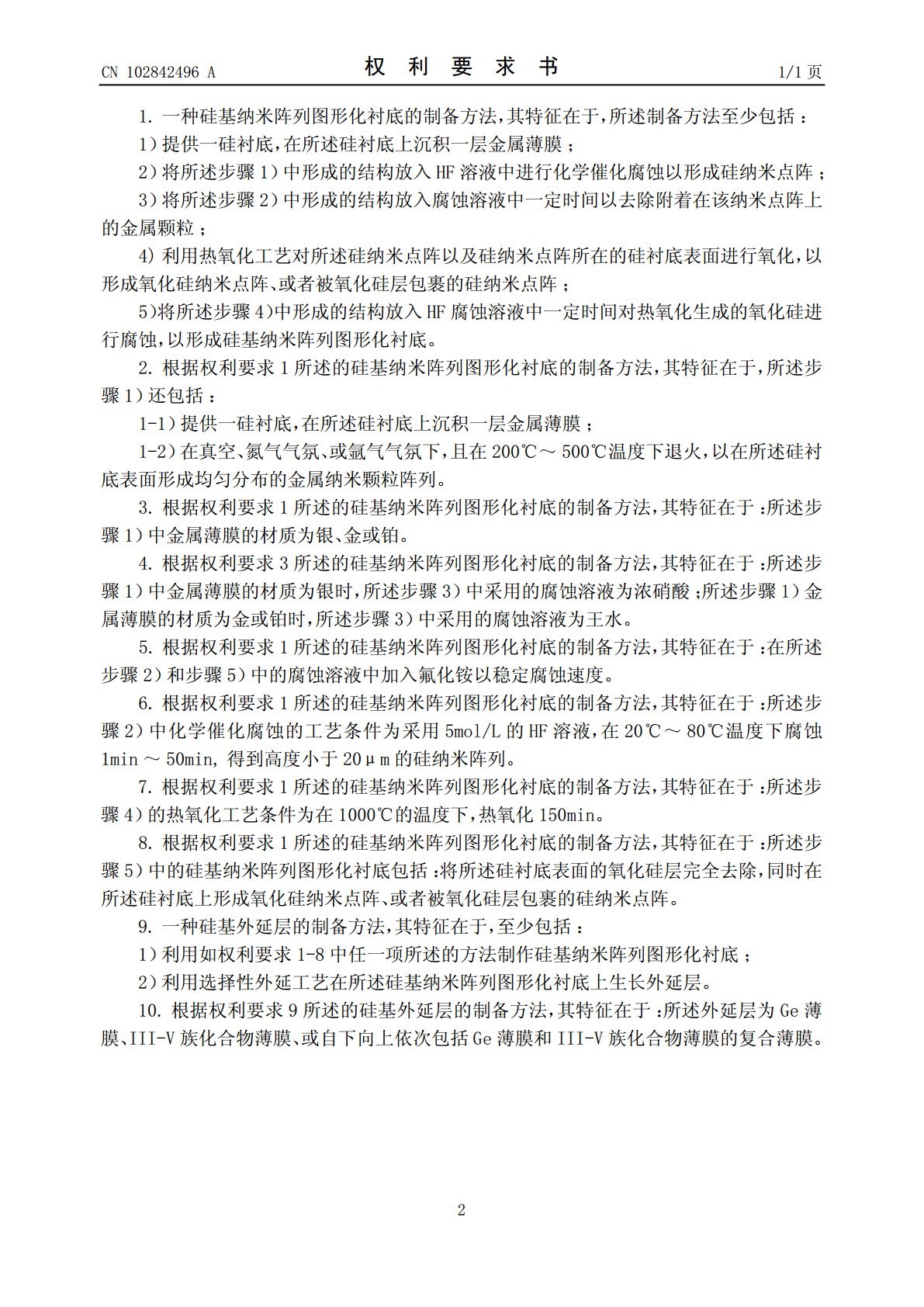

本发明提供一种硅基纳米阵列图形化衬底及硅基外延层的制备方法,该方法利用化学催化腐蚀法制备出硅基纳米阵列图形化衬底,然后在所述硅基纳米阵列图形化衬底上外延Ge或III-V族化合物,从而可以得到低缺陷密度、高晶体质量的Ge或III-V族化合物外延层。此外,本发明的制备工艺简单,成本低,有利于推广使用。

硅基纳米阵列图形化衬底及硅基外延层的制备方法.pdf

本发明提供一种硅基纳米阵列图形化衬底及硅基外延层的制备方法,该方法利用化学催化腐蚀法制备出硅基纳米阵列图形化衬底,然后在所述硅基纳米阵列图形化衬底上外延Ge或III-V族化合物,从而可以得到低缺陷密度、高晶体质量的Ge或III-V族化合物外延层。此外,本发明的制备工艺简单,成本低,有利于推广使用。

一种基于衬底背面外延层的硅基AlGaN/GaN HEMT及制备方法.pdf

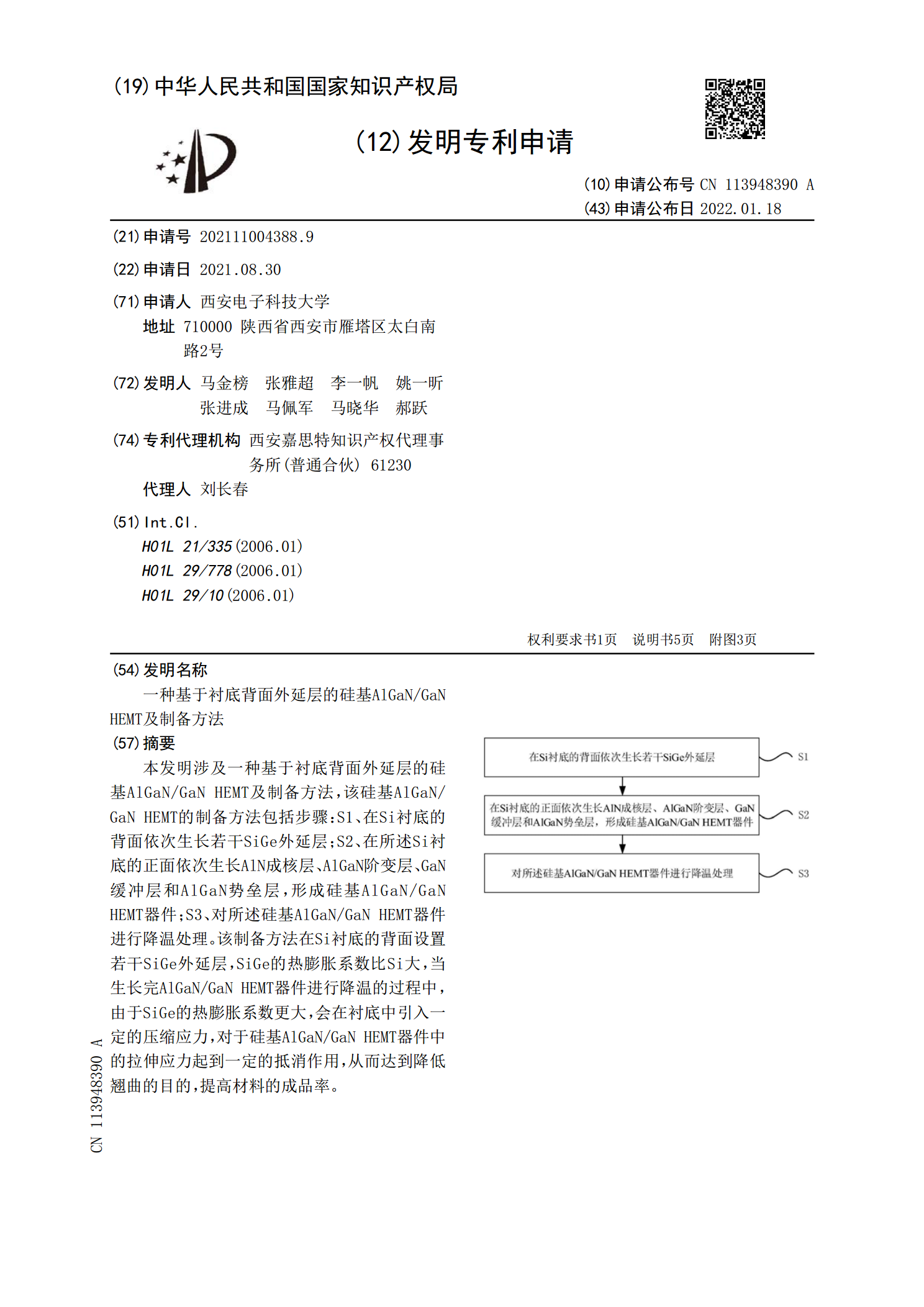

本发明涉及一种基于衬底背面外延层的硅基AlGaN/GaNHEMT及制备方法,该硅基AlGaN/GaNHEMT的制备方法包括步骤:S1、在Si衬底的背面依次生长若干SiGe外延层;S2、在所述Si衬底的正面依次生长AlN成核层、AlGaN阶变层、GaN缓冲层和AlGaN势垒层,形成硅基AlGaN/GaNHEMT器件;S3、对所述硅基AlGaN/GaNHEMT器件进行降温处理。该制备方法在Si衬底的背面设置若干SiGe外延层,SiGe的热膨胀系数比Si大,当生长完AlGaN/GaNHEMT器件进行降

一种基于衬底背面SiSn外延层的硅基AlGaN/GaN HEMT及制备方法.pdf

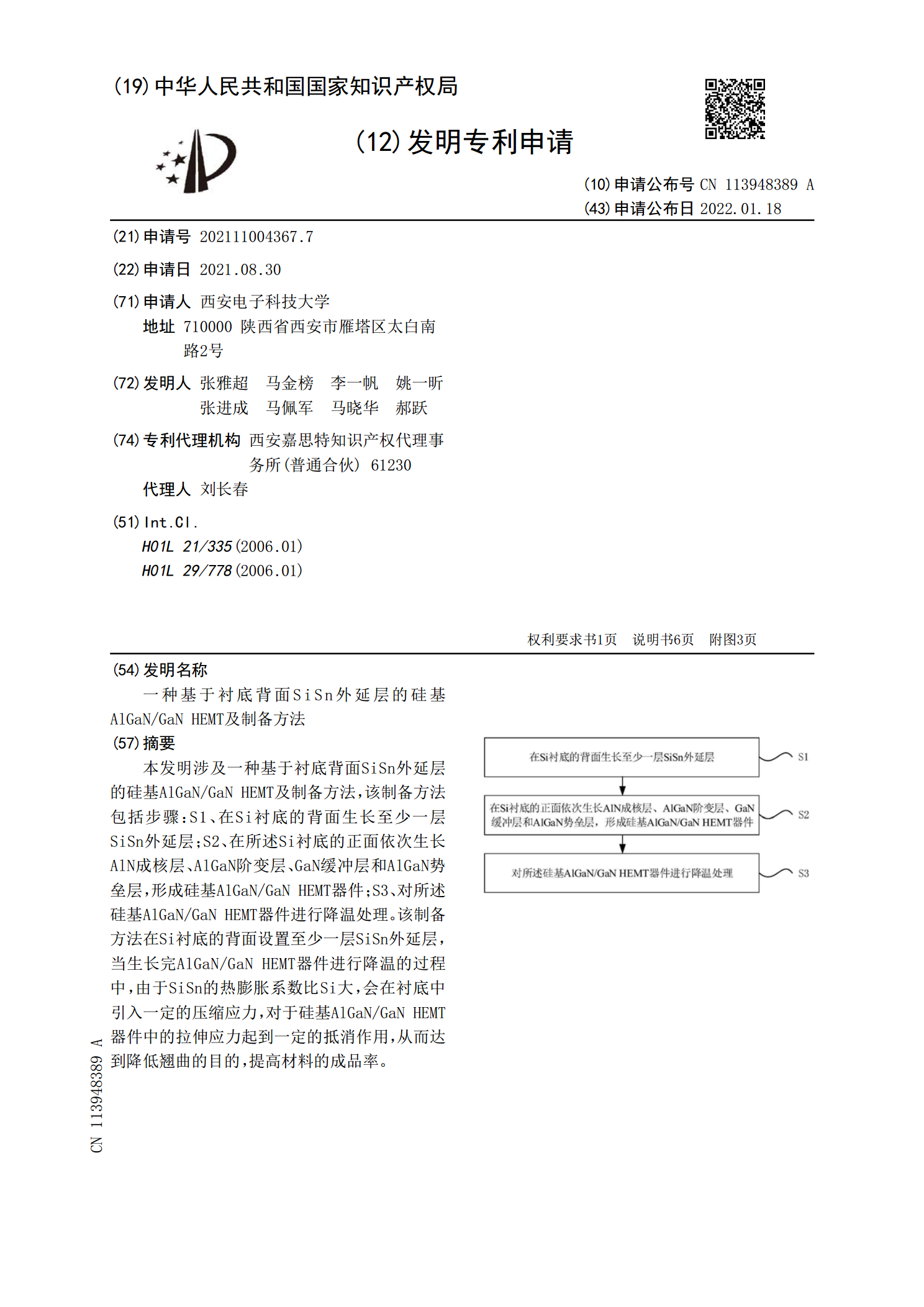

本发明涉及一种基于衬底背面SiSn外延层的硅基AlGaN/GaNHEMT及制备方法,该制备方法包括步骤:S1、在Si衬底的背面生长至少一层SiSn外延层;S2、在所述Si衬底的正面依次生长AlN成核层、AlGaN阶变层、GaN缓冲层和AlGaN势垒层,形成硅基AlGaN/GaNHEMT器件;S3、对所述硅基AlGaN/GaNHEMT器件进行降温处理。该制备方法在Si衬底的背面设置至少一层SiSn外延层,当生长完AlGaN/GaNHEMT器件进行降温的过程中,由于SiSn的热膨胀系数比Si大,会在衬

一种基于衬底背面GeSnSi外延层的硅基AlGaN/GaN HEMT及制备方法.pdf

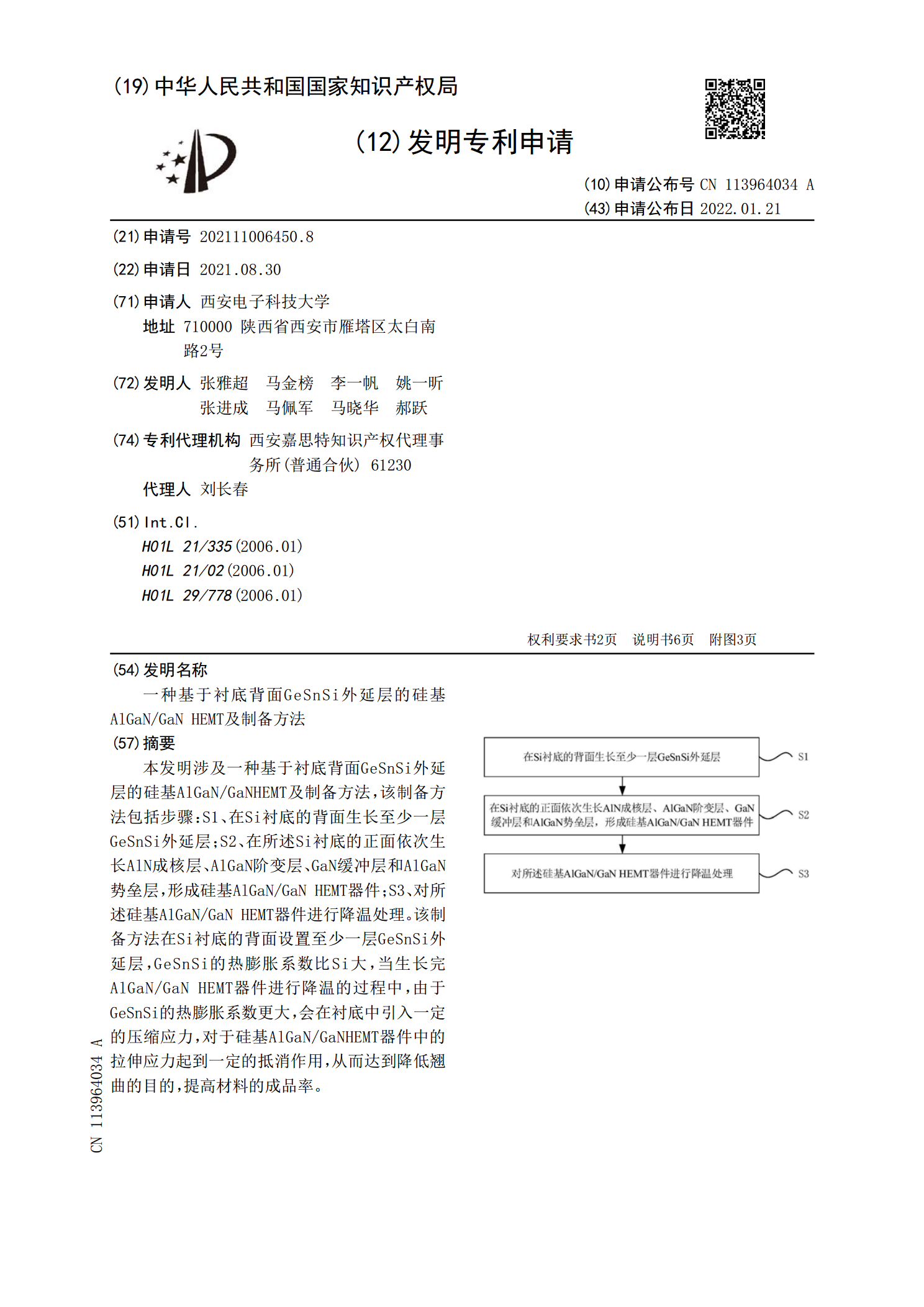

本发明涉及一种基于衬底背面GeSnSi外延层的硅基AlGaN/GaNHEMT及制备方法,该制备方法包括步骤:S1、在Si衬底的背面生长至少一层GeSnSi外延层;S2、在所述Si衬底的正面依次生长AlN成核层、AlGaN阶变层、GaN缓冲层和AlGaN势垒层,形成硅基AlGaN/GaNHEMT器件;S3、对所述硅基AlGaN/GaNHEMT器件进行降温处理。该制备方法在Si衬底的背面设置至少一层GeSnSi外延层,GeSnSi的热膨胀系数比Si大,当生长完AlGaN/GaNHEMT器件进行降温的过程