控制系统、方法、装置、电子设备及可读存储介质.pdf

努力****凌芹

亲,该文档总共26页,到这已经超出免费预览范围,如果喜欢就直接下载吧~

相关资料

控制系统、方法、装置、电子设备及可读存储介质.pdf

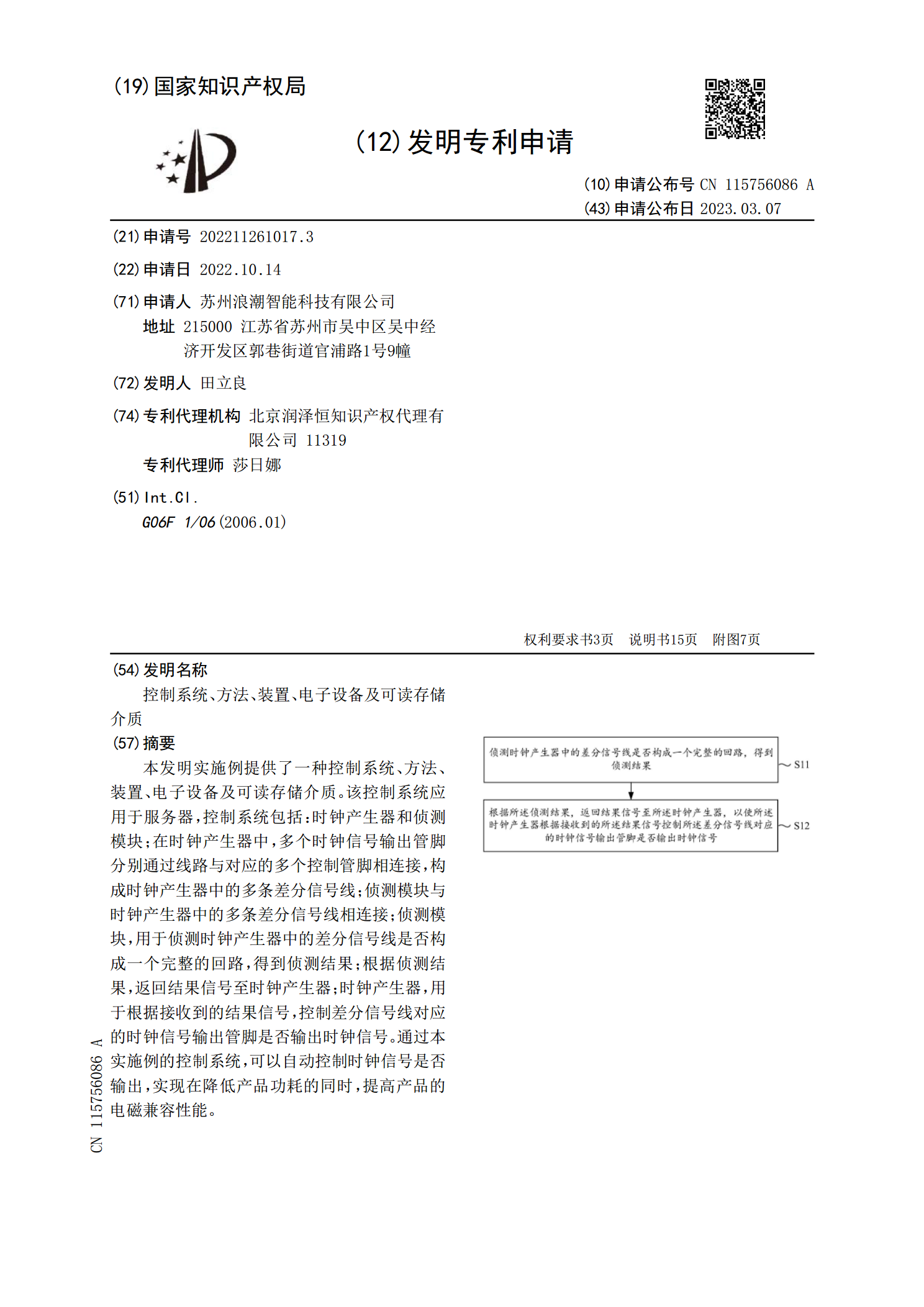

本发明实施例提供了一种控制系统、方法、装置、电子设备及可读存储介质。该控制系统应用于服务器,控制系统包括:时钟产生器和侦测模块;在时钟产生器中,多个时钟信号输出管脚分别通过线路与对应的多个控制管脚相连接,构成时钟产生器中的多条差分信号线;侦测模块与时钟产生器中的多条差分信号线相连接;侦测模块,用于侦测时钟产生器中的差分信号线是否构成一个完整的回路,得到侦测结果;根据侦测结果,返回结果信号至时钟产生器;时钟产生器,用于根据接收到的结果信号,控制差分信号线对应的时钟信号输出管脚是否输出时钟信号。通过本实施例的

数据存储方法、装置、电子设备及可读存储介质.pdf

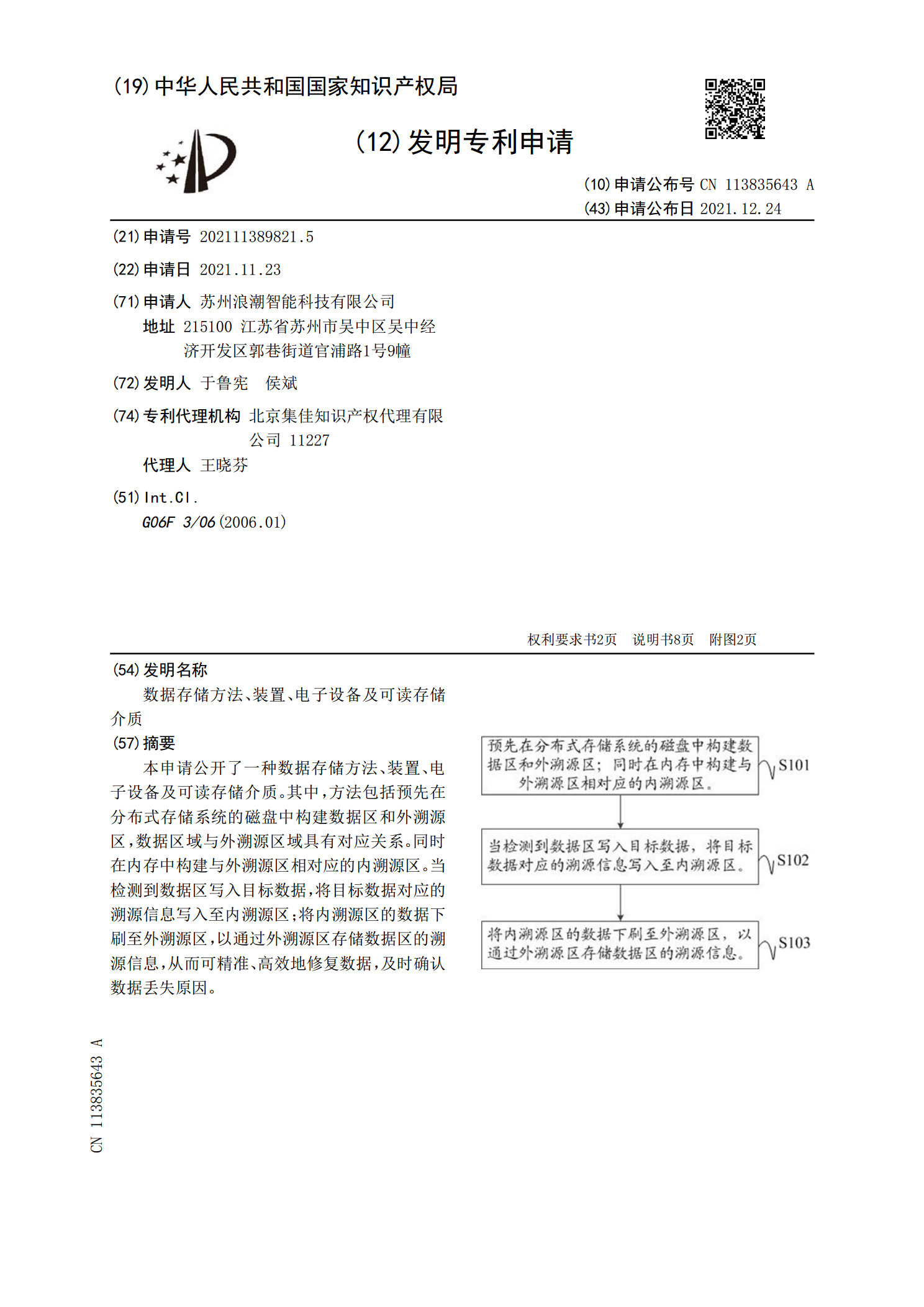

本申请公开了一种数据存储方法、装置、电子设备及可读存储介质。其中,方法包括预先在分布式存储系统的磁盘中构建数据区和外溯源区,数据区域与外溯源区域具有对应关系。同时在内存中构建与外溯源区相对应的内溯源区。当检测到数据区写入目标数据,将目标数据对应的溯源信息写入至内溯源区;将内溯源区的数据下刷至外溯源区,以通过外溯源区存储数据区的溯源信息,从而可精准、高效地修复数据,及时确认数据丢失原因。

拍摄方法、装置、电子设备及可读存储介质.pdf

本申请公开了一种拍摄方法、装置、电子设备及可读存储介质。该方法包括:在拍摄预览界面显示第一图像的情况下,获取第一图像的特征信息;根据特征信息,确定第一图像的质量信息;根据第一图像的质量信息输出目标图像。

输入方法、装置、电子设备及可读存储介质.pdf

本申请公开了一种输入方法、装置、电子设备及可读存储介质,属于通信技术领域。该方法包括:接收用户在输入法的内容输入区域的第一输入,第一输入为在内容输入区域瞄定M个按键位置的输入,每个按键位置对应虚拟键盘中的一个预设瞄定按键,M为大于1的整数;响应于第一输入,基于M个按键位置,在内容输入区域中显示虚拟键盘;接收用户对虚拟键盘中的目标虚拟按键的第二输入;响应于第二输入,显示与目标虚拟按键对应的内容。

对话方法、装置、电子设备及可读存储介质.pdf

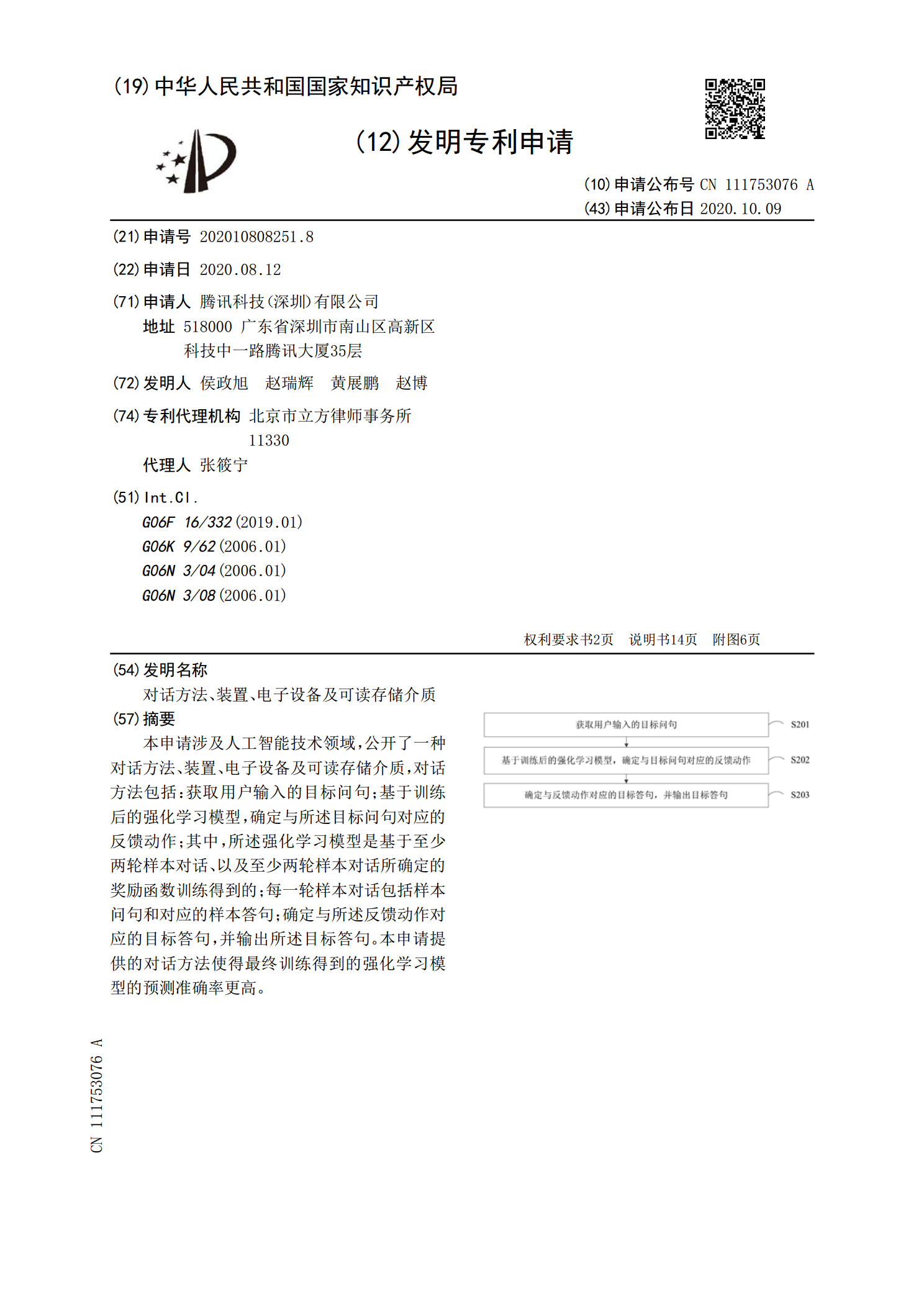

本申请涉及人工智能技术领域,公开了一种对话方法、装置、电子设备及可读存储介质,对话方法包括:获取用户输入的目标问句;基于训练后的强化学习模型,确定与所述目标问句对应的反馈动作;其中,所述强化学习模型是基于至少两轮样本对话、以及至少两轮样本对话所确定的奖励函数训练得到的;每一轮样本对话包括样本问句和对应的样本答句;确定与所述反馈动作对应的目标答句,并输出所述目标答句。本申请提供的对话方法使得最终训练得到的强化学习模型的预测准确率更高。