智能插座.pdf

秀华****魔王

在线预览结束,喜欢就下载吧,查找使用更方便

相关资料

智能插座.pdf

本发明提供一种智能插座包括插座本体,插座本体上设有插脚和至少一个插孔;插座本体外部设有数据接口,数据接口通过总线连接外部设备;插座本体内设有微处理器,电源转换单元,外部设备检测单元,输出控制单元,指示单元;其中外部设备检测单元分别连接数据接口和微处理器,检测数据接口是否连接外部设备,并将信息传输给微处理器;微处理器收集数据信息,并进行数据分析,控制智能插座,实现通信和显示输出;输出控制单元控制智能插座的输出开启或关闭。在保留电源转换连接作用的基础上,实现数据的采集,传输和处理,以及信息交互控制。通过一个数

智能插座.pdf

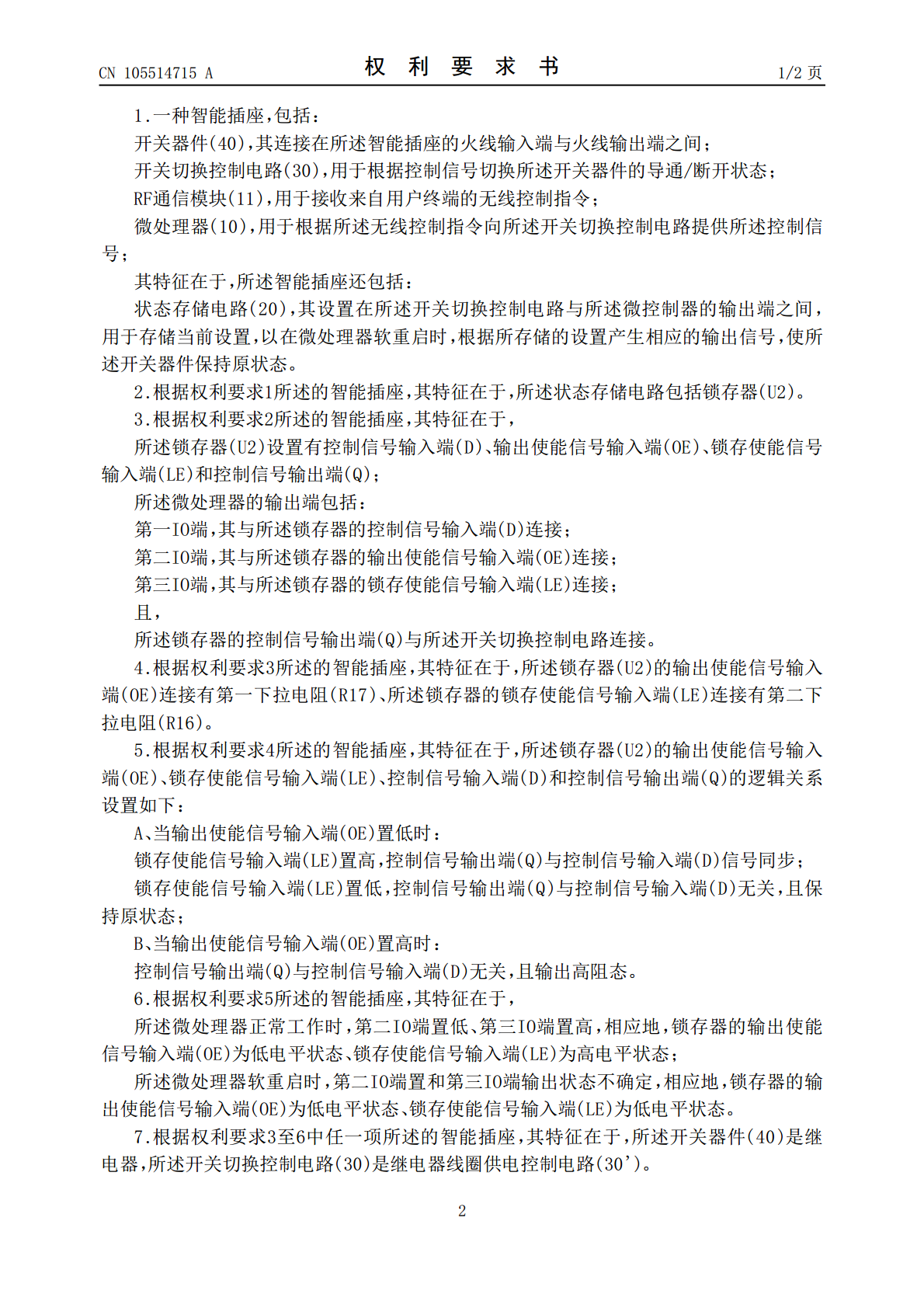

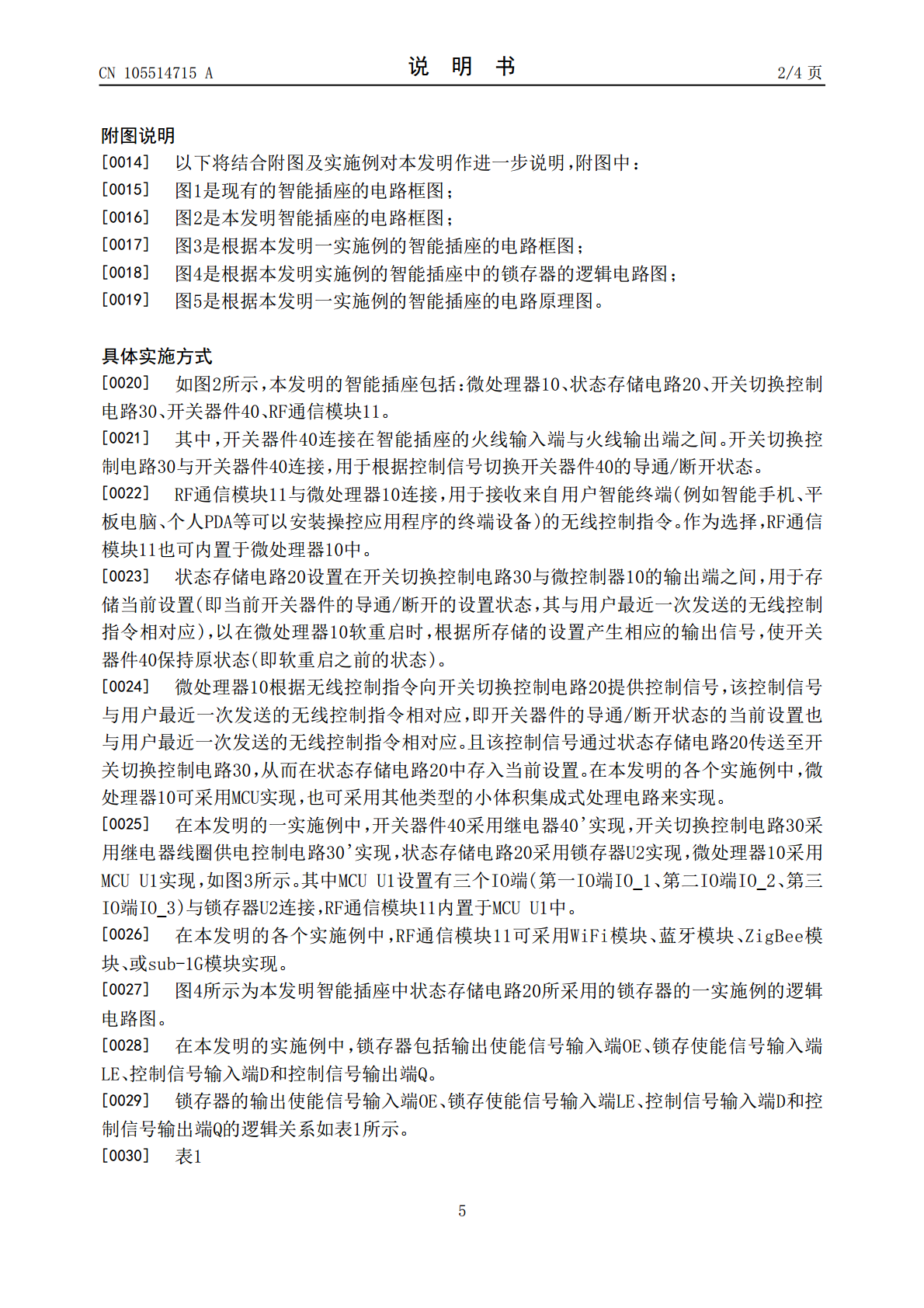

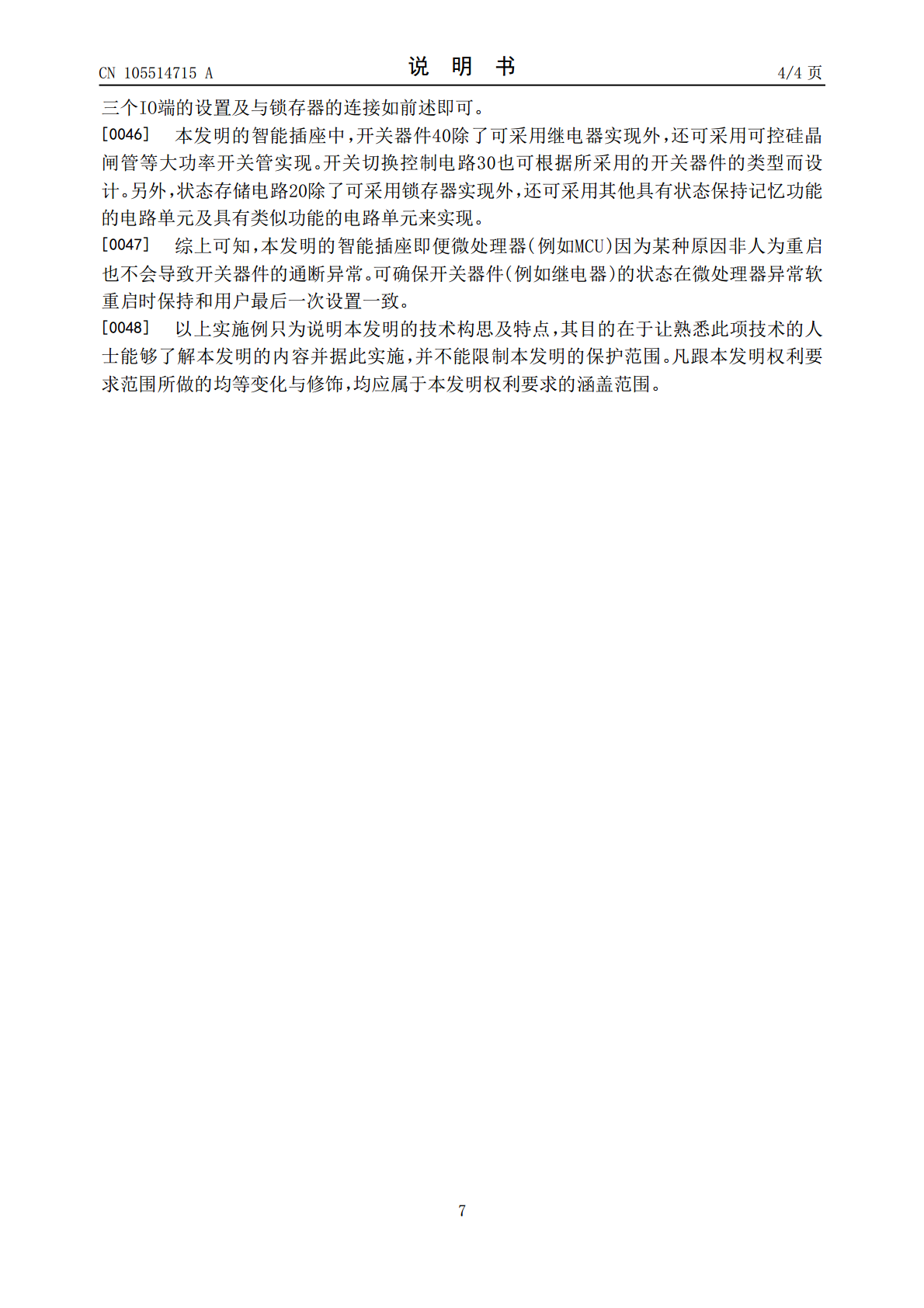

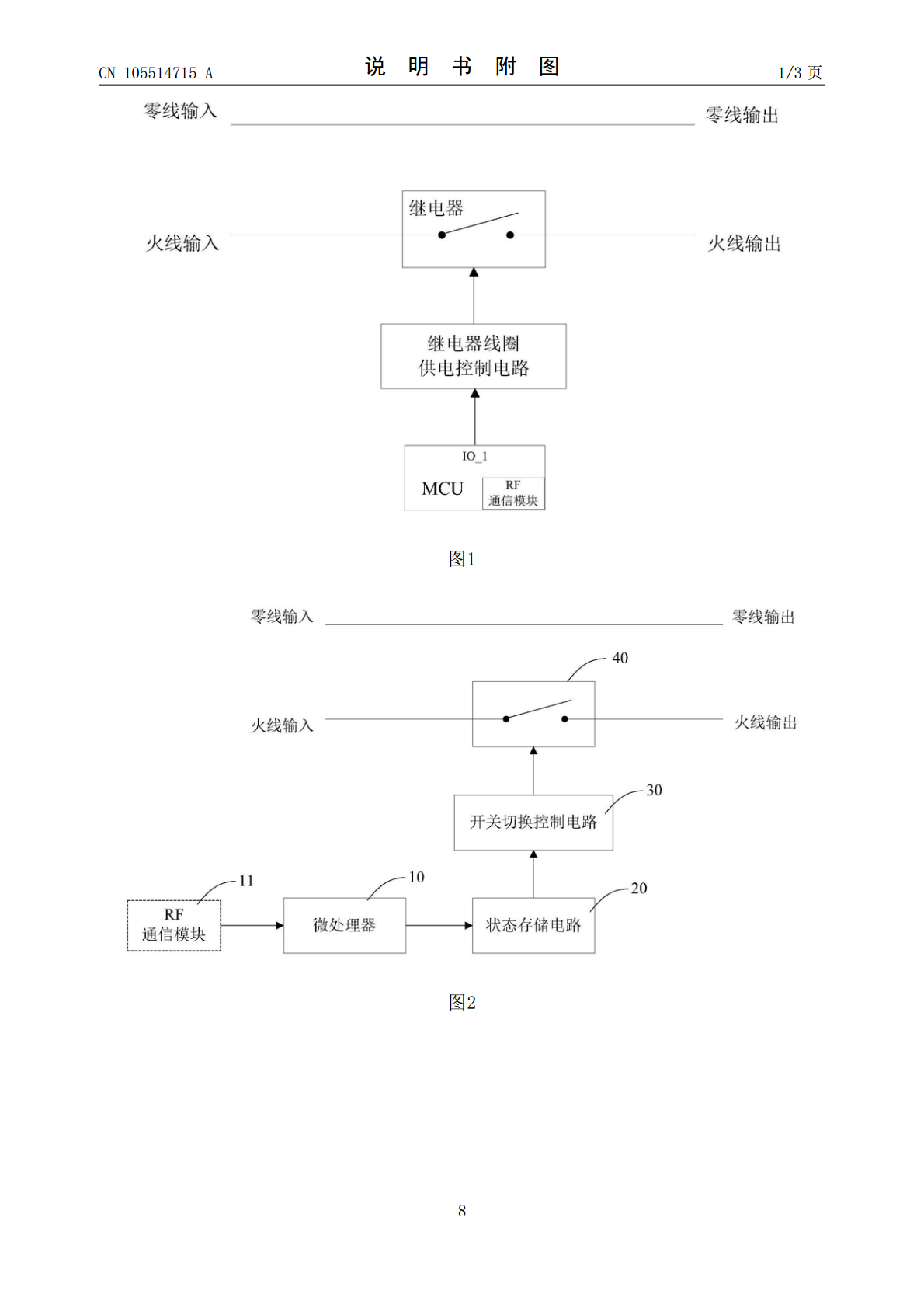

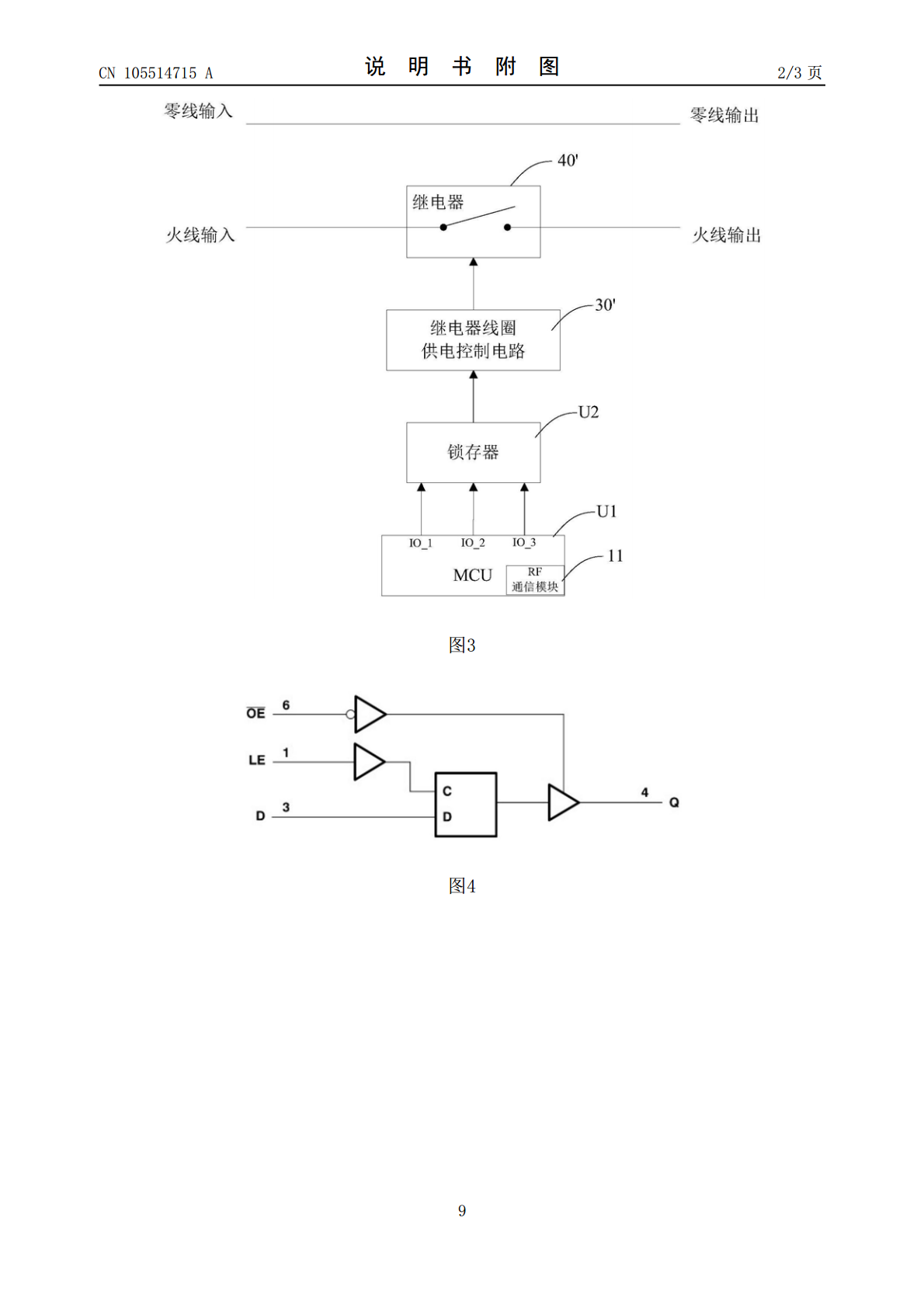

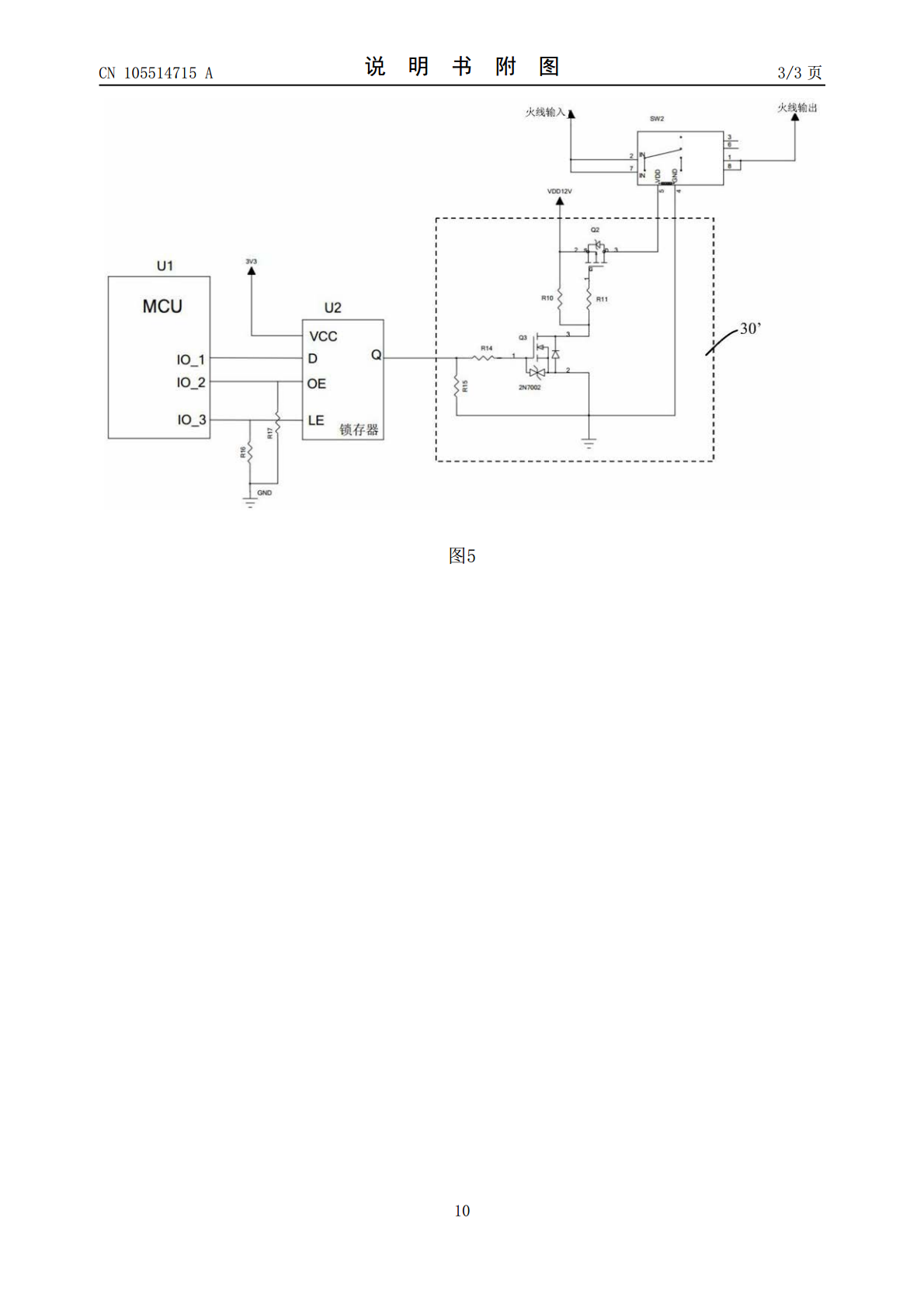

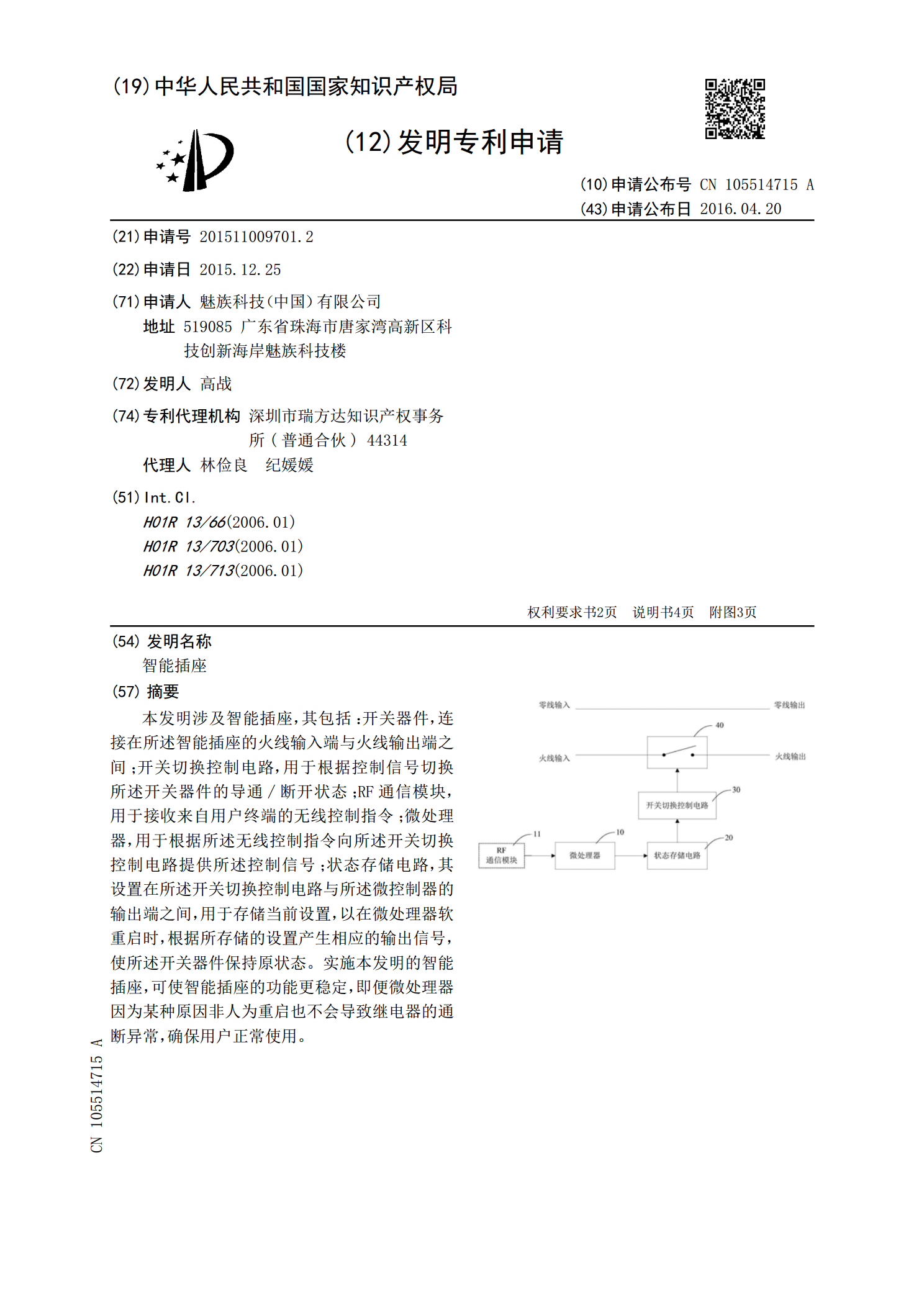

本发明涉及智能插座,其包括:开关器件,连接在所述智能插座的火线输入端与火线输出端之间;开关切换控制电路,用于根据控制信号切换所述开关器件的导通/断开状态;RF通信模块,用于接收来自用户终端的无线控制指令;微处理器,用于根据所述无线控制指令向所述开关切换控制电路提供所述控制信号;状态存储电路,其设置在所述开关切换控制电路与所述微控制器的输出端之间,用于存储当前设置,以在微处理器软重启时,根据所存储的设置产生相应的输出信号,使所述开关器件保持原状态。实施本发明的智能插座,可使智能插座的功能更稳定,即便微处理器

智能插座.pdf

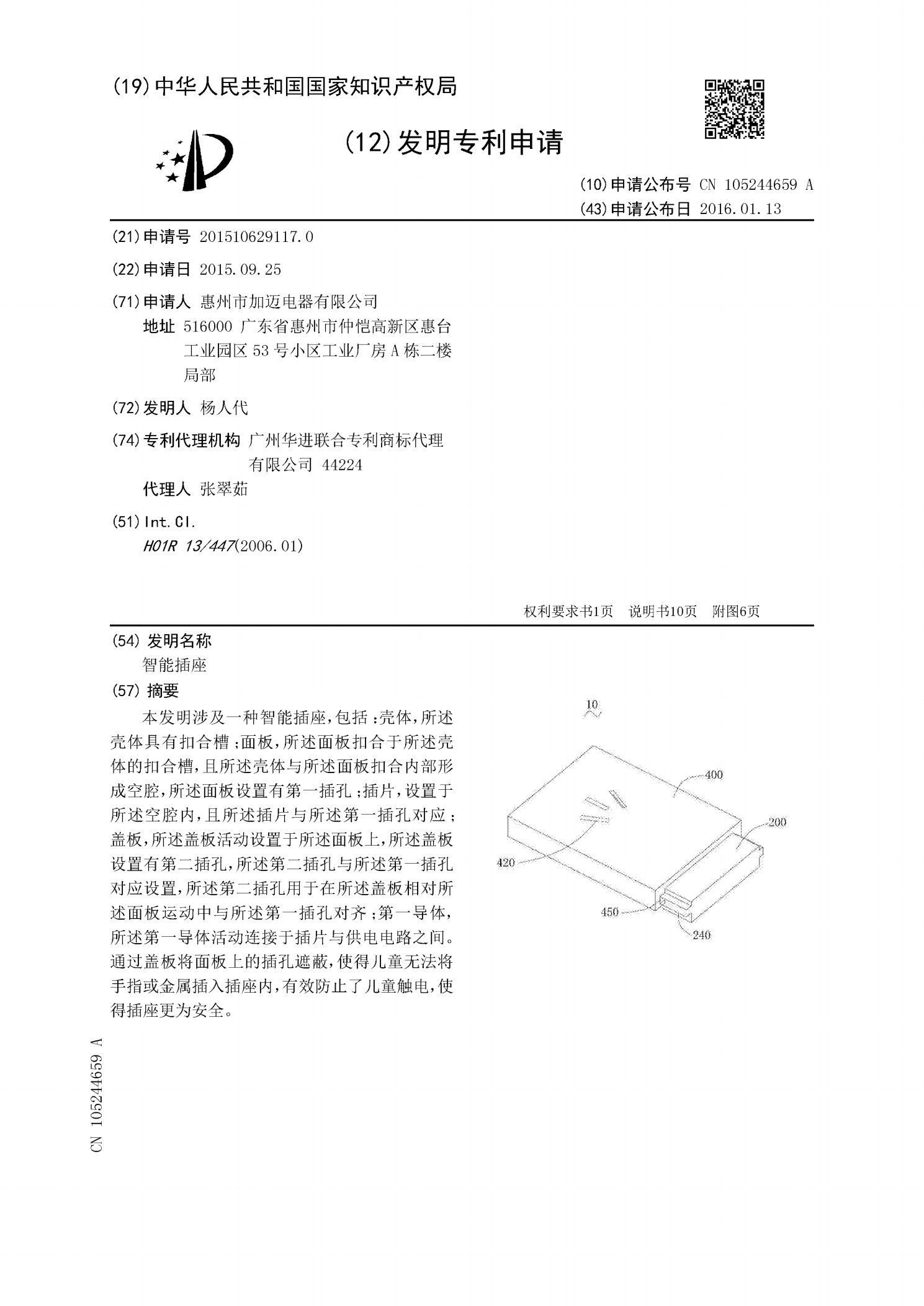

本发明涉及一种智能插座,包括:壳体,所述壳体具有扣合槽;面板,所述面板扣合于所述壳体的扣合槽,且所述壳体与所述面板扣合内部形成空腔,所述面板设置有第一插孔;插片,设置于所述空腔内,且所述插片与所述第一插孔对应;盖板,所述盖板活动设置于所述面板上,所述盖板设置有第二插孔,所述第二插孔与所述第一插孔对应设置,所述第二插孔用于在所述盖板相对所述面板运动中与所述第一插孔对齐;第一导体,所述第一导体活动连接于插片与供电电路之间。通过盖板将面板上的插孔遮蔽,使得儿童无法将手指或金属插入插座内,有效防止了儿童触电,使得

智能插座.pdf

本发明公开的智能插座,其包括前面板,其设置有供电插孔。壳体,其容纳有供电的电源基座,该电源基座上设置有深度与电源插头长度匹配的插孔。智能插座还包括信息检测单元,用于以设定频率检测并输出智能插座的工作状态信息。信息存储单元,用于存储信息检测单元输出的工作状态信息或者其他智能插座的信息。通信单元,用于与其他设备或其他智能插座通信,实现信息的读取、发送或接收,在智能插座的工作状态信息发生变化时将变化的工作状态信息发送给其他智能插座。显示单元,其位于前面板上,轮番显示信息存储单元中存储的各智能插座的工作状态或通信

智能防潮插座.pdf

本发明公开了一种智能防潮插座,包括:插座主体,其一侧设有电源线、上表面设有多个插孔、内部设有电器元件以及相邻两个插孔之间设有竖直的隔板,所述隔板将所述插座主体分隔成多个插孔空间;多个加热机构,其包括从下至上依次敷设的第一防火涂料层、陶瓷层、第二防火涂料层、导热硅胶壳体,导热硅胶壳体内部设有电热丝、外部设有蓄电池;多个抽湿机构,其包括穿设在插座主体侧壁上的导风管、敷设在导风管内壁上的隔音层、以及设置在隔音层上的抽风机;控制机构,其包括湿度传感器、插孔开关和蜂鸣器、以及控制器。本发明具有检测插座湿度、并根据湿