一种半导体光电探测器芯片及其制备方法.pdf

是你****元呀

亲,该文档总共12页,到这已经超出免费预览范围,如果喜欢就直接下载吧~

相关资料

一种半导体光电探测器芯片及其制备方法.pdf

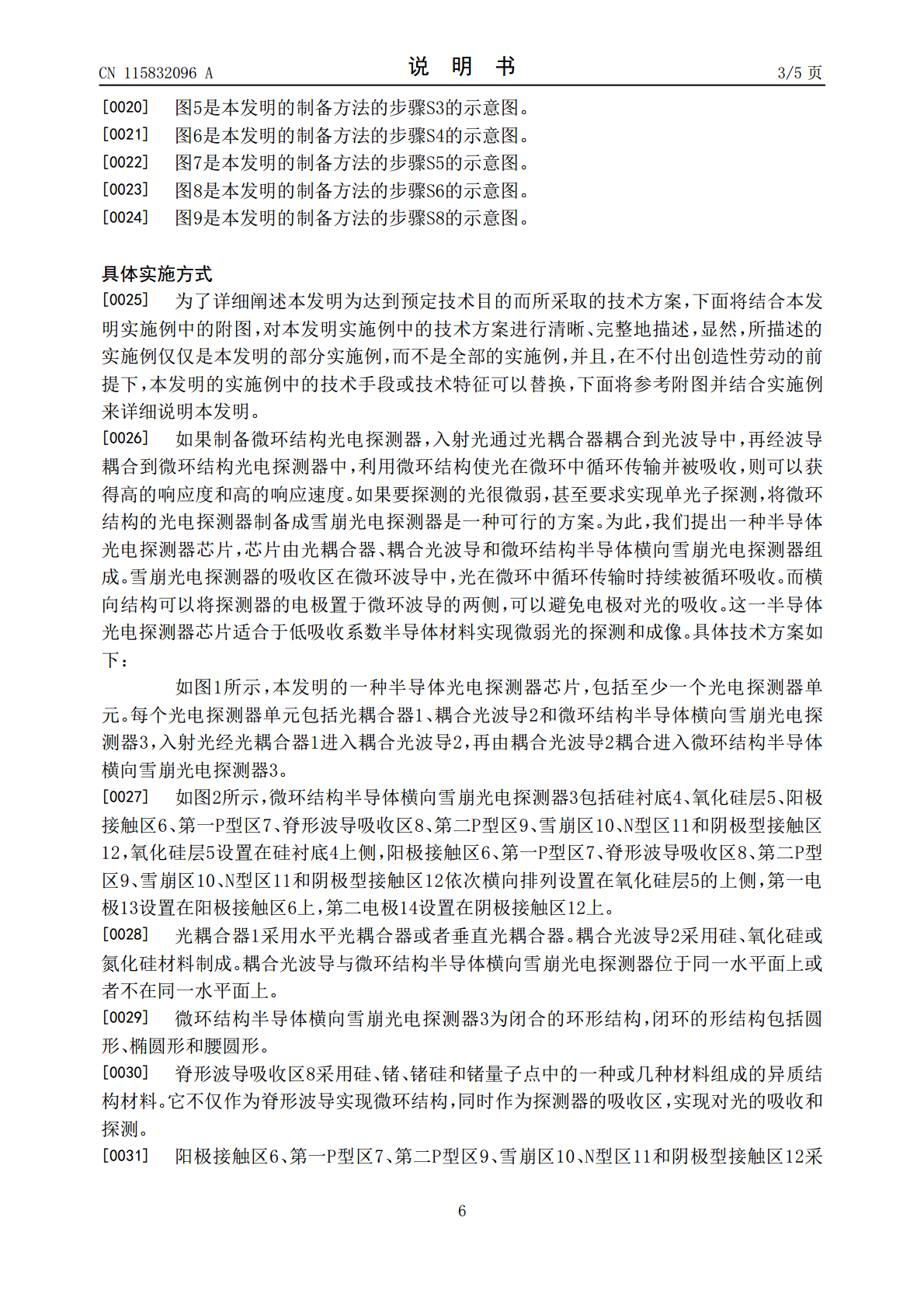

本发明公开了一种半导体光电探测器芯片及其制备方法,包括至少一个光电探测器单元,每个光电探测器单元包括光耦合器、耦合光波导和微环结构半导体横向雪崩光电探测器,微环结构半导体横向雪崩光电探测器包括硅衬底、氧化硅层、阳极接触区、第一P型区、脊形波导吸收区、第二P型区、雪崩区、N型区和阴极型接触区。本发明适合于在吸收系数很低的情况下对微弱光信号的探测和成像,并且采用微环结构不增加器件的尺寸,解决了现有技术在微弱光信号下的探测率低和工作速度低的问题。

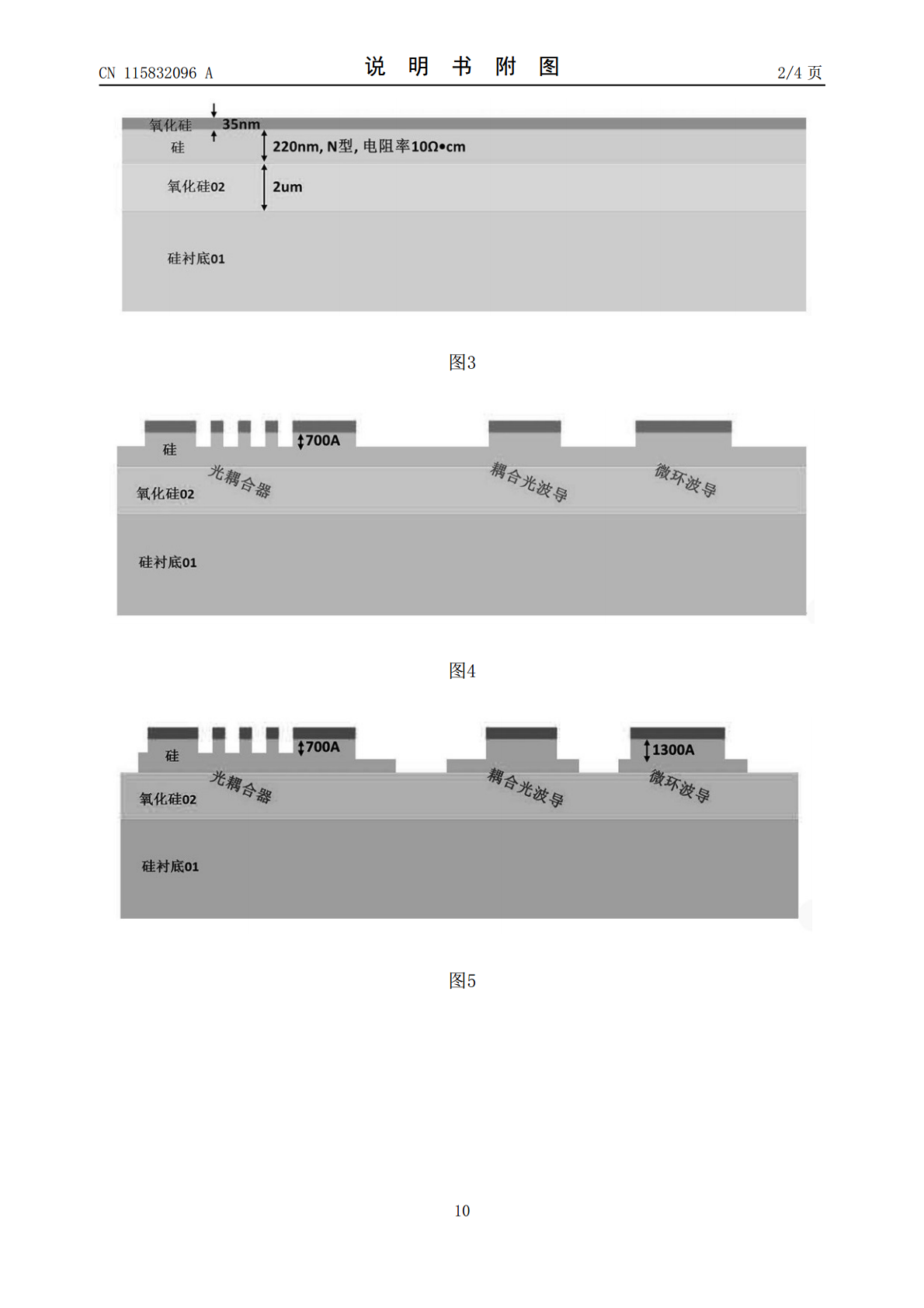

一种半导体紫外探测器芯片的外延结构及其制备方法、半导体紫外探测器芯片.pdf

本发明涉及紫外探测器技术领域,尤其涉及一种半导体紫外探测器芯片的外延结构及其制备方法、半导体紫外探测器芯片。本发明通过交替生长的超晶格层的设置实现了对半导体缓冲层的位错线的有效阻挡,极大的降低了整个缓冲层的位错密度,解决了由于位错密度偏大导致器件暗电流大的问题;在P型传输层和P型接触层之间引入应变超晶格层,此层的引入能够使结构产生应变,能带发生弯曲,电子空穴隧穿迁移效果明显提升,提高了量子效率,提高了紫外响应度;应变超晶格层的引入能够有效阻止底层材料位错线的延伸,如此能够极大的降低器件的暗电流,从而提升紫

一种ESD半导体芯片及其制备方法.pdf

(19)国家知识产权局(12)发明专利申请(10)申请公布号CN116031286A(43)申请公布日2023.04.28(21)申请号202310295236.1(22)申请日2023.03.24(71)申请人江西萨瑞微电子技术有限公司地址330000江西省南昌市赣江新区直管区儒乐湖399号四楼409室(72)发明人宋锐李运鹏段洪(74)专利代理机构南昌旭瑞知识产权代理事务所(普通合伙)36150专利代理师曹远龙(51)Int.Cl.H01L29/06(2006.01)H01L29/861(2006.0

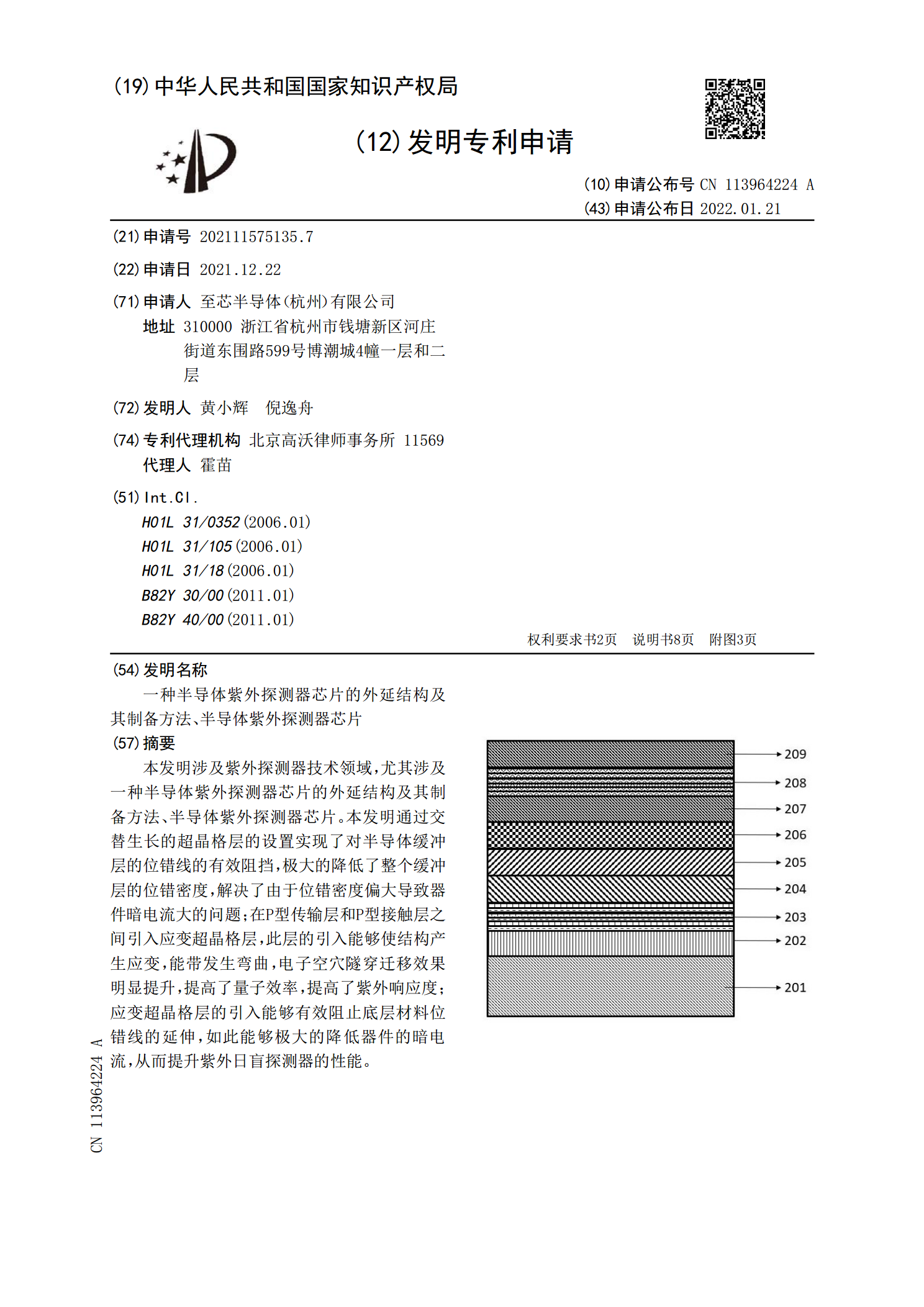

光电探测器及其制备方法.pdf

本申请公开了光电探测器及其制备方法,其中,光电探测器包括:氧化硅片,具有硅基衬底以及位于硅基衬底上方的二氧化硅层,所述二氧化硅层上具有硅窗口;In2Se3层,位于所述二氧化硅层的上方,覆盖所述硅窗口,In2Se3层与硅窗口相对应的部分处于悬浮状态;WSe2层,位于所述In2Se3层的上方,与所述硅窗口相对应;两个电极,位于所述WSe2层的上方,两个电极分别位于硅窗口的两侧。本申请采用应变工程,通过将In2Se3层悬浮,避免了与氧化硅片接触,这种结构形式可以大大降低现有技术因为衬底的不利影响导致器件性能受限

光电探测器及其制备方法.pdf

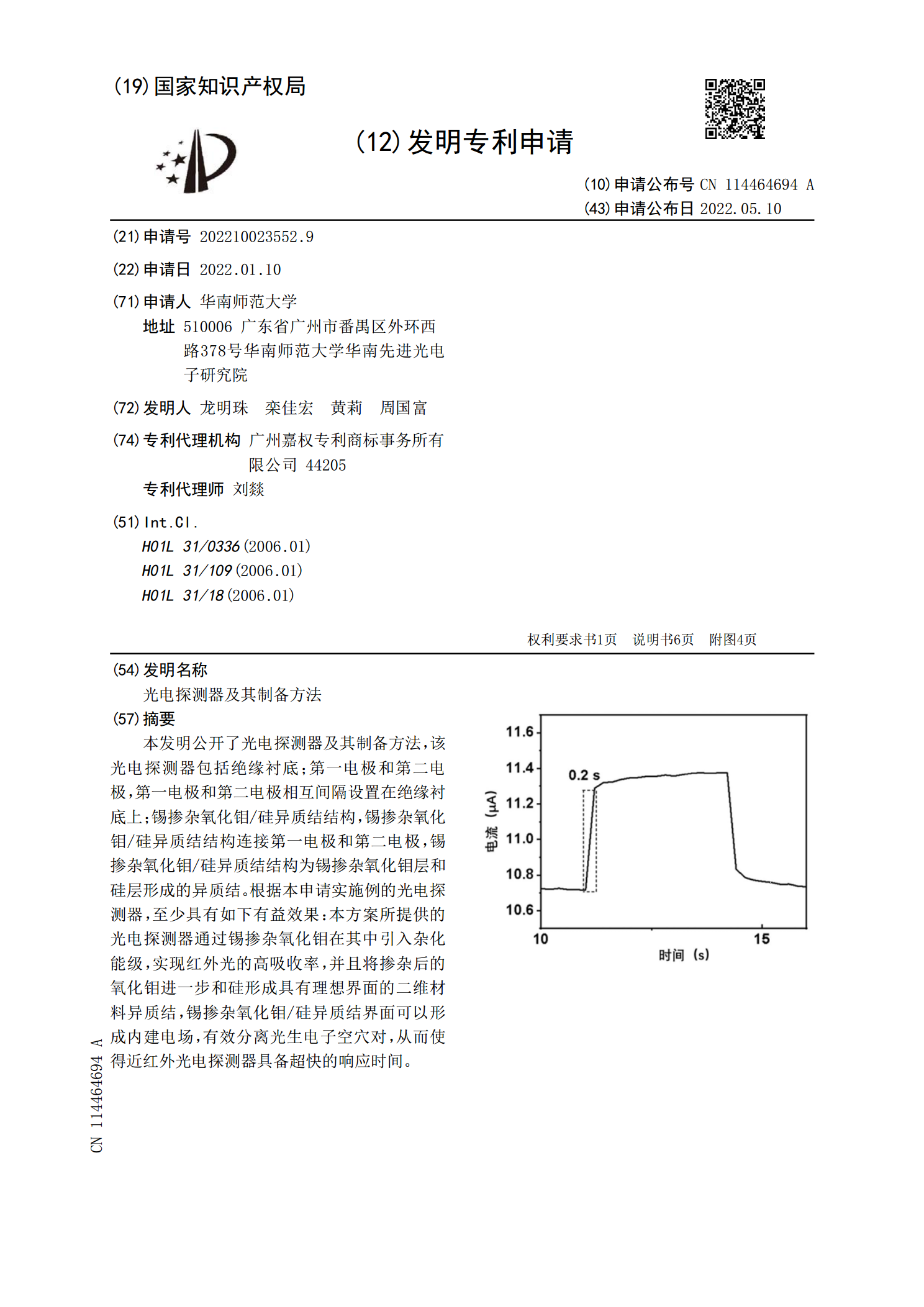

本发明公开了光电探测器及其制备方法,该光电探测器包括绝缘衬底;第一电极和第二电极,第一电极和第二电极相互间隔设置在绝缘衬底上;锡掺杂氧化钼/硅异质结结构,锡掺杂氧化钼/硅异质结结构连接第一电极和第二电极,锡掺杂氧化钼/硅异质结结构为锡掺杂氧化钼层和硅层形成的异质结。根据本申请实施例的光电探测器,至少具有如下有益效果:本方案所提供的光电探测器通过锡掺杂氧化钼在其中引入杂化能级,实现红外光的高吸收率,并且将掺杂后的氧化钼进一步和硅形成具有理想界面的二维材料异质结,锡掺杂氧化钼/硅异质结界面可以形成内建电场,有