驱动电路、相关控制方法、同步升压电路及电子设备.pdf

一只****呀淑

亲,该文档总共12页,到这已经超出免费预览范围,如果喜欢就直接下载吧~

相关资料

驱动电路、相关控制方法、同步升压电路及电子设备.pdf

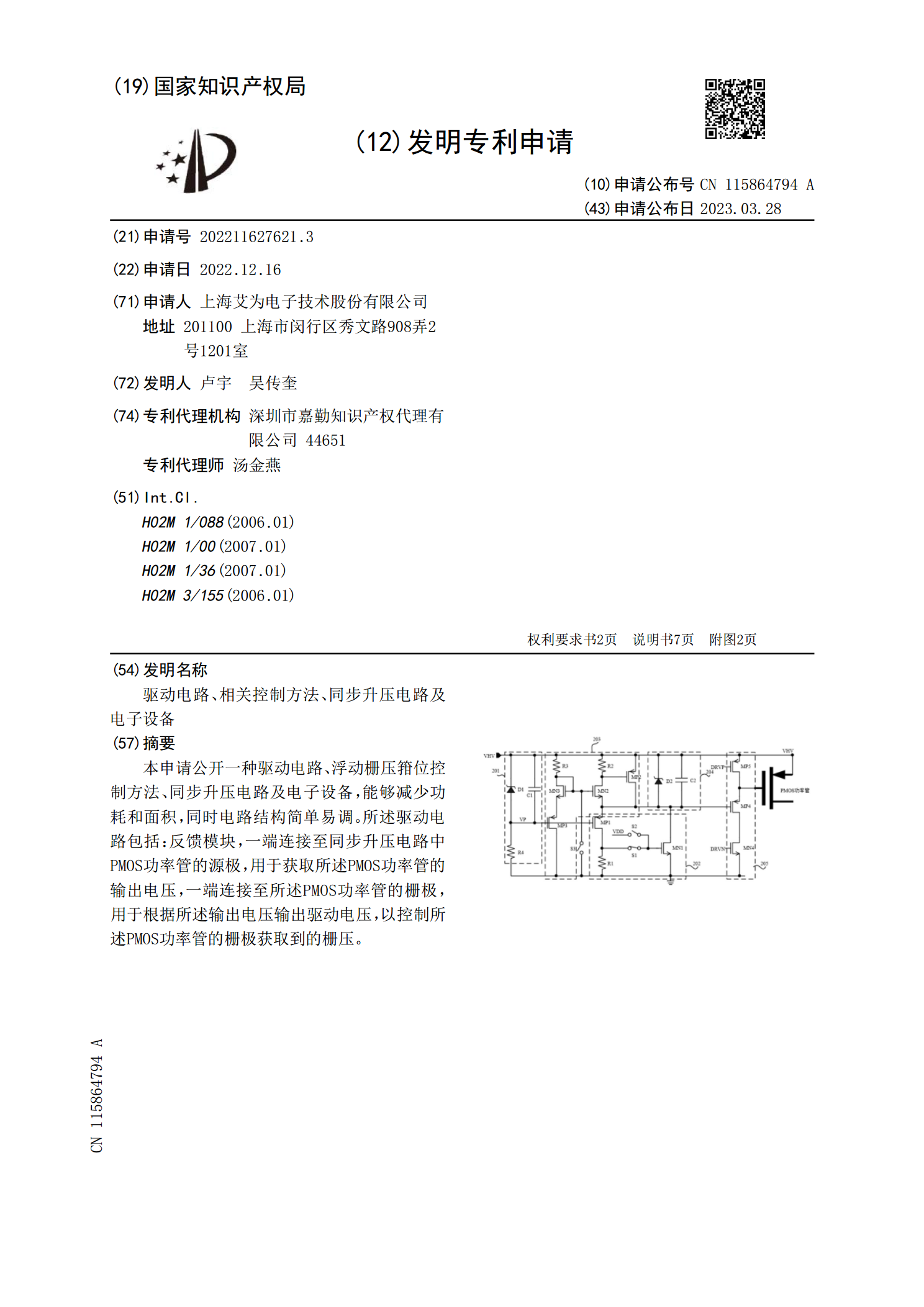

本申请公开一种驱动电路、浮动栅压箝位控制方法、同步升压电路及电子设备,能够减少功耗和面积,同时电路结构简单易调。所述驱动电路包括:反馈模块,一端连接至同步升压电路中PMOS功率管的源极,用于获取所述PMOS功率管的输出电压,一端连接至所述PMOS功率管的栅极,用于根据所述输出电压输出驱动电压,以控制所述PMOS功率管的栅极获取到的栅压。

升压转换器电路与升压转换器电路控制方法.pdf

一种与升压转换器电路控制方法。该升压转换器控制方法用以控制一升压转换器,其中升压转换器根据一输入电压产生一输出电压,升压转换器包括一电感、耦接于电感与一接地点之间的一第一晶体管、耦接在电感与一输出端之间的一第二晶体管、以及耦接至第二晶体管与输出端的一电容。此升压转换器控制方法包括:在一第一时间区间持续导通第二晶体管,用以充电电容;在一第二时间区间根据一第一切换频率轮流导通第一晶体管与第二晶体管;以及在一第三时间区间根据一第二切换频率轮流导通第一晶体管与第二晶体管,其中该第一切换频率小于该第二切换频率。

综合布线系统升压驱动电路.pdf

综合布线系统升压驱动电路,包括依次连接的输入端、电感、功率管;所述功率NMOS管和地之间连接有负载,所述负载和功率管的公共端作为反馈电压采样端,所述反馈电压采样端和功率管的控制端之间连接有反馈控制环路;所述反馈控制环路由采样电路、误差放大器、PWM比较器、电流比较器、逻辑驱动电路、基准电压和电平位移电路组成;所述电平位移电路为高电平位移电路,输出信号的正电源端与电感和功率管的公共端连接;还包括连接在反馈电压采样端和地之间的储能电容。采用本发明所述的综合布线系统升压驱动电路,将负载直接加在功率管源级,并实现

具有升压电路的电子设备.pdf

本发明的目的在于提供具有蓄电电容的个数较少的升压电路或使用了电容值较小的小型蓄电电容的升压电路的电子设备。具有升压电路的电子设备(100)具备第1升压电路(103)、第1输出电路(105)、负载(106)、第1蓄电电容(102)、第2蓄电电容(104)以及输入端子(107),输入端子(107)与第1蓄电电容(102)和第1升压电路(103)连接,第2蓄电电容(104)与第1升压电路(103)和第1输出电路(105)连接,负载(106)与第1输出电路(105)连接。

直流-直流升压转换器电路及其驱动方法.pdf

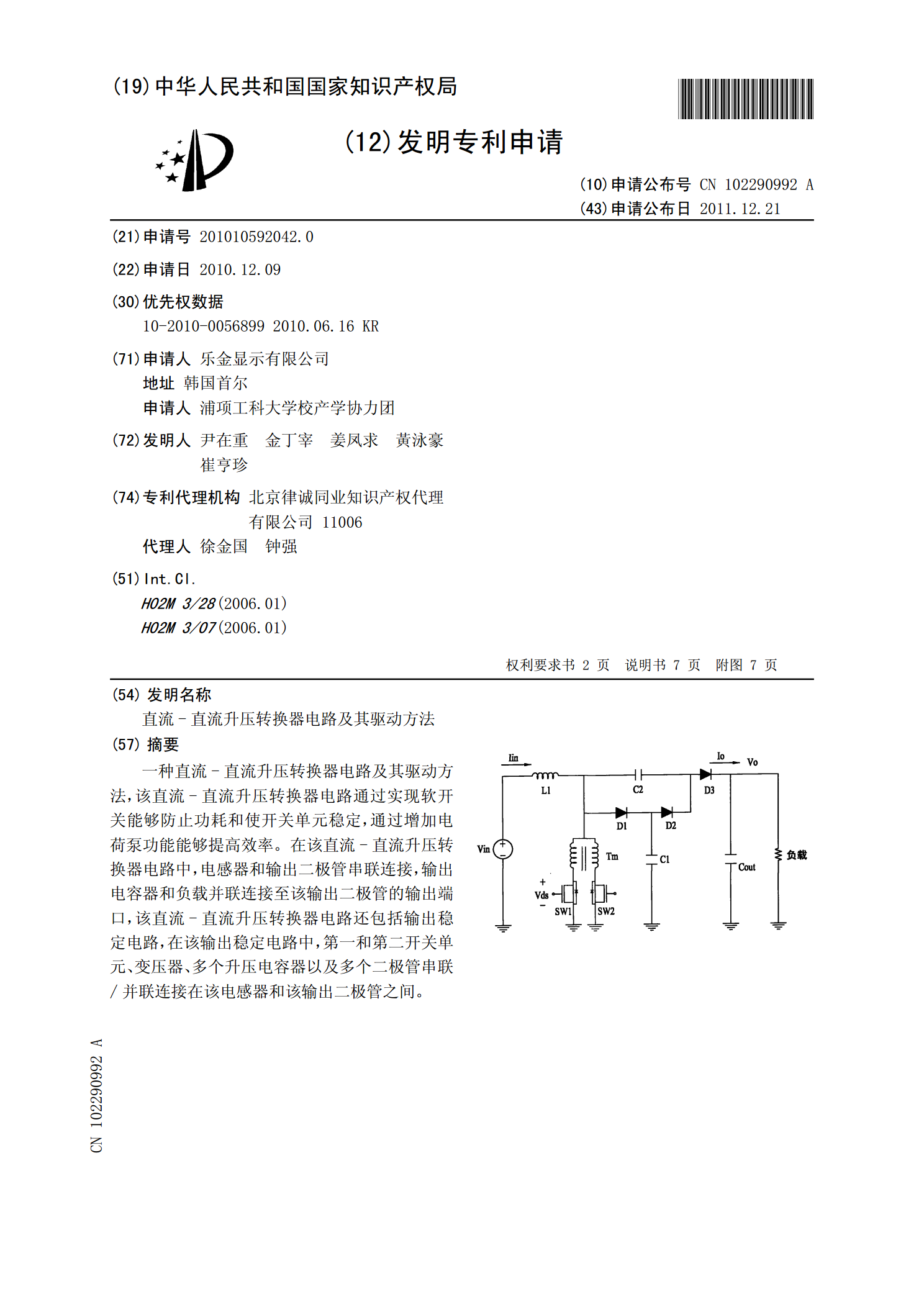

一种直流-直流升压转换器电路及其驱动方法,该直流-直流升压转换器电路通过实现软开关能够防止功耗和使开关单元稳定,通过增加电荷泵功能能够提高效率。在该直流-直流升压转换器电路中,电感器和输出二极管串联连接,输出电容器和负载并联连接至该输出二极管的输出端口,该直流-直流升压转换器电路还包括输出稳定电路,在该输出稳定电路中,第一和第二开关单元、变压器、多个升压电容器以及多个二极管串联/并联连接在该电感器和该输出二极管之间。