基于嵌入式高速收发器的校准逻辑系统.pdf

曾琪****是我

在线预览结束,喜欢就下载吧,查找使用更方便

相关资料

基于嵌入式高速收发器的校准逻辑系统.pdf

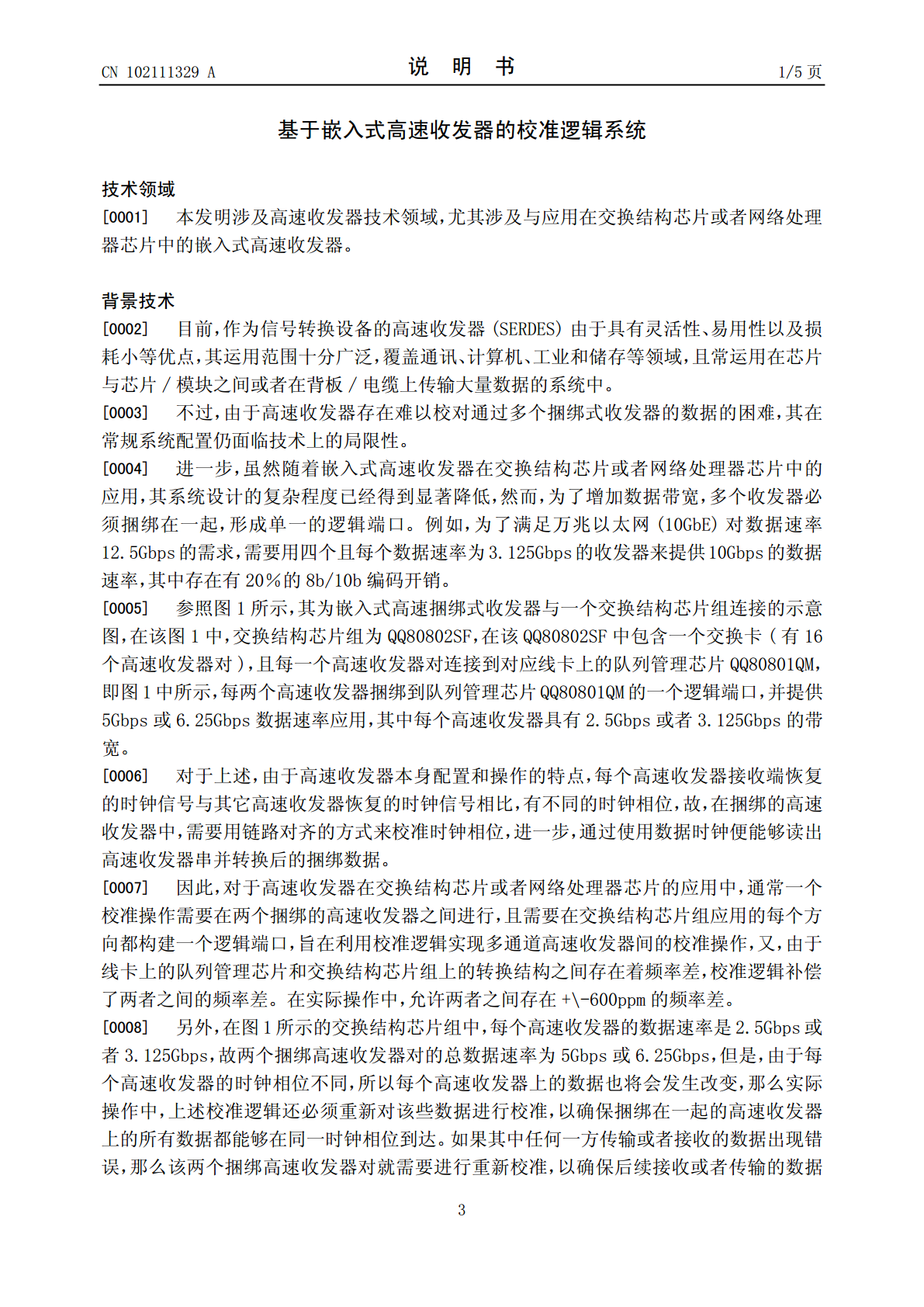

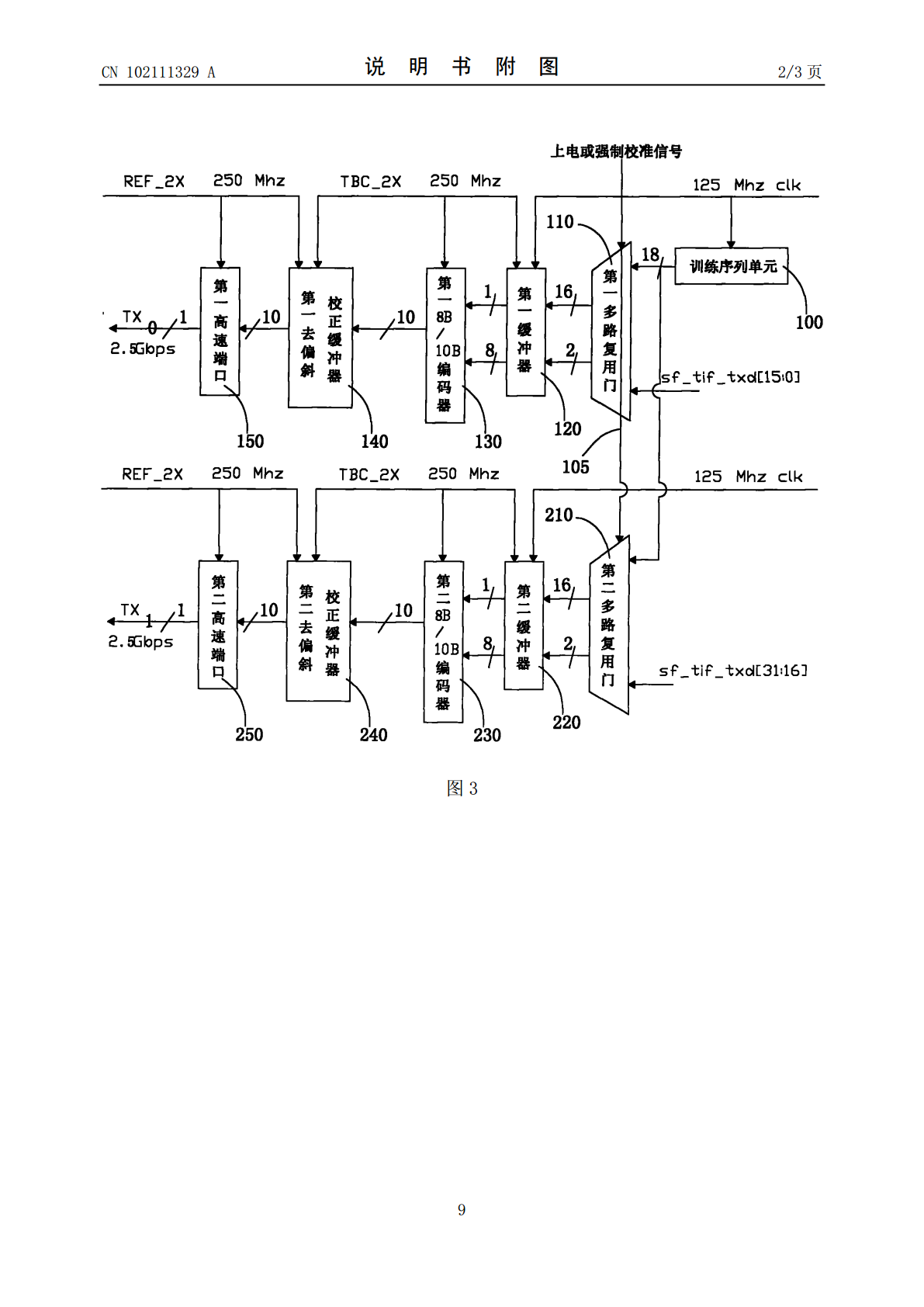

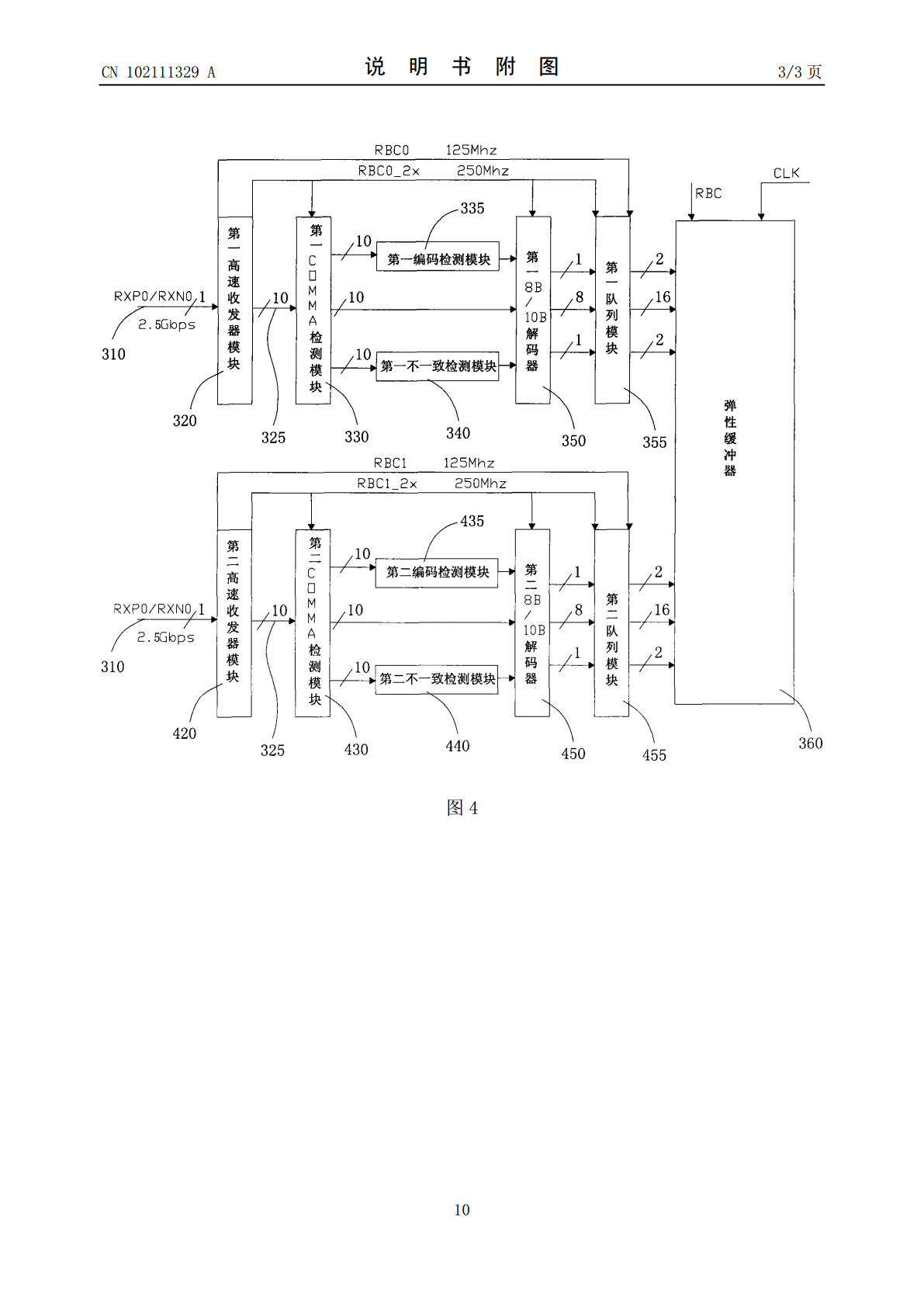

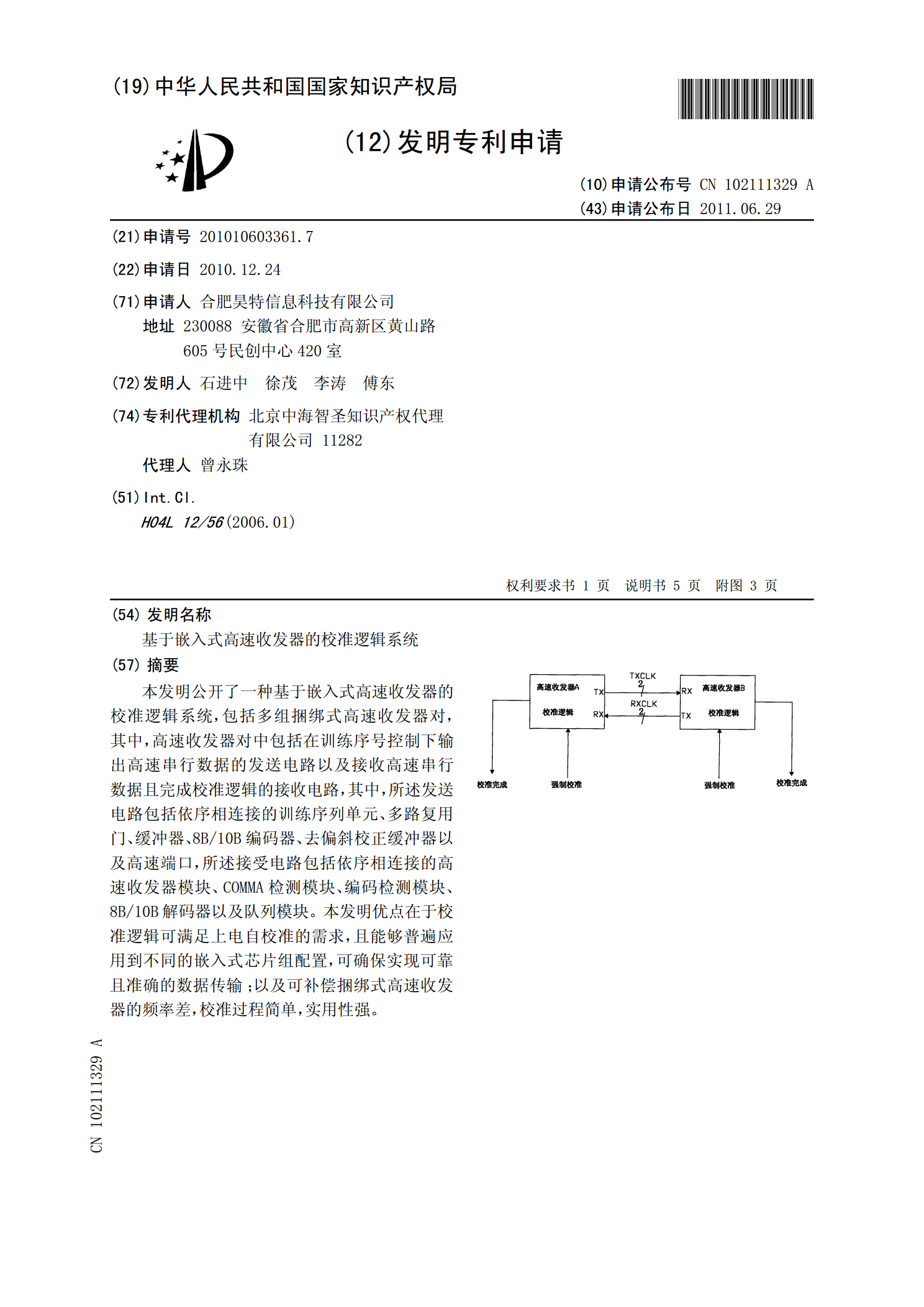

本发明公开了一种基于嵌入式高速收发器的校准逻辑系统,包括多组捆绑式高速收发器对,其中,高速收发器对中包括在训练序号控制下输出高速串行数据的发送电路以及接收高速串行数据且完成校准逻辑的接收电路,其中,所述发送电路包括依序相连接的训练序列单元、多路复用门、缓冲器、8B/10B编码器、去偏斜校正缓冲器以及高速端口,所述接受电路包括依序相连接的高速收发器模块、COMMA检测模块、编码检测模块、8B/10B解码器以及队列模块。本发明优点在于校准逻辑可满足上电自校准的需求,且能够普遍应用到不同的嵌入式芯片组配置,可确

基于延迟线的收发器校准.pdf

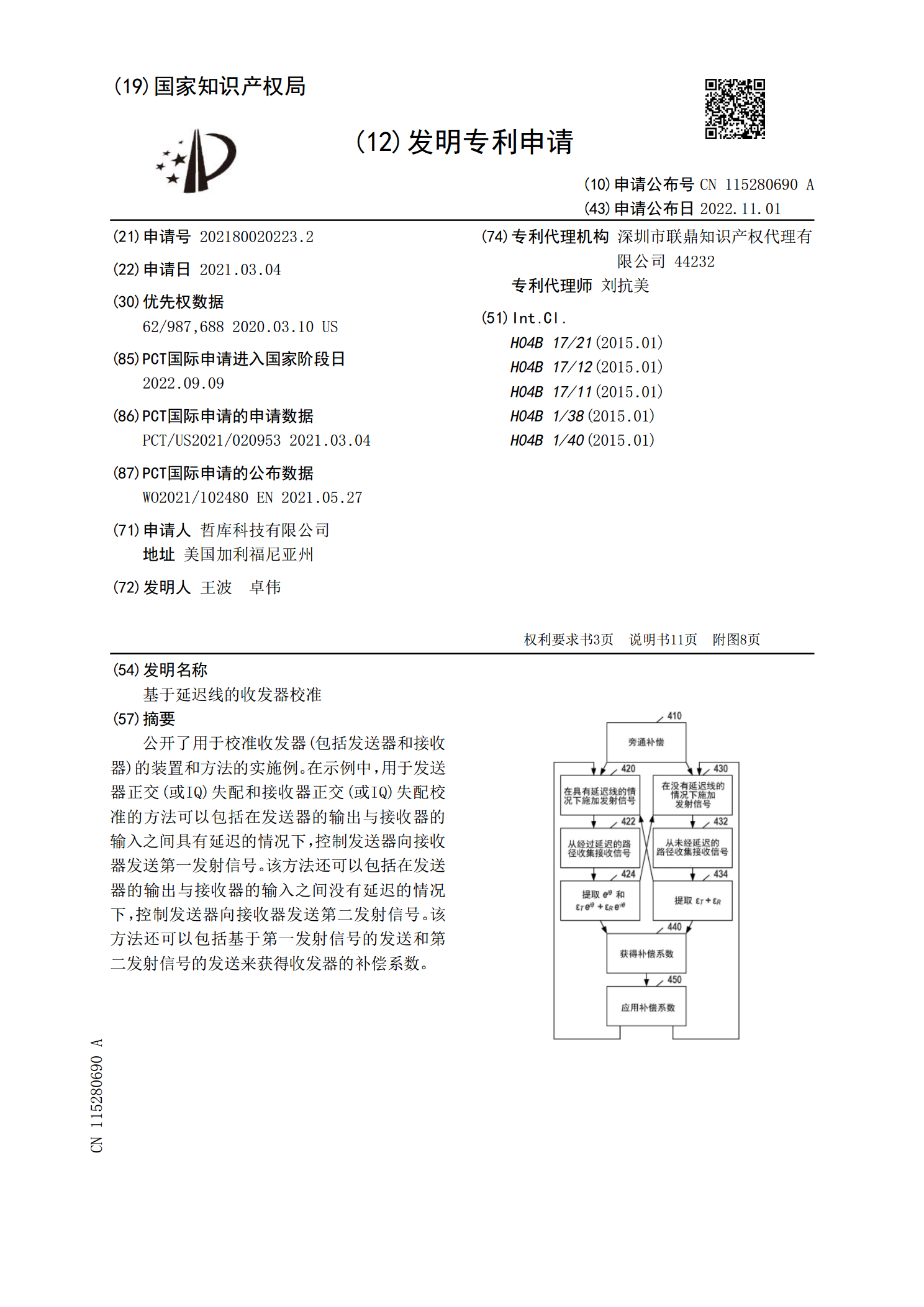

公开了用于校准收发器(包括发送器和接收器)的装置和方法的实施例。在示例中,用于发送器正交(或IQ)失配和接收器正交(或IQ)失配校准的方法可以包括在发送器的输出与接收器的输入之间具有延迟的情况下,控制发送器向接收器发送第一发射信号。该方法还可以包括在发送器的输出与接收器的输入之间没有延迟的情况下,控制发送器向接收器发送第二发射信号。该方法还可以包括基于第一发射信号的发送和第二发射信号的发送来获得收发器的补偿系数。

收发器校准电路.pdf

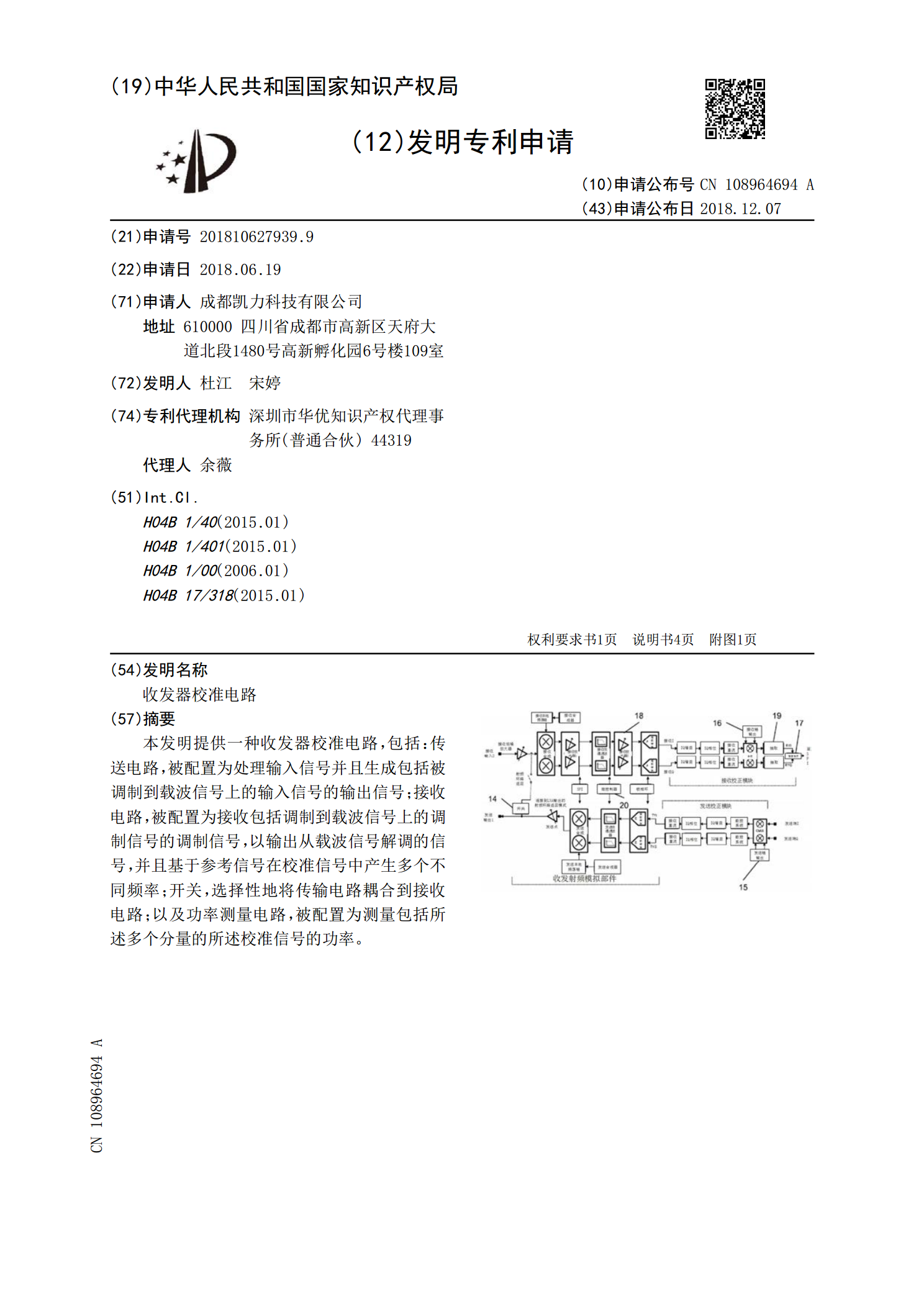

本发明提供一种收发器校准电路,包括:传送电路,被配置为处理输入信号并且生成包括被调制到载波信号上的输入信号的输出信号;接收电路,被配置为接收包括调制到载波信号上的调制信号的调制信号,以输出从载波信号解调的信号,并且基于参考信号在校准信号中产生多个不同频率;开关,选择性地将传输电路耦合到接收电路;以及功率测量电路,被配置为测量包括所述多个分量的所述校准信号的功率。

收发器和收发器校准方法.pdf

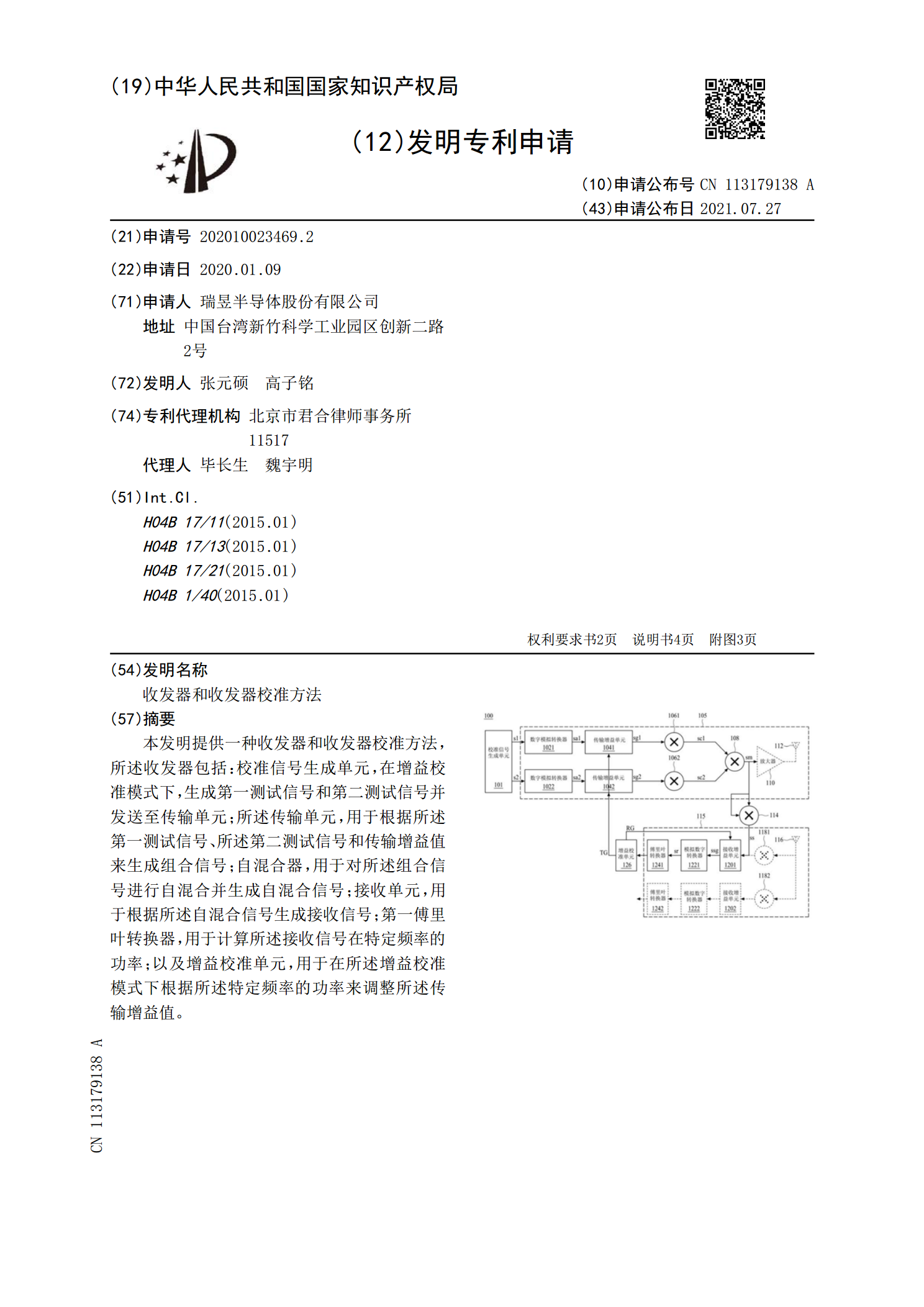

本发明提供一种收发器和收发器校准方法,所述收发器包括:校准信号生成单元,在增益校准模式下,生成第一测试信号和第二测试信号并发送至传输单元;所述传输单元,用于根据所述第一测试信号、所述第二测试信号和传输增益值来生成组合信号;自混合器,用于对所述组合信号进行自混合并生成自混合信号;接收单元,用于根据所述自混合信号生成接收信号;第一傅里叶转换器,用于计算所述接收信号在特定频率的功率;以及增益校准单元,用于在所述增益校准模式下根据所述特定频率的功率来调整所述传输增益值。

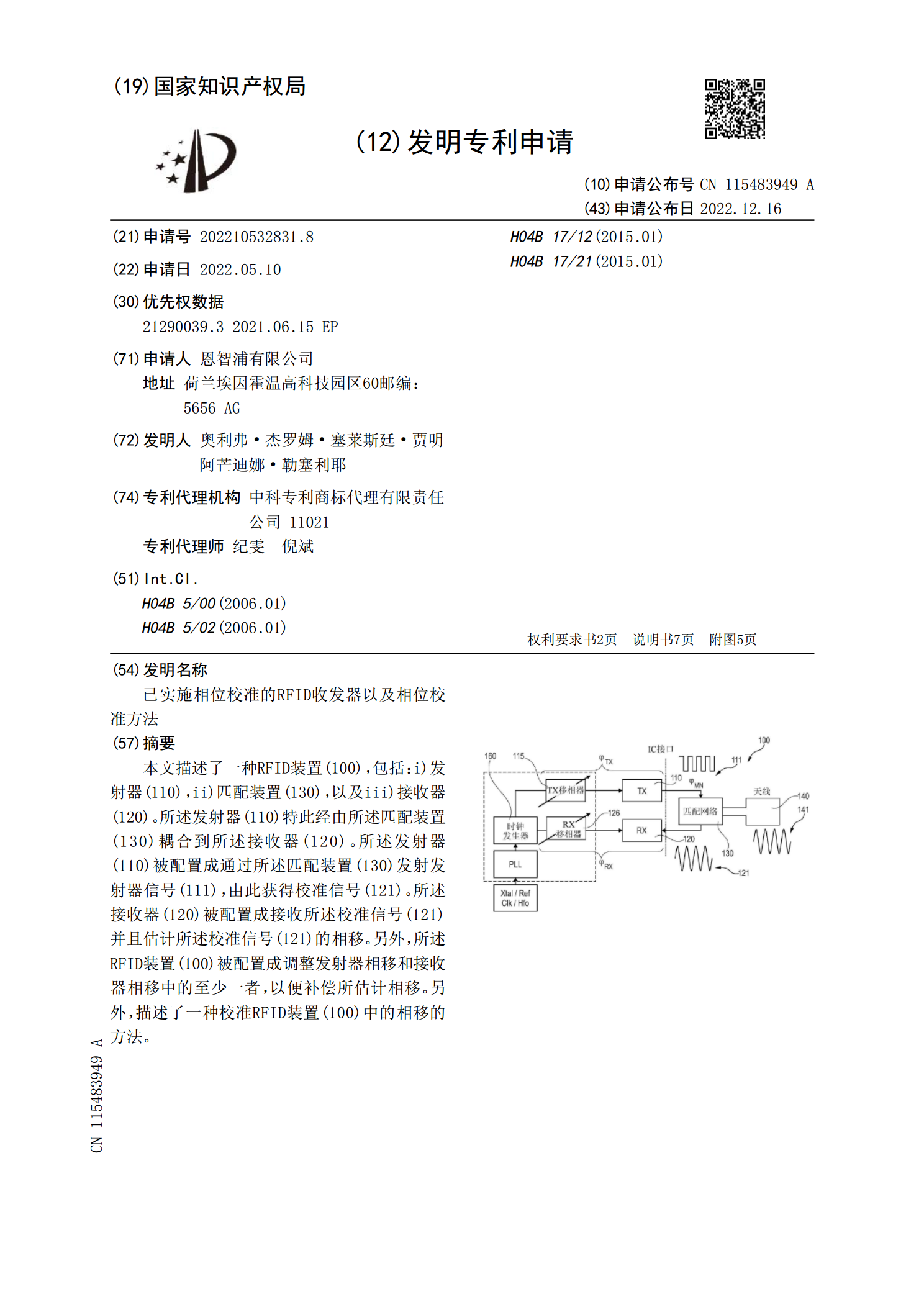

已实施相位校准的RFID收发器以及相位校准方法.pdf

本文描述了一种RFID装置(100),包括:i)发射器(110),ii)匹配装置(130),以及iii)接收器(120)。所述发射器(110)特此经由所述匹配装置(130)耦合到所述接收器(120)。所述发射器(110)被配置成通过所述匹配装置(130)发射发射器信号(111),由此获得校准信号(121)。所述接收器(120)被配置成接收所述校准信号(121)并且估计所述校准信号(121)的相移。另外,所述RFID装置(100)被配置成调整发射器相移和接收器相移中的至少一者,以便补偿所估计相移。另外,描述