一种高压隔离智能功率电路.pdf

论文****酱吖

亲,该文档总共12页,到这已经超出免费预览范围,如果喜欢就直接下载吧~

相关资料

一种高压隔离智能功率电路.pdf

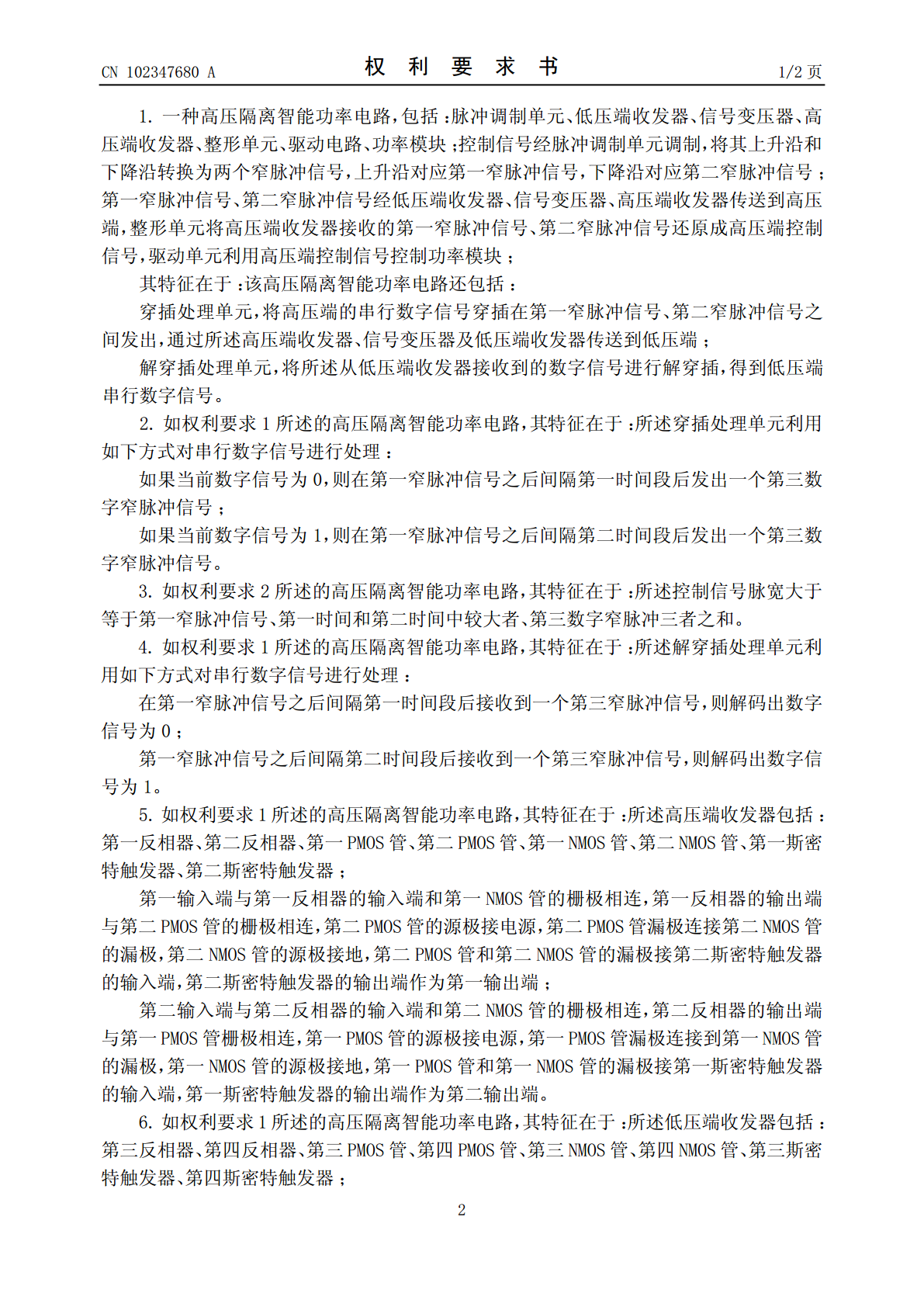

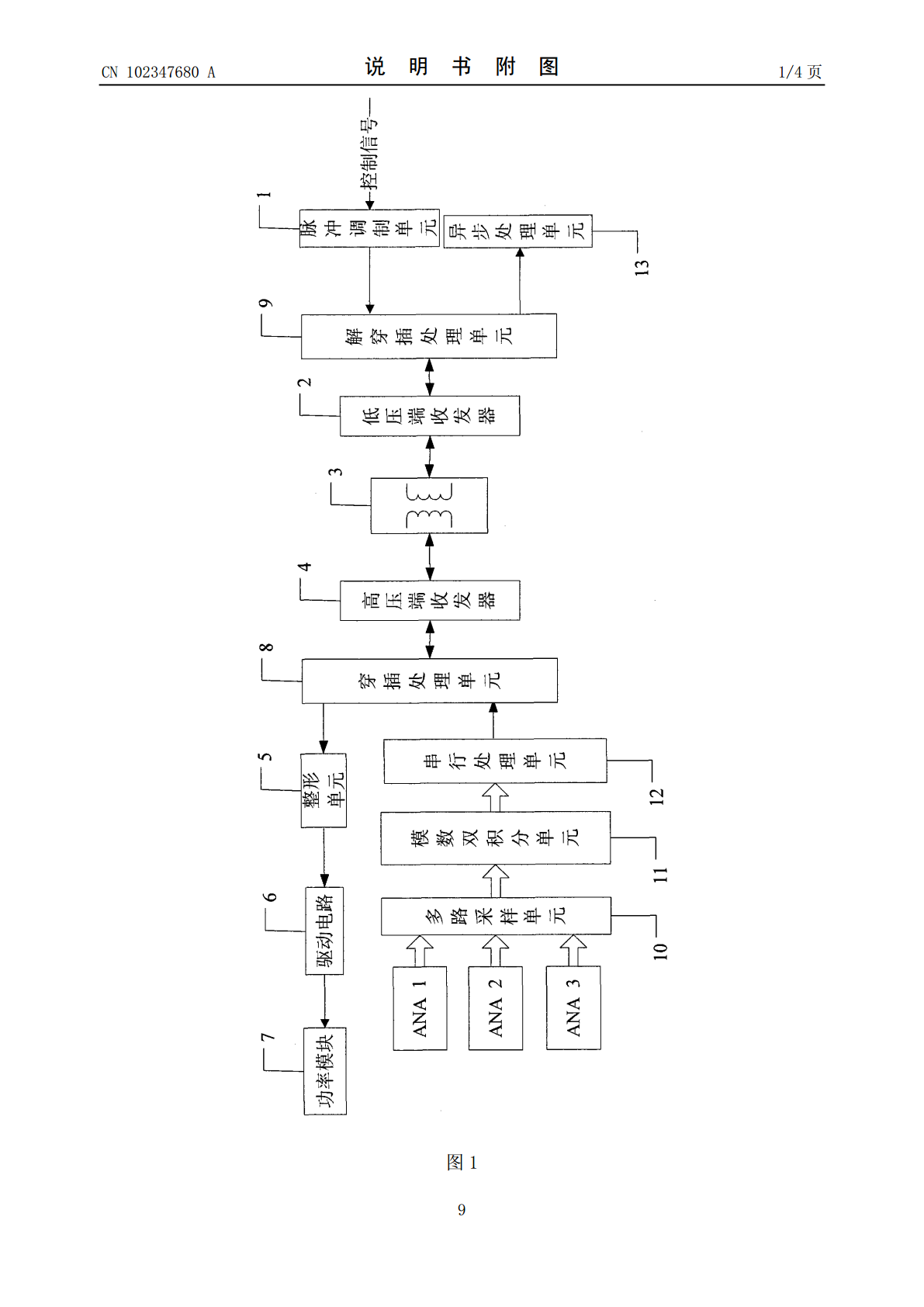

一种高压智能功率电路,包括:脉冲调制单元、低压端收发器、信号变压器、高压端收发器、整形单元、驱动电路、功率模块;控制信号经脉冲调制单元调制,调制后的控制信号经低压端收发器、信号变压器、高压端收发器传送到高压端,整形单元将高压端收发器接收的控制信号整形还原,驱动单元利用高压端控制信号控制功率模块;该电路还包括:穿插处理单元,将高压端的串行数字信号穿插在调制后的控制信号之间发出,通过高压端收发器、信号变压器及低压端收发器传送到低压端;解穿插处理单元,将所述从低压端收发器接收到的数字信号进行解穿插得到串行数字信

智能功率模块及其高压驱动电路.pdf

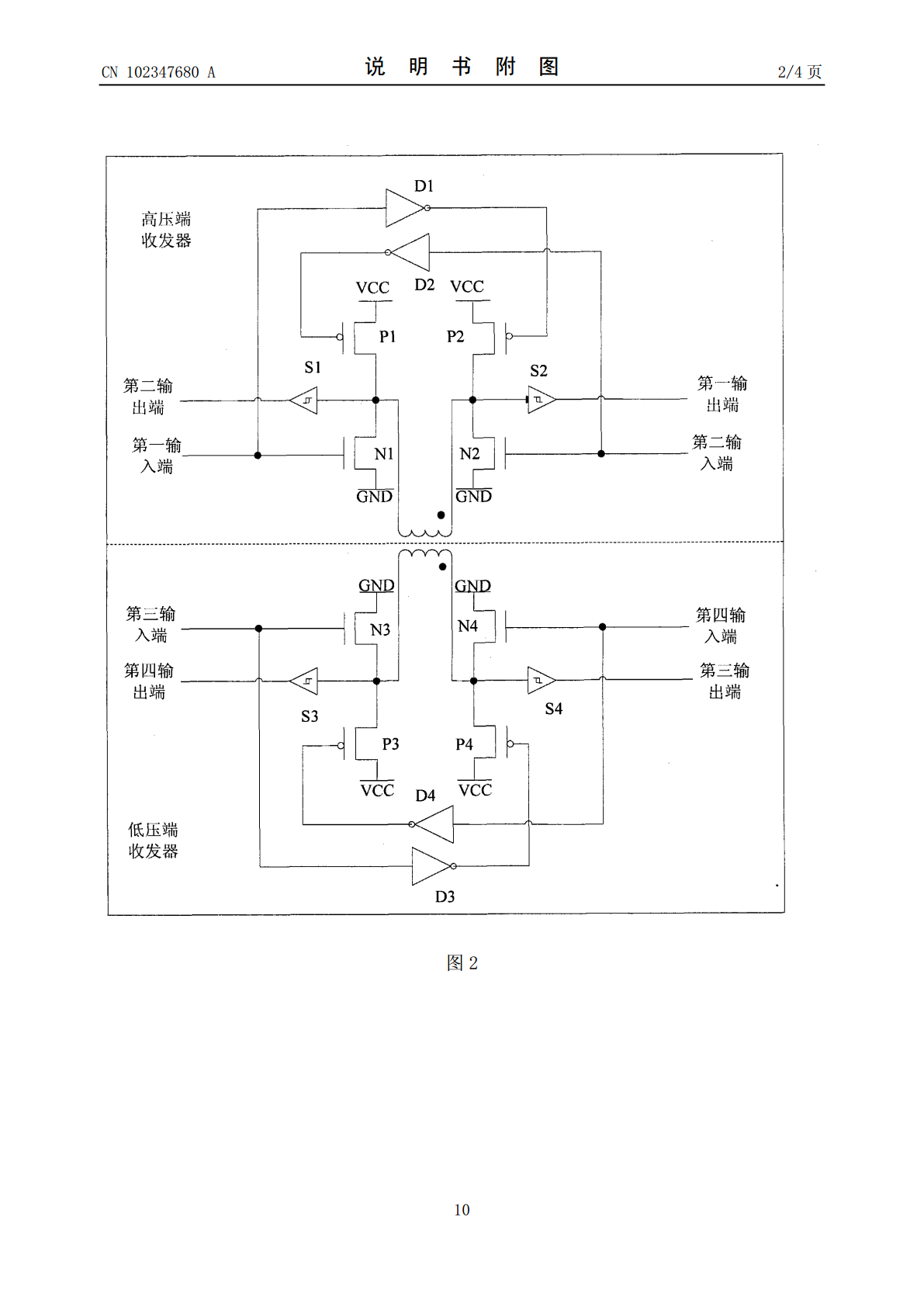

本发明公开了一种智能功率模块及其高压驱动电路,所述驱动电路包括第一至第六驱动电路和第一至第六充放电电路,每个充放电电路包括第一信号输入端、第一信号输出端、供电电源正端和供电电源负端,供电电源正端对应与智能功率模块的高压区供电电源正端/低压区供电电源正端相连,供电电源负端对应与智能功率模块的高压区供电电源负端/低压区供电电源负端相连,其中,当低压区供电电源/高压区供电电源异常时,充放电电路停止将对应的驱动电路输出的驱动信号输出至对应的功率开关管的控制端,并控制第一信号输出端处于低阻状态,以对负载侧的剩余电荷

一种高压大功率压电陶瓷驱动电路.pdf

本发明公开了一种高压大功率压电陶瓷驱动电路,由运算放大器A<base:Sub>1</base:Sub>,电阻R<base:Sub>1</base:Sub>~R<base:Sub>13</base:Sub>,电容C<base:Sub>1</base:Sub>~C<base:Sub>3</base:Sub>以及MOS管Q<base:Sub>1</base:Sub>~Q<base:Sub>4</base:Sub>组成;运算放大器A<base:Sub>1</base:Sub>的输出通过电阻连接到运算放大器A<ba

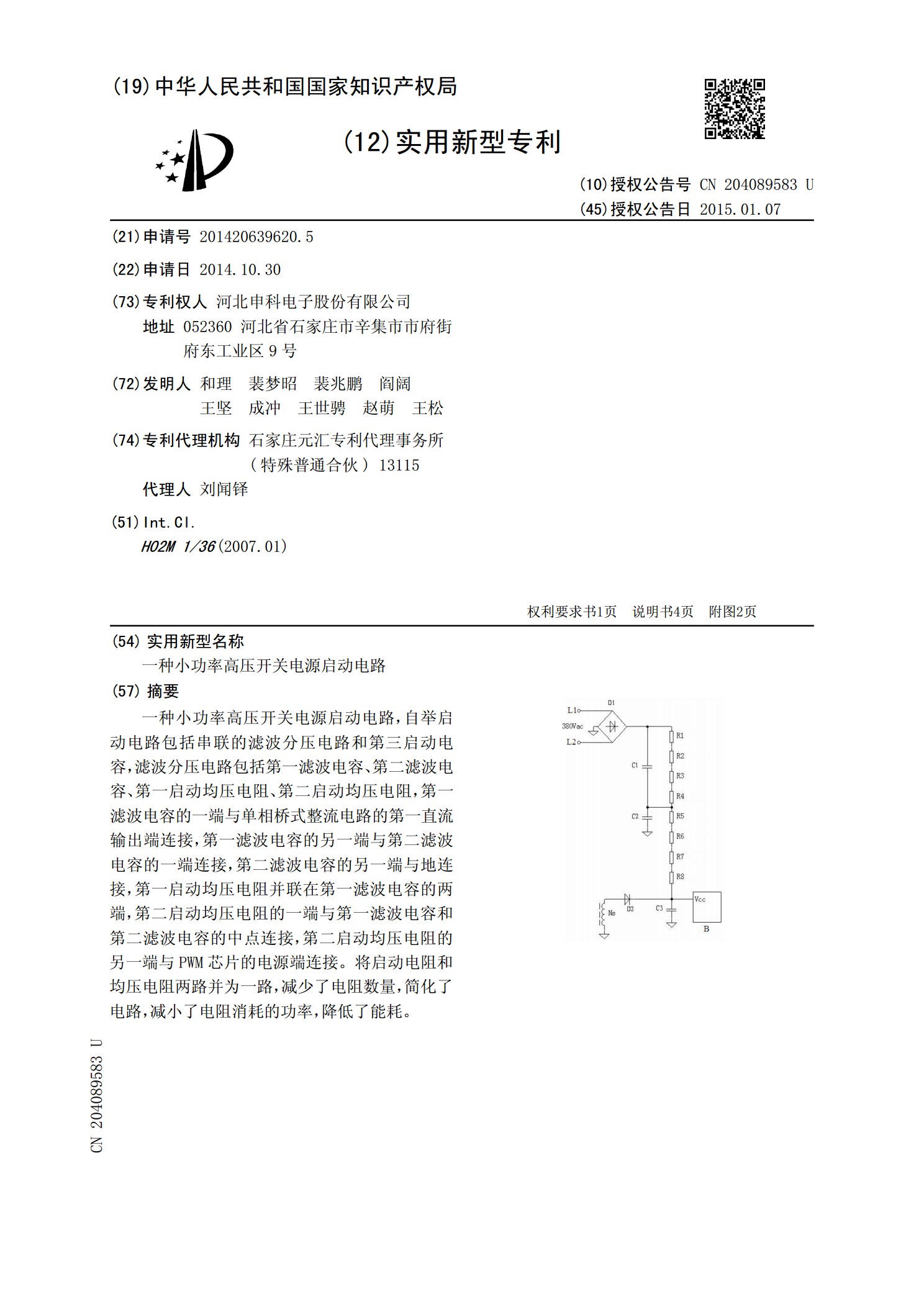

一种小功率高压开关电源启动电路.pdf

一种小功率高压开关电源启动电路,自举启动电路包括串联的滤波分压电路和第三启动电容,滤波分压电路包括第一滤波电容、第二滤波电容、第一启动均压电阻、第二启动均压电阻,第一滤波电容的一端与单相桥式整流电路的第一直流输出端连接,第一滤波电容的另一端与第二滤波电容的一端连接,第二滤波电容的另一端与地连接,第一启动均压电阻并联在第一滤波电容的两端,第二启动均压电阻的一端与第一滤波电容和第二滤波电容的中点连接,第二启动均压电阻的另一端与PWM芯片的电源端连接。将启动电阻和均压电阻两路并为一路,减少了电阻数量,简化了电路

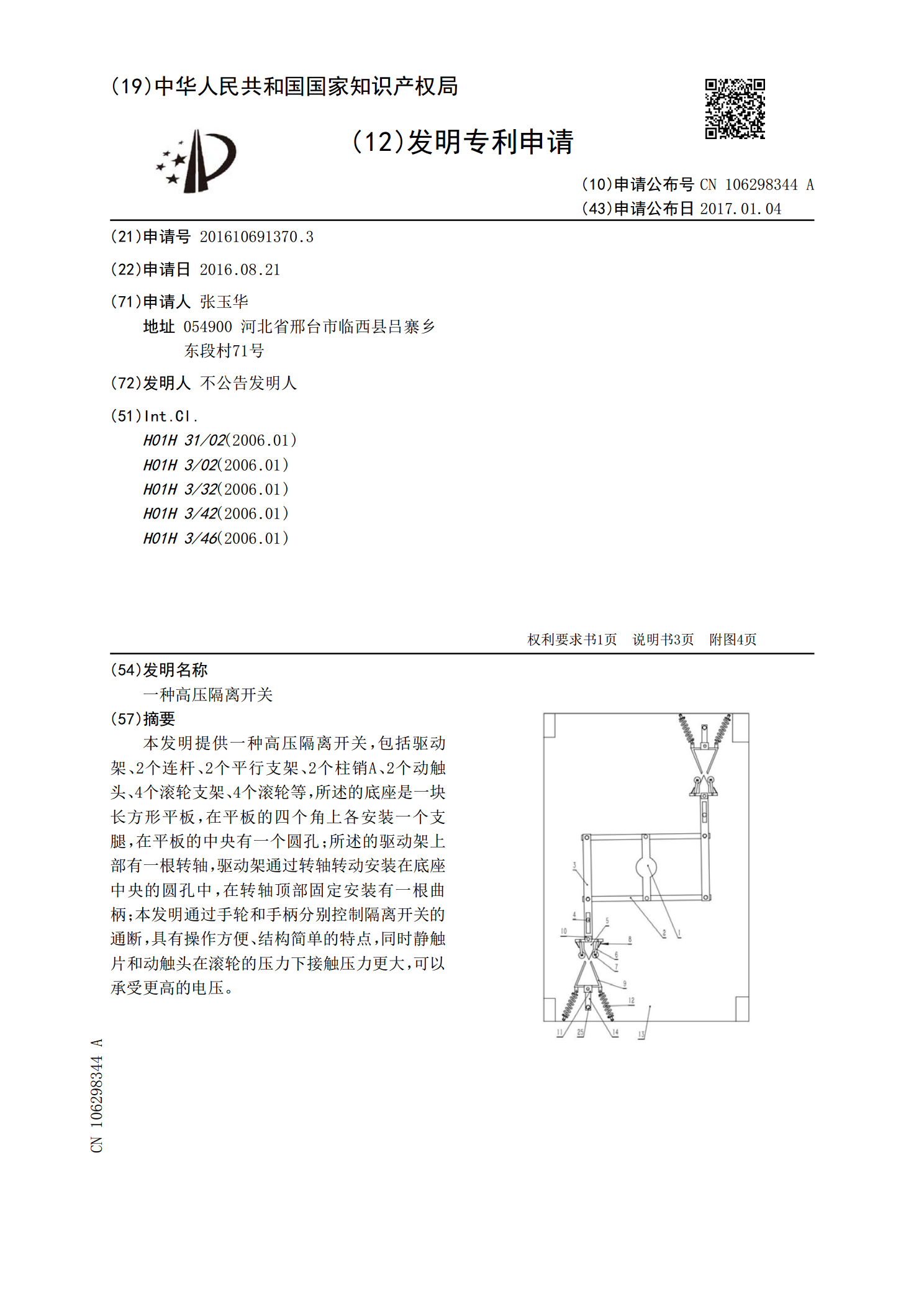

一种高压隔离开关.pdf

本发明提供一种高压隔离开关,包括驱动架、2个连杆、2个平行支架、2个柱销A、2个动触头、4个滚轮支架、4个滚轮等,所述的底座是一块长方形平板,在平板的四个角上各安装一个支腿,在平板的中央有一个圆孔;所述的驱动架上部有一根转轴,驱动架通过转轴转动安装在底座中央的圆孔中,在转轴顶部固定安装有一根曲柄;本发明通过手轮和手柄分别控制隔离开关的通断,具有操作方便、结构简单的特点,同时静触片和动触头在滚轮的压力下接触压力更大,可以承受更高的电压。