基于频域相关干涉仪的宽带测向控制方法.pdf

是你****盟主

亲,该文档总共16页,到这已经超出免费预览范围,如果喜欢就直接下载吧~

相关资料

基于频域相关干涉仪的宽带测向控制方法.pdf

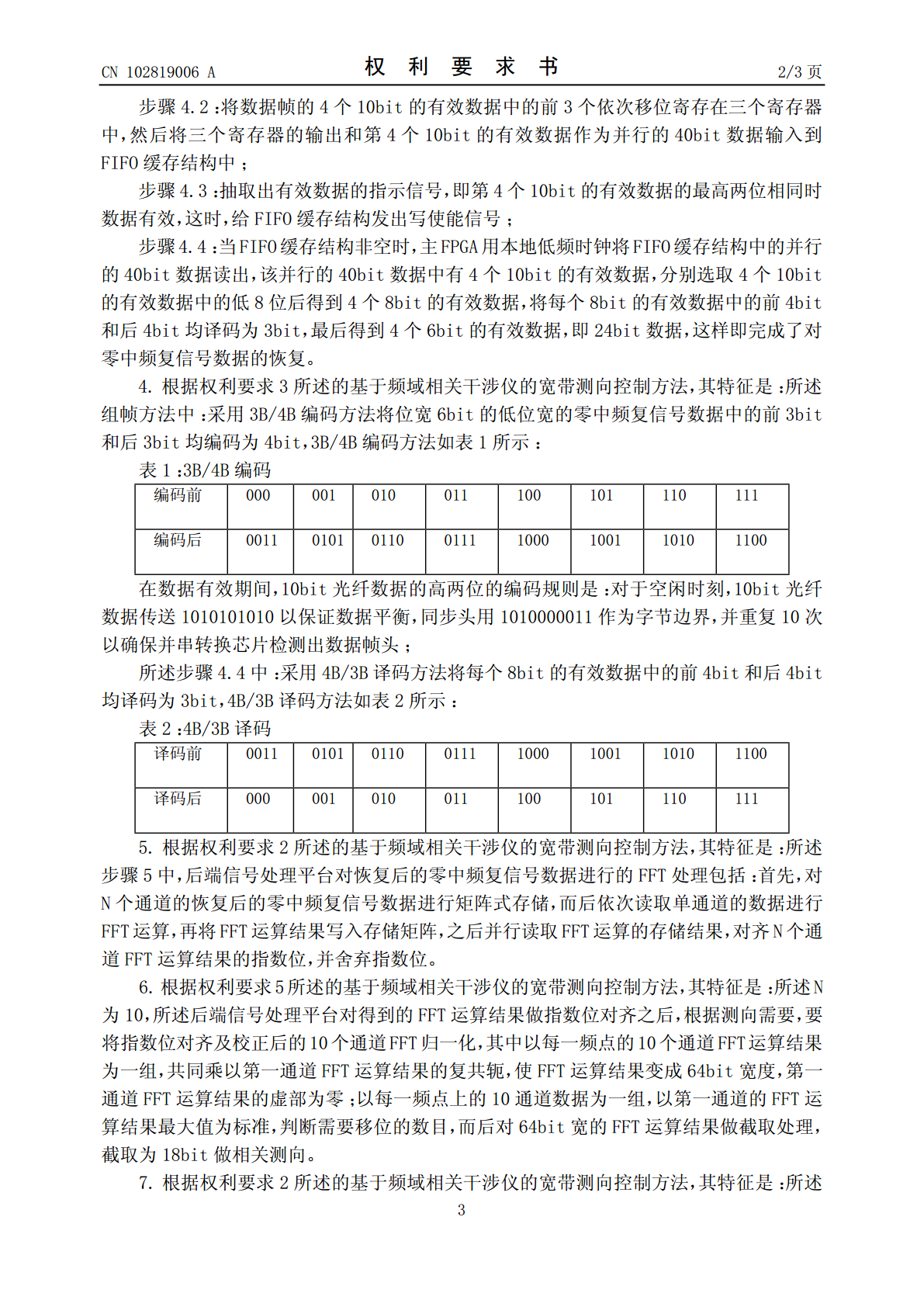

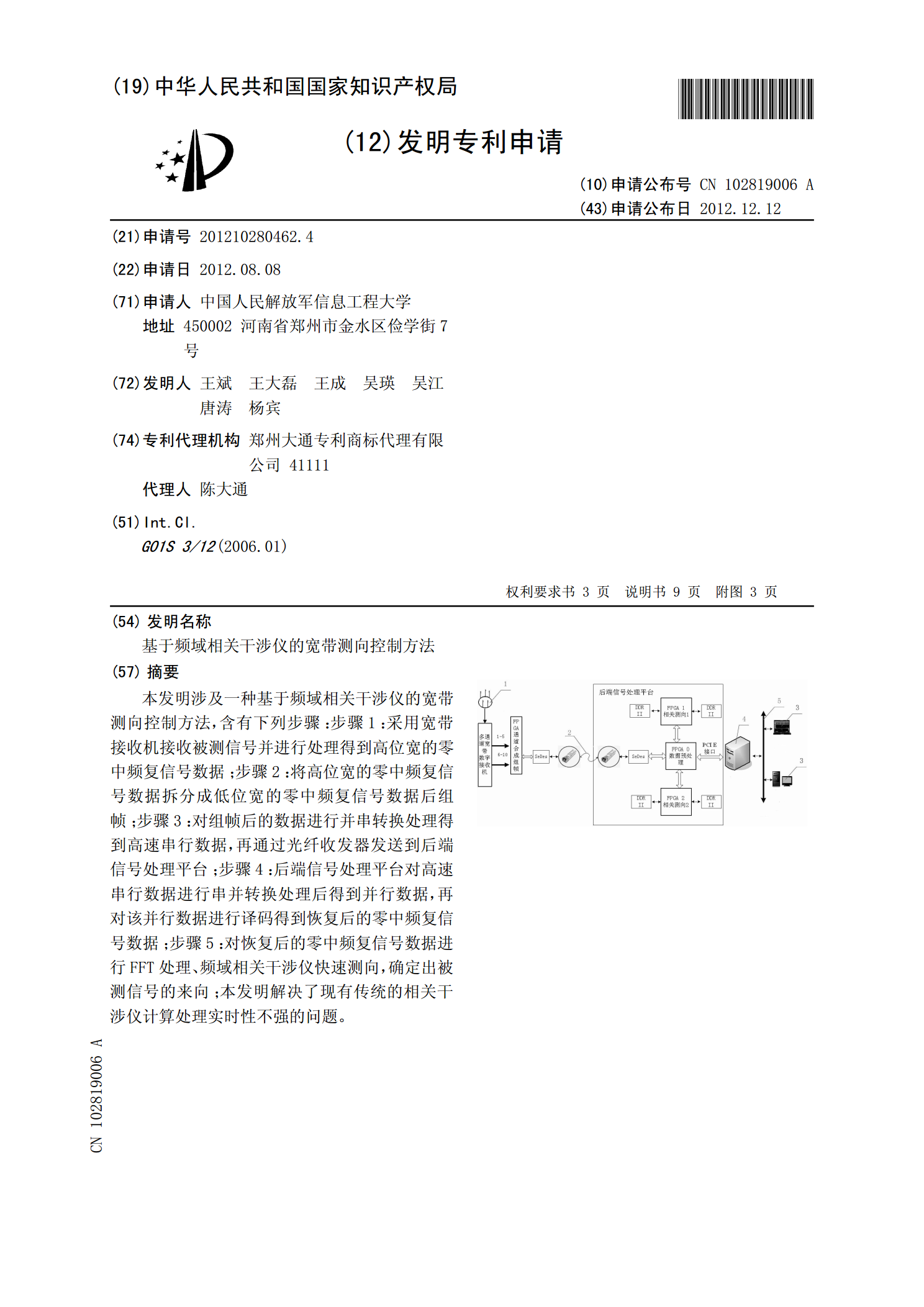

本发明涉及一种基于频域相关干涉仪的宽带测向控制方法,含有下列步骤:步骤1:采用宽带接收机接收被测信号并进行处理得到高位宽的零中频复信号数据;步骤2:将高位宽的零中频复信号数据拆分成低位宽的零中频复信号数据后组帧;步骤3:对组帧后的数据进行并串转换处理得到高速串行数据,再通过光纤收发器发送到后端信号处理平台;步骤4:后端信号处理平台对高速串行数据进行串并转换处理后得到并行数据,再对该并行数据进行译码得到恢复后的零中频复信号数据;步骤5:对恢复后的零中频复信号数据进行FFT处理、频域相关干涉仪快速测向,确定出

基于频域相关和SVM的宽带多信号测向方法研究.docx

基于频域相关和SVM的宽带多信号测向方法研究摘要:宽带多信号测向方法是无线通信领域中的一个重要研究方向。本文提出了一种基于频域相关和SVM的宽带多信号测向方法。首先,利用多通道频域相关分析将多个宽带信号转化为多个窄带信号。然后,采用支持向量机(SVM)分类器估算信号的起始方向。为了验证这种方法的有效性,我们使用模拟数据和真实数据进行了实验。实验结果表明,该方法具有较高的测向准确性和较好的鲁棒性。关键词:宽带多信号测向;频域相关;支持向量机;测向准确性;鲁棒性。引言:宽带多信号测向是一种重要的技术,可以在无

频域解模糊干涉仪测向方法.pptx

频域解模糊干涉仪测向方法目录频域解模糊干涉仪测向方法的原理频域解模糊干涉仪的基本原理频域解模糊干涉仪的信号处理过程频域解模糊干涉仪的测向精度和误差分析频域解模糊干涉仪测向方法的应用频域解模糊干涉仪在雷达测向中的应用频域解模糊干涉仪在声纳测向中的应用频域解模糊干涉仪在无线电测向中的应用频域解模糊干涉仪测向方法的优势和局限性频域解模糊干涉仪测向方法的优势频域解模糊干涉仪测向方法的局限性频域解模糊干涉仪测向方法的发展趋势和未来展望频域解模糊干涉仪测向方法的发展趋势频域解模糊干涉仪测向方法的未来展望感谢观看

基于神经网络的干涉仪测向方法.docx

基于神经网络的干涉仪测向方法基于神经网络的干涉仪测向方法摘要:干涉仪测向是无线通信领域中的一项重要技术,它可以根据接收到的信号相位差来确定信号源的方向。传统的干涉仪测向方法主要基于信号处理和参数估计的算法,但这些方法往往需要大量的计算资源和复杂的计算模型。随着神经网络的发展和应用,在干涉仪测向领域,神经网络方法也逐渐得到了广泛的应用。本文通过综述相关文献和研究成果,详细介绍了基于神经网络的干涉仪测向方法的原理、优势和应用。关键词:干涉仪测向、神经网络、信号处理、参数估计1.引言随着无线通信技术的快速发展,

一种基于干涉仪布阵的方位俯仰相关测向方法.docx

一种基于干涉仪布阵的方位俯仰相关测向方法摘要干涉仪是一种测量电击声波的优质仪器,其常用于地震学、地质学、天文学等领域中进行水平和垂直方向的测向。本论文研究了一种基于干涉仪布阵的方位俯仰相关测向方法,并在实验中进行了验证。该方法的优点为可精准测量目标物体在空间中的方位和俯仰角度,且具有较高的精度。关键词:干涉仪,测向方法,布阵,方位,俯仰角度引言干涉仪是一种测量电击声波的优质仪器。在地震学、地质学、天文学等领域中,常用于进行方位和俯仰相关测向。传统的测向方法主要通过多个干涉仪进行三点交通测向,但这种方法存在