IEEE1588时钟同步系统及其实现方法.pdf

一条****88

在线预览结束,喜欢就下载吧,查找使用更方便

相关资料

IEEE1588时钟同步系统及其实现方法.pdf

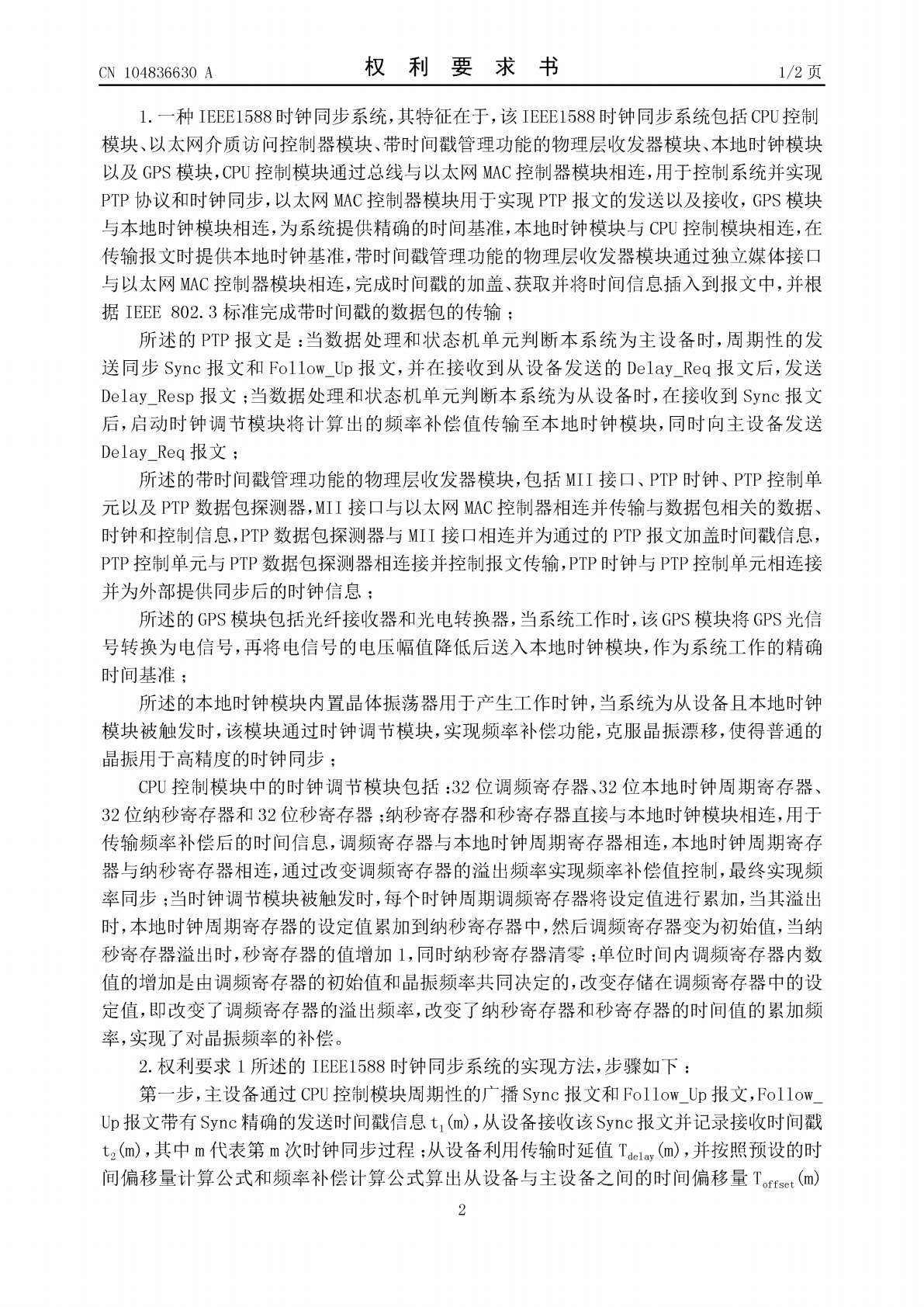

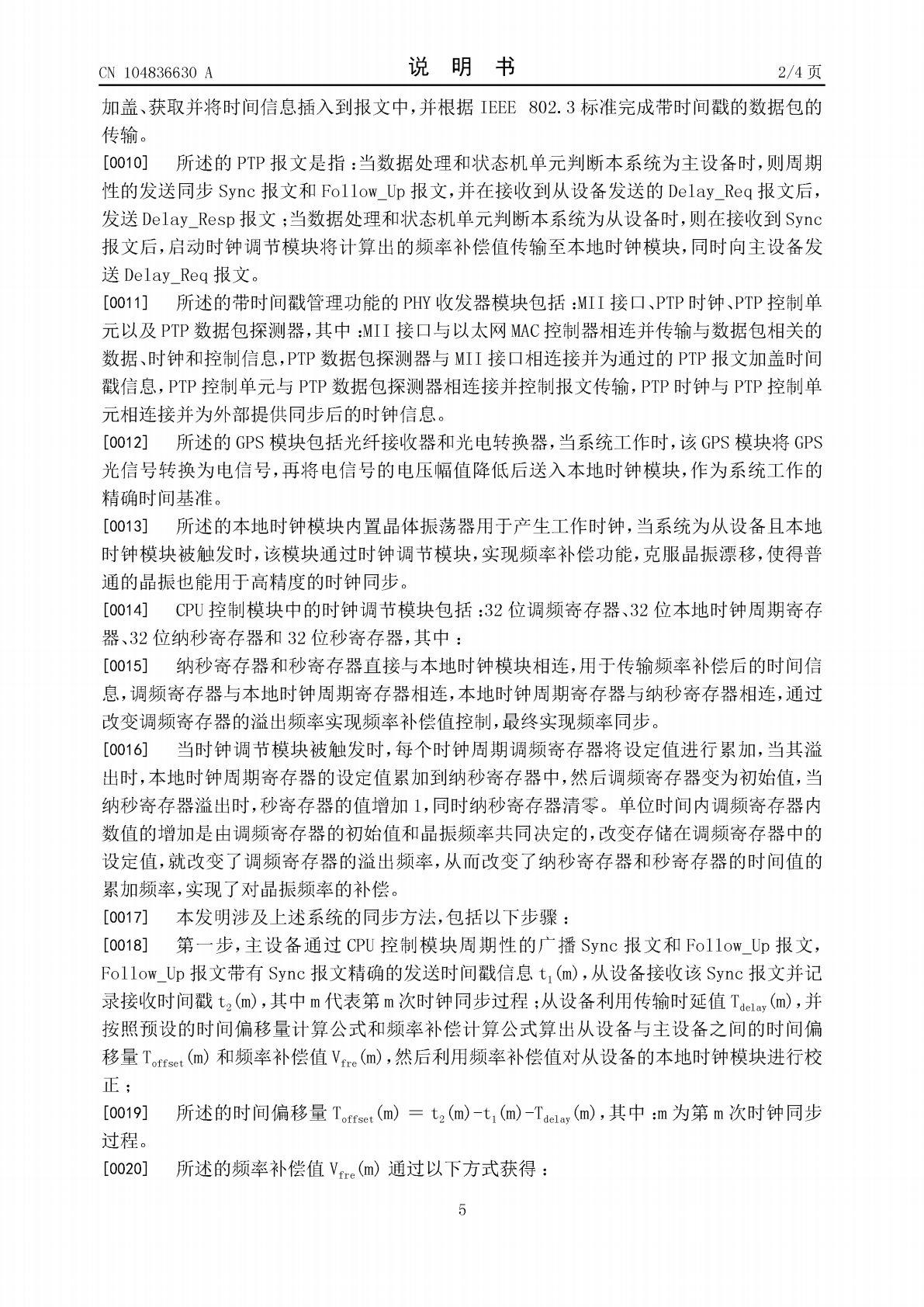

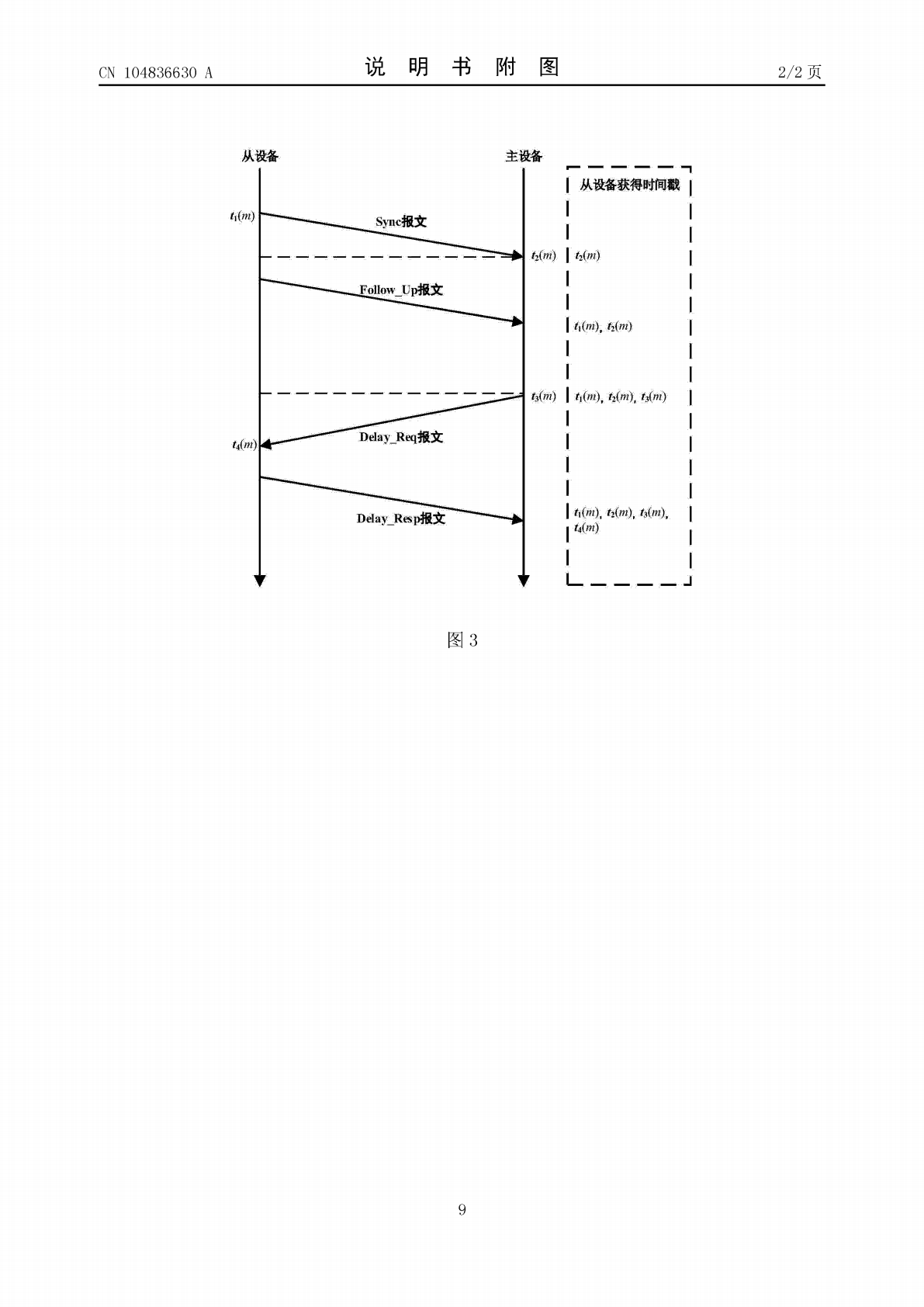

本发明属于网络信息传输技术领域,涉及IEEE1588时钟同步系统及其实现方法。CPU控制模块通过总线与以太网介质访问控制(MAC)控制器模块相连,用于控制所述系统并实现PTP协议和时钟同步,以太网MAC控制器模块用于实现PTP报文的发送以及接收,GPS模块与本地时钟模块相连,为系统提供精确的时间基准,本地时钟模块与CPU控制模块相连,在传输报文时提供本地时钟基准,带时间戳管理功能的物理层(PHY)收发器模块通过独立媒体接口与以太网MAC控制器模块相连,完成时间戳的加盖、获取并将时间信息插入到报文中,并根据

基于FPGA的IEEE1588时钟同步系统的实现的中期报告.docx

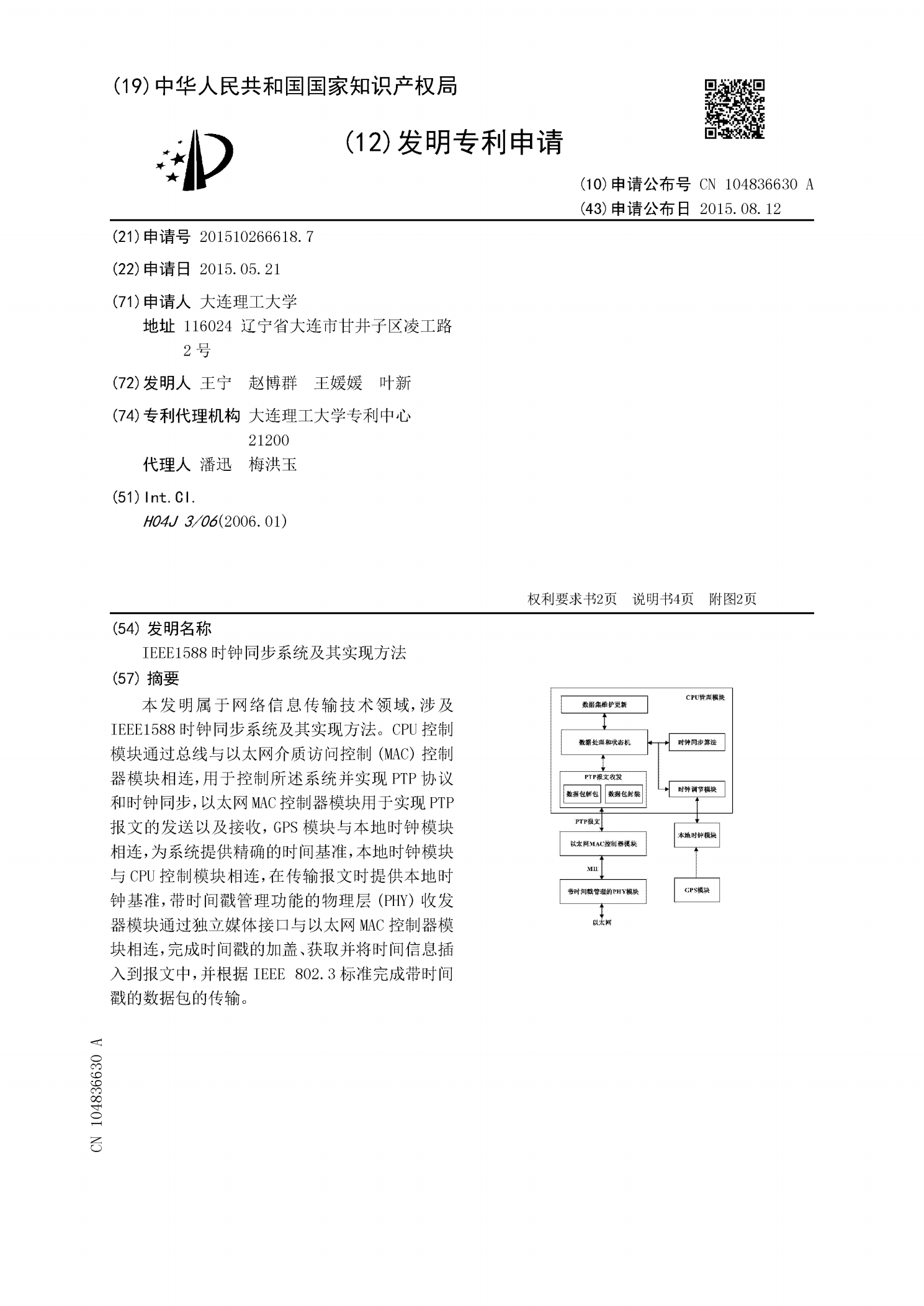

基于FPGA的IEEE1588时钟同步系统的实现的中期报告摘要:本项目旨在基于FPGA实现IEEE1588时钟同步系统,通过对传输链路上的同步标准进行实时校准,实现高精度、高可靠性的时钟同步。本文主要介绍了本项目的研究背景和相关技术,详细分析了时钟同步协议的通信原理、硬件架构以及实现方式。通过对时钟同步协议的模拟与实验,验证了该系统的可行性和性能,为后续系统的开发和升级提供了一定的参考与经验。关键词:FPGA、IEEE1588、时钟同步、硬件设计一、研究背景在现代化工业、交通等领域中,时钟同步是重要的通信

基于FPGA的IEEE1588时钟同步系统的实现的任务书.docx

基于FPGA的IEEE1588时钟同步系统的实现的任务书一、任务背景在计算机网络中,时钟同步是非常重要的一环。无论是开展计算机网络实时交互还是计算机网络的数据流同步,时钟同步都是计算机网络应用领域中不可或缺的功能。IEEE1588时钟同步协议是一种很好地实现网络时钟同步的协议,广泛应用于通信领域。FPGA技术在时钟同步领域也应用十分广泛。基于FPGA实现的IEEE1588时钟同步系统,因其性能优良、可靠性高、灵活性强等优点,也成为研究的热点。本文将着眼于基于FPGA的IEEE1588时钟同步系统的实现,探

一种时钟同步方法及其系统.pdf

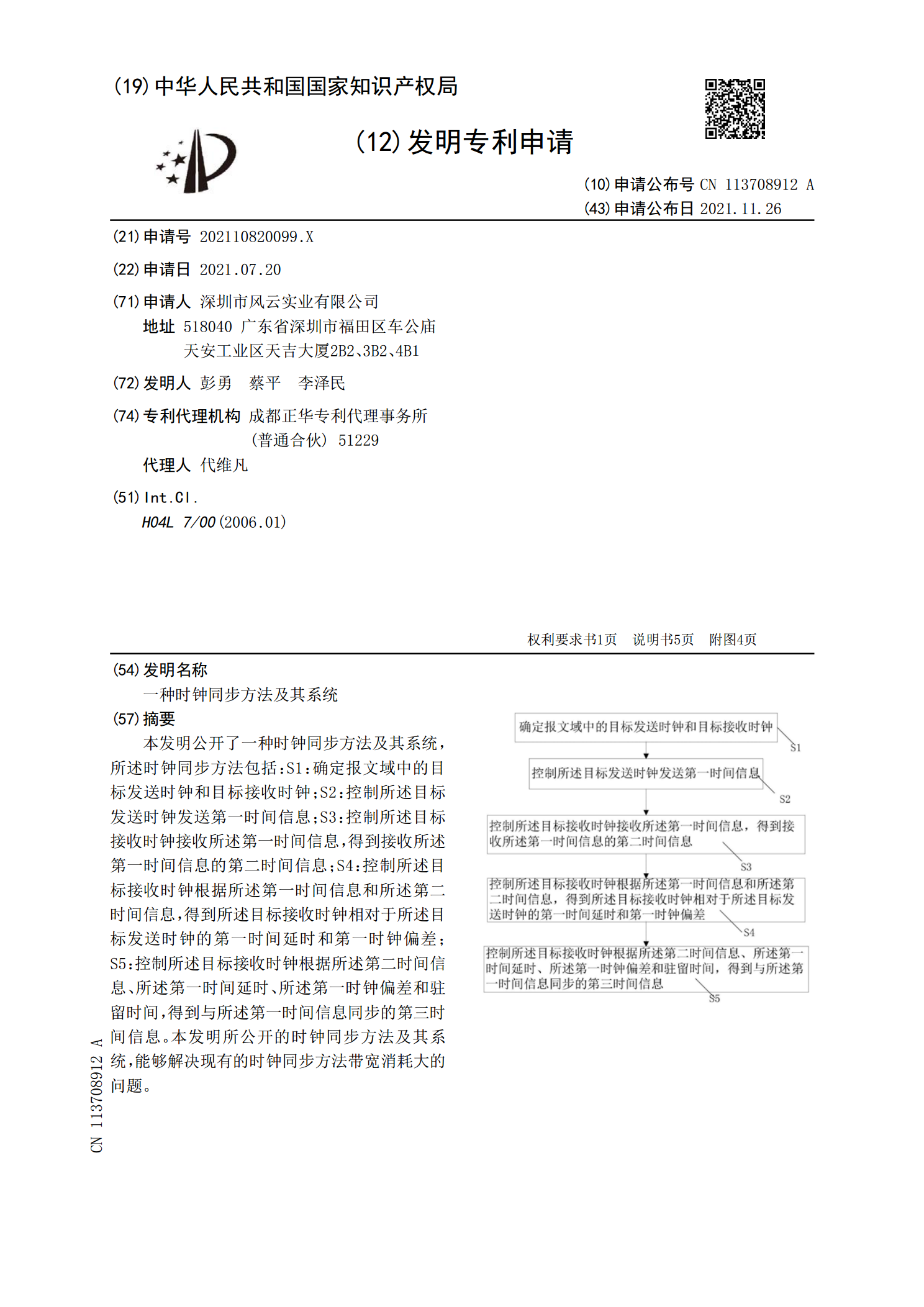

本发明公开了一种时钟同步方法及其系统,所述时钟同步方法包括:S1:确定报文域中的目标发送时钟和目标接收时钟;S2:控制所述目标发送时钟发送第一时间信息;S3:控制所述目标接收时钟接收所述第一时间信息,得到接收所述第一时间信息的第二时间信息;S4:控制所述目标接收时钟根据所述第一时间信息和所述第二时间信息,得到所述目标接收时钟相对于所述目标发送时钟的第一时间延时和第一时钟偏差;S5:控制所述目标接收时钟根据所述第二时间信息、所述第一时间延时、所述第一时钟偏差和驻留时间,得到与所述第一时间信息同步的第三时间信

IEEE1588精密时钟同步协议测试技术.docx

1引言以太网技术由于其开放性好、价格低廉和使用方便等特点,已经广泛应用于电信级别的网络中,以太网的数据传输速度也从早期的10M提高到100M,GE,10GE。40GE,100GE正式产品也将于2009年推出。以太网技术是“即插即用”的,也就是将以太网终端接到IP网络上就可以随时使用其提供的业务。但是,只有“同步的”的IP网络才是一个真正的电信级网络,才能够为IP网络传送各种实时业务与数据业务的多重播放业务提供保障。目前,电信级网络对时间同步要求十分严格,对于一个全国范围的IP网络来说,骨干网络时延一般要求