多通道串行总线高速数据采集处理系统及方法.pdf

是你****噩呀

在线预览结束,喜欢就下载吧,查找使用更方便

相关资料

多通道串行总线高速数据采集处理系统及方法.pdf

本发明涉及一种多通道串行总线高速数据采集处理系统及方法,涉及数据处理技术领域。本发明提出了一种基于微型CPU加FPGA和多种类串行收发器的高速串行通讯采集处理并存储的方案,能够满足电子系统在串行总线高速通讯时数据异常后问题排查分析和串行总线通讯监听存储的需求。

基于PCI总线的多通道图像数据高速采集.docx

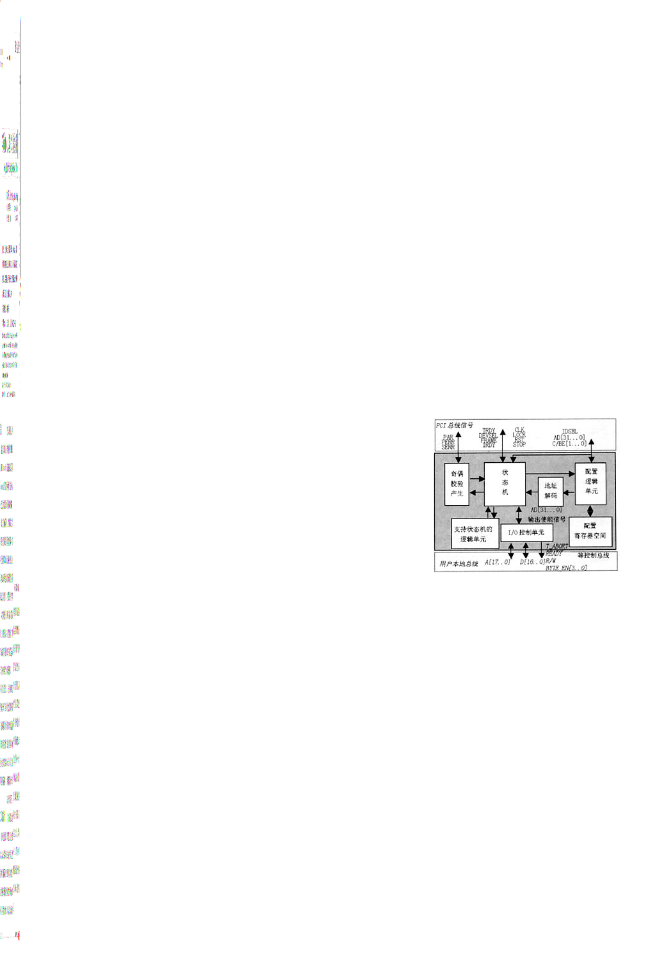

基于PCI总线的多通道图像数据高速采集摘要基于PCI总线的多通道图像数据高速采集,已成为图像处理领域中的一个重要问题。本文从硬件和软件两个角度进行分析,提出了一种基于PCI总线的多通道图像数据高速采集方案,该方案采用了多通道的数据采集模式,同时结合了硬件加速和软件优化的技术,对于接口的实现和传输的效率都有一定的提高。关键词:PCI总线,多通道,图像数据,高速采集,硬件加速,软件优化引言随着图像处理技术的快速发展,对于高速图像采集和传输的需求也越来越大。基于PCI总线的数据采集方案因其采集速度快、数据传输稳

多通道RXI总线数据采集系统设计.pdf

万方数据引言PXI总线接口模块设计随着自动测试技术的不断发展,基Instrumentation)总线的虚拟仪器测试系统已成为总线化自动测试系统的一个重要分支。在航空航天和其它测控领域,PXI总线测试系统的应用越来越广泛,因而研究自主化PXI接口,组建自定义的总线化测试系统成为自动测试领域备受瞩目的研究课题[1。⋯。本文针对航天测控领域提出的研制自主化PXI总线测试系统的要求,对PXI总线接口进行了深入研究,提出并实现了基于FPGA平台的自主化PXI总线接口设计方案;并针对导弹地面测试系统的具体要求实现了P

基于PCI总线多通道数据采集系统的设计.docx

基于PCI总线多通道数据采集系统的设计现代工业控制系统中,数据采集系统是重要的组成部分,它能够有效地提高生产效率和产品质量。而基于PCI总线多通道数据采集系统的设计则是实现高精度、高速数据采集系统的一种有效方式。PCI总线是PC机内部的一种通信总线,它可以实现高速、高带宽的数据传输。因此,基于PCI总线的多通道数据采集系统相比传统的数据采集系统具有更高的数据传输速度和更好的扩展性。在设计基于PCI总线的多通道数据采集系统时,需要考虑以下几个方面。1.硬件设计硬件设计是基于PCI总线的多通道数据采集系统设计

基于CAN总线的多通道数据采集系统设计.docx

基于CAN总线的多通道数据采集系统设计CAN总线是一种高可靠性的数据通信协议,广泛应用于车载电子设备、工业控制等领域。基于CAN总线的多通道数据采集系统能够实现对多个信号源的同时采集和传输,具有高精度、高可靠性和高效性的特点,是工业控制和汽车电子领域中不可或缺的设备之一。本文将对基于CAN总线的多通道数据采集系统进行探讨和研究。一、CAN总线的特点CAN总线是一种控制器局域网,具有广泛的应用场景。CAN总线的主要特点包括以下几个方面:1.高可靠性:CAN总线采用差分信号传输,可有效抑制干扰。此外,CAN总